近年來,視頻處理系統的研究受到了人們越來越多的關注,發展也非常迅速。同時,視頻技術也是一門跨越很多學科的技術,在此基礎上又衍生出了很多的新的技術和研究方向,比如人臉識別技術和圖像邊緣檢測算法的研究以及視頻壓縮算法的研究等。現在視頻處理系統有著廣泛的應用,比如交通路口的監控裝置、在機場、港口以及一些公共場所使用的視頻監控設備等。如果視頻技術再和圖像處理等技術結合起來,那么其應用的范圍和深度都會有很大的提高,比如在安防領域可以用于輔助識別危險目標和恐怖分子等,這些技術在民用領域和軍事領域都有著廣泛的應用。

針對以上這些應用需求,本文采用TI公司的DM642" title="TMS320DM642" target="_blank">TMS320DM642(以下簡稱DM642)數字多媒體處理芯片設計了一套視頻處理系統。文中主要介紹了系統的硬件設計和調試過程。

1 系統硬件設計方案

1.1 系統的硬件結構

視頻處理系統的硬件設計采用的DSP是DM642,它是一款高性能的數字多媒體處理器,最高運算速度可達5760MIPS(每秒百萬條指令),可以滿足復雜算法的實時處理要求。視頻信號需要通過CCD攝像頭采集。

視頻解碼芯片將采集到的模擬信號轉換為數字信號供DSP進行運算處理。DM642的視頻接口(VP口)共有3個,其中VP0和VP1都是20位,10位用于視頻輸入,另外10位用于音頻輸入。VP2口也是20位,可以分為兩路視頻輸入。在本文設計的視頻處理系統中,采集到的模擬視頻信號經過視頻解碼芯片模/數轉換后,形成BT.656格式的數字視頻信號,通過DM642的VP0口輸入。

數字信號經過DM642的軟件編碼器進行編碼壓縮處理,編碼壓縮生成的視頻碼流數據打包后通過RJ-45接口經以太網傳送到遠端的上位機,上位機作為SERVER,這樣就構成監控系統。通過DM642獨立多媒體接口(MII),片外連接一片以太網處理芯片,就可以構成10/100 Mbpa以太網模塊。本地回放由視頻編碼芯片來完成。

通過DM642的EMIF接口可以連接SDRAM和Flash存儲器。盡管DSP提供了片內RAM,但是在大多數情況下不能滿足系統的要求;同時對于要求實時處理的系統而言,又要求盡量減小在數據流動過程中由于存儲器讀寫造成的時間開銷,因此在系統中配置了高性能的SDRAM,它在運行程序和數據處理時使用。Flash在系統中主要是用來存放系統軟件和配置參數的。

系統的總體框圖如圖1所示。

在該視頻處理系統上集成了相當數量的板上設備以適應不同的應用環境,其主要特點為:

1)系統的運行頻率為600 MHzc。

2)2個視頻端口:1個為板上解碼器,1個為板上編碼器。

3)32 MB的同步DRAM空間。

4)2 MB的Flash空間。

5)以太網接口。

6)配有仿真器接口可以用來進行JTAG仿真。

7)供電電壓為+5 V。

8)蜂鳴器報警。

1.2 存儲器模塊設計

在數據處理模塊中,DSP芯片、SDRAM芯片和Flash芯片這3塊芯片是整個模塊電路的核心。該模塊的功能是完成與外部數據存儲器的數據傳輸和程序存儲器的程序讀寫任務。通過JTAG接口電路與仿真器相連后接到計算機主機進行仿真調試,實現與目標主機的數據交換。

1.2.1 SDRAM接口設計

在系統的硬件設計中,SDRAM內存芯片選用Micron公司生產的MT48LCAM3282-1Mx32×4 banks。SDRAM,即Synchronous DRAM(同步動態隨機存儲器),表明它的工作速度是和系統的總線速度同步的。MT48LC4M3282總線最高時鐘為166 MHz,它主要用來存儲數據和程序,SDRAM的刷新由DSP芯片自動控制。MT48LCAM3282是一款高速CMOS動態隨機存儲器,它內部配置為4個區的同步接口。

DM642的EMIF可以對SDRAM的地址屬性進行編程,它和SDRAM可以實現無縫連接。EMIFA最大的時鐘總線可達133 MHz。SDRAM控制器可以支持16 M~256 Mbit的SDRAM芯片。TMS320DM642上的Cache容量有限,所以視頻數據通常存放在片外SDRAM中,在需要用到的時候通過EDMA把數據從片外搬移到片內處理,這樣就可以提高程序的執行效率四。TMS320DM642的SDRAM接口圖如圖2所示。

由于TMS320DM642的數據總線是64位,而每片MT48LC4M3282的數據總線是32位,所以需要并聯兩片MT48LC4M3282才能構成64位的數據總線,這樣才可以與TMS320DM642的EMW數據總線相連。參照DM642數據手冊中SDRAM的配置方法,EA15、EA16控制SDRAM的組,EA3-EA14控制行地址,EA3-EA11控制列地址,片選信號接到DM642的![]() 上,這樣就把SDRAM分配到CE0空間上。

上,這樣就把SDRAM分配到CE0空間上。

1.2.2 Flash接口設計

DM642 EMIFA的異步接口為各種存儲器和外設類型提供了可配置的存儲器周期類型,包括SRAM、EPROM、Flash等,在本系統中Flash采用的是SST公司生產的SST39VF1601 Flash,片選信號接到DM642的![]() 引腳上。當DSP上電后,DSP通過增強的直接存儲器訪問從外部的CE1尋址空間復制1 K字節的數據傳給內部存儲空間,然后再從內部存儲空間0x0處開始運行,所以Flash ROM必須配置在DSP的CE1空間,在DSP存儲器中對應的地址是0x90000000-0x90200000。

引腳上。當DSP上電后,DSP通過增強的直接存儲器訪問從外部的CE1尋址空間復制1 K字節的數據傳給內部存儲空間,然后再從內部存儲空間0x0處開始運行,所以Flash ROM必須配置在DSP的CE1空間,在DSP存儲器中對應的地址是0x90000000-0x90200000。

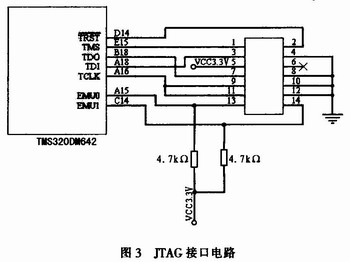

1.3 JTAG接口設計

JTAG接口是調試環境和目標板之間的接口,它的好處是可以讓開發者在對目標板進行開發的同時可以不改變目標板的系統結構,從而方便了系統的開發與測試。XDS510仿真器通過JTAG接口將系統板與電腦連接起來,這樣就可以使用TI提供的集成化開發環境對系統進行調試了。JTAG接口采用標準的雙排14腳插座。系統的JTAG接口電路如圖3所示。

1.4 電源模塊設計

DM642需要兩種電源,一種是內核電源(1.4 V),另一種是I/O電源(3.3 V)。通常由于DM642用于嵌入式系統中,因此電源電路設計不僅要考慮電壓精度、穩定度和外圍電路的復雜度等問題,還要考慮低功耗問題。另外,根據設計要求,為了保證芯片正常工作,在系統上電作時,對這兩種電源的上電順序還有一定的要求,如果違反該要求,可能降低器件的性能或永久損壞器件。內核電源要比I/O電源早上電,至少不能晚于I/O電源上電。在電路設計中,通過采用在兩個電源之間串聯二極管的方法來解決系統上電順序的問題。

系統設計中,電源芯片采用的是TI公司的TPS54310,它是TI公司生產的一款開關電源調節芯片,它能夠實現低電壓輸入和高電流輸出(輸人電壓范圍為3~6 V,輸出電壓根據需要可以在0.9~3.3 V之間調節,輸出電流為3 A)。圖4是3.3 V電源產生電路,1.4 V電源產生電路與此類似,只需根據TPS54310中的計算公式將相應的電阻和電容值做相應的修改就可以得到1.4 V電源。3.3V的電源不僅是DM642的0電源,同時也是系統上視頻解碼芯片、視頻編碼芯片、SDRAM芯片等的供給電源。

1.5 視頻輸入輸出模塊設計

1.5.1 視頻輸入模塊設計

視頻輸入模塊設計采用的視頻解碼芯片是TVP5150APBS,它是TI公司專門開發的一款可以方便攜帶的低功耗視頻解碼芯片,可以廣泛用于視頻系統的設計。TVP5150APBS的視頻輸入端可以輸入兩路復合視頻信號或者一路S端子信號。輸入信號(如PAL、NTSC等制式)通過增益控制單元、模數轉換器和Y/C分離及處理模塊后,最后可以轉化為8位ITU-R BT.656的數據格式,或者轉化為8位4:2:2的數據格式。TVP5150A-PBS的初始化操作是通過操作IIC總線來實現的。TVP5150APBS的IIC地址可以通過控制12CSEL引腳的高低電平來設置。當該引腳是低電平時,IIC地址是0xB8h,當該引腳是高電平時,IIC地址則為0xBAh。TVP5150APBS與TMS320DM642的連接示意如圖5所示。

從圖5可知,視頻信號可從TVP5150APBS的AIP1A或AIPIB輸入,數據輸出引腳YOUT[0:7]與DM642的VP0[2:9]引腳連接在一起。TVP5150-APBS的系統時鐘引腳SCLK與DM642的VPOCLK0引腳連接。因為在本系統的設計中采用的是ITU-R BT.656的視頻輸出格式,所以在系統中不需要分立的同步信號。因此,TVP5150APBS的HSYNC(行同步信號)、VSYNC(場同步信號)、AVID(行消隱指示信號)以及FIDFig.5 Colleetion bet-ween TVP5150APB5 and DM642(奇偶場指示信號)這幾個引腳并不需要與TMS320DM642連接, 只需要將TVP5150APBS的INTERQ引腳與TMS320DM-642的VPOCTL0引腳連接起來。

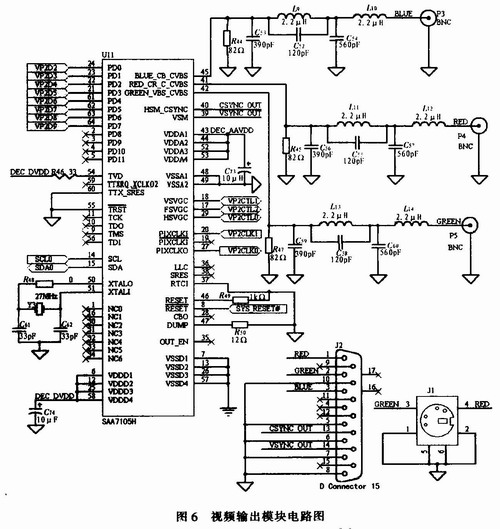

1.5.2 視頻輸出模塊設計

在系統設計中,視頻輸出模塊中的視頻編碼芯片選用的是Philips公司的SAA7105H,它同時具有SDTV(標準清晰度電視)和HDTV(高清晰度電視)信號編碼能力,可以廣泛用于視頻輸出的設計中。視頻輸出模塊的電路如圖6所示。

從圖6中可知,將DM642的VP2端口配置成視頻輸出端口。由于VP2端口的數據線與SAA710SH的數據線相互錯位,因此這會造成無法正常顯示視頻輸出。為了解決這個問題,在將VP2端口配置成ITU-R BT.656視頻輸出時,數據就會從VP2 A通道的VPD02-VP2D09輸出,VP2D00-VP2D 01則輸出無效,因此就需要將VP2D02-VP2D09這8根數據線連接到SAA7105H的PD0-PD7對應的引腳。這樣VP2D10-VP2D19在視頻回放中就沒有使用。

SAA7105H將從DM642端傳送來的PC信號轉化為PAL制式(50 Hz)或者是NISC制式(60 Hz)送到外部TV端輸出。SAA7105H默認為休眠狀態,在休眠過程中HC總線仍然可以接受來自DM642的命令。當SAA7105H的3個數模轉換器視頻輸出與外部TV相連接時,SAA7105H能夠自動檢測到數模轉換器接口的阻抗變化,然后通過芯片的TVD(電視信號檢測)引腳向TMS320DM642發出中斷請求,表明外部有播放要求。此時,DM642就會通過IIC總線來配置SAA7105H的內部寄存器,激活還處于休眠狀態的SAA7105H,開始進行本地視頻的播放。

在視頻輸出模塊中,SAA7105H的HSVGC(水平同步輸出)、VSVGC(垂直同步輸出)、FSVGC(幀同步輸出)分別于TMS320DM642端口的VP2CTL0、VF2CTL1以及VP2CTL2這3個引腳相連。SAA7105H的輸出方式可以有RGB格式、CVBS(混合視頻)格式、S-Video格式以及VGA格式等幾種。其輸出方式的選擇通過SAA7105H的應用子地址來控制。

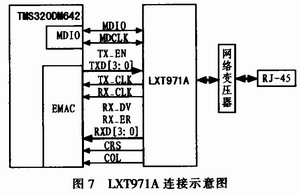

1.6 以太網接口設計

以太網接口設計中的以太網處理芯片采用Intel公司的LXT97lA,它符合IEEE標準,直接支持10 Mbps和100Mbps的雙絞線應用,也可以支持100 Mbps的光纖接口。LXT971A與DM642的連接示意圖如圖7所示,在以太網模塊中還需要用到網絡變壓器和RJ-45以太網連接器。

1.7 報警電路設計

系統的報警電路結構比較簡單,它由驅動電路與蜂鳴器構成,驅動電路與DSP的一個GPIO引腳連在一起,電路如圖8所示。

從圖8中可以看出,當GP10輸出高電平(通知報警)時,三極管的集電極和發射極之間將視為短接,從而驅動蜂鳴器發聲報警,系統設計中采用的是有源蜂鳴器來進行報警。

2 系統調試

2.1 Flash的調試

Flash調試的步驟如下:

1)配置寄存器,Flash的基地址是0x90000000,共有512個扇區,每個扇區有4 K字節,Flash的大小為2M字節。將Flash的空間映射到TMS320D-M642的存儲器空間內;

2)進行Flash的擦除操作;

3)判斷擦除操作是否結束。Flash的DQ6位和DQ7位都可以用來判斷擦除是否結束,這里采用的是DQ7位。在內部擦除操作過程中,讀出的DQ7的值是“0”,一旦內部擦除操作完成,DQ7的值就會變化為“1”;

4)開始Flash的寫操作和讀操作。

可以通過CCS的Memory窗口可以觀察Flash的寫入是否正確。讀出的數據和寫入的數據經過對比后無誤,說明系統的Flash工作正常。

2.2 SDRAM的調試

兩塊SDRAM芯片MT48LC4M3282的片選信號是與TMS320DM642的![]() 引腳接在一起的,因此SDRAM的基地址是Ox800000000。在測試SDRAM時,從SDRAM的基地址開始,長度為32 M字節。在編程時向SDRAM中寫入數據。然后再讀出數據,將讀出的數據與寫入的數據進行對比,測試后對比無誤,說明系統的SDRAM工作是正常的。

引腳接在一起的,因此SDRAM的基地址是Ox800000000。在測試SDRAM時,從SDRAM的基地址開始,長度為32 M字節。在編程時向SDRAM中寫入數據。然后再讀出數據,將讀出的數據與寫入的數據進行對比,測試后對比無誤,說明系統的SDRAM工作是正常的。

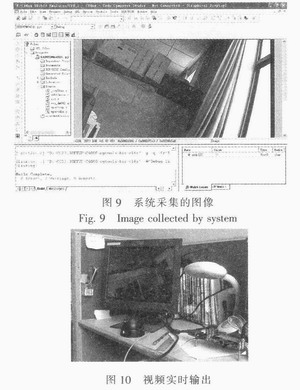

2.3 靜態圖像的采集

在圖像采集中用到的是TMS320DM642的VP0口,需要一個CCD攝像頭。采集到的靜態圖像通過CCS的View功能來顯示。

視頻解碼芯片TVP5150APBS的IIC地址設置為0xB8。另外,在程序中還需要對TVP5150APBS相關的寄存器進行必要的設置以滿足系統的要求。編寫圖像采集程序,TVP5150APBS能夠實時采集圖像。程序在CCS中經過編譯、運行后采集到的圖像如圖9所示。

2.4 視頻顯示的調試

視頻顯示模塊主要是在圖像采集的基礎上實現VGA制式視頻圖像的實時顯示。在調試過程中需要編寫視頻接口的顯示驅動程序以及整個視頻顯示通道的調試程序,還需要對視頻編碼芯片SAA7105H的寄存器進行設置。視頻輸出信號通過VGA接口連接到顯示器上,這里采用的是電腦顯示器。調試程序經過編譯、運行后,會將TVP5150APBS采集到的圖像通過SAA7105H送到顯示器實時顯示出來,如圖10所示。

2.5 報警模塊的調試

在調試時通過編程將GP10引腳設置為“1”,即給報警電路輸入一個報警信號,此時蜂鳴器將會發聲報警。

2.6 以太網模塊的調試

以太網模塊的調試主要是測試EMAC與MDIO的配置及使用,以及如何配置一個PHY設備和CSL庫中關于網絡接口部分程序的應用。在調試過程中,是采用自閉環的方式來完成的。

將系統板上的RJ-45網絡接口用網線和局域網連在一起,在調試中需要用到TI推出的TCP/IP NDK(Network Developer's Kit)開發套件中提供的調試程序。程序運行后,系統板可以和局域網中的電腦正確地進行數據傳輸,說明系統的以太網模塊是可以正常工作的。

3 結束語

系統研究并實現了一個通用的基于DM642的視頻處理系統。該系統已經調試成功,它可以完成視頻信號的輸入與輸出,可以應用于視頻圖象采集和處理的各種場合中。系統還擴展了一個網口,可以方便地與外界通信。與傳統的視頻處理系統相比,該系統在視頻輸出方式上更趨多樣化,視頻輸出接口既可以接到電視機上,也可以與PC機的顯示器相連接,彌補了以往接口單一的缺陷。系統新增的報警功能增強了系統的實用性。下一步研究的方向是對該系統做進一步的完善,比如可以增加USB接口,擴展系統的應用范圍,將蜂鳴器報警改為語音報警等。最后,在此系統上研究各種算法,比如視頻壓縮算法、圖像處理算法等,這樣它可以應用于視頻會議、交通、監控等諸多領域,具有廣泛的應用前景。