摘要:目前數字相機逐步取代模擬相機應用在光電測量設備中,因此圖像處理器" title="圖像處理器">圖像處理器也逐漸轉化為接收數字視頻的接口,對數字圖像處理器檢測的信號發生器" title="信號發生器">信號發生器的研制也變得十分迫切。本文介紹了一種基于FPGA的兩種數字視頻格式輸出的視頻發生器,它可以產生LVDS制式的數字視頻信號和CamerLink制式的數字視頻信號,而且可以通過串口對產生的視頻中的目標大小、運動速度、灰度及背景灰度進行實時更改。它滿足了對數字視頻輸入的圖像處理平臺" title="圖像處理平臺">圖像處理平臺的檢測,具有一定應用前景。

關鍵詞:現場可編程門陣列;視頻發生器;LVDS;圖像處理平臺

0 引言

在光電測量系統中,需要圖像處理器進行圖像采集、處理。而為了對圖像處理器的圖像采集能力及處理能力進行評估、檢測,常常需要對圖像處理器輸入特定視頻,進行各項功能測試。目前隨著數字化相機的廣泛應用,圖像處理器多采用數字化接口。而且對圖像處理器的檢測要求信號發生器產生的視頻內容越來越豐富,幀頻越來越高,而目前檢測圖像處理器的信號發生器多是標準的模擬視頻輸出,如文獻提出的模擬視頻發生器,有的雖然能產生數字視頻但內容是固定的,如果對內容進行更改則需要對數字視頻信號發生器重新編程以達到要求,比較麻煩,不能滿足日益復雜的要求。因此靈活改變視頻內容的數字視頻信號發生器的研制變得十分迫切。本文提出一種數字視頻信號發生器的設計方法,此方法可以同時得到LVDS和CamerLink制式的視頻,供數字化圖像處理器檢測使用。本文提出的設計方法除可以脫離計算機獨立使用外,如果想實時更改信號發生器輸出視頻的各項參數,無需重新改寫程序,只需把該信號發生器通過串口連接到計算機上,即可通過人機交互的方式對視頻中的目標灰度、背景灰度,目標大小、目標運動速度進行更改。此外目標的背景還可以從板卡上的SDRAM中選取。與以往的視頻信號發生器相比,本文提出的信號發生器除能產生多種數字化視頻外,還能靈活更改所產生的視頻各項參數,因此具有一定應用價值。

1 硬件組成

數字視頻發生器主要卣FPGA模塊、單片機模塊、串行通信模塊" title="通信模塊">通信模塊、TTL轉L,VDS模塊、FTL轉CamerL,ink模塊、SDRAM模塊組成,整個系統框圖如圖1所示。

1.1 工作原理

數字式視頻信號主要由行同步、幀同步、像素時鐘、圖像數據" title="圖像數據">圖像數據組成。其中行同步決定一行的起始位置,幀同步決定一幀圖像的起始位置,像素時鐘決定一行有多少列圖像數據。根據數字圖像的組成,可以看出如果想要生成一幅數字圖像,必須包含上述要素。其行幀信號同圖像的關系如圖2所示,其中VSYN表示幀同步信號,HSYN表示行同步信號。

其中圖像的采集是從行同步上升沿開始后,按像素時鐘采集的。

本文根據數字視頻產生所需的各要素進行信號發生器的設計。主要通過FPGA產生行同步信號、幀同步信號、像素時鐘;通過單片機+串口通信模塊實現目標參數的更改,并把更改后的參數傳遞給FPGA,供FPGA產生相應運動的視頻信號;通過視頻制式轉換模塊把FPGA生成的視頻數據及視頻控制信號轉換成LVDS和CamerLink制式的數字視頻信號。

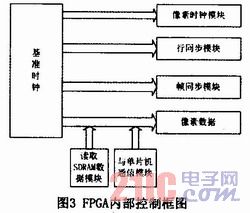

2 FPGA控制模塊

FPGA具有高集成度、高可靠性以及開發工具智能化等特點,目前逐步成為復雜數字電路設計的理想首選。此外FPGA可以通過編程實現硬件的邏輯功能,大大減少了硬件設計的復雜程度。因此本文以FPGA為核心器件產生視頻信號,這里選用ALTERA公司的SycloncII系列的EP2C8 F25618N,采用VHDL語言編程生成與數字視頻有關的各個信號,與單片機通信接收視頻修改參數的模塊及得到SDRAM內部圖像的模塊。其結構框圖如圖3所示。

信號發生器上電后,FPGA通過與單片機通信的模塊得到初始視頻各項參數,根據參數進行目標大小、目標灰度、目標運動速度、背景灰度的設置,然后根據各項設置產生視頻數據,FPGA幀同步模塊、行同步模塊、像素時鐘模塊分別產生幀同步、行同步、像素時鐘,圖像數據按以上控制信號從FPGA中發送出去。

在本文中FPGA各功能模塊根據基準時鐘生成幀同步、行同步、像素時鐘。這里以50M時鐘為基準時鐘信號,根據圖像處理平臺對輸入信號的要求,設計的幀同步高電平占33ms,低電平占1.2ms,行同步高電平占35 μm,低電平占8.4μm。這里把50M基準時鐘輸入像素時鐘模塊經過鎖相后依然以50M的時鐘頻率輸出,作為像素時鐘。由于一行較多,可在程序中進行限位,控制每行像素數。像素的產生主要有兩種方式,一種是通過與單片機通信得到目標像素灰度及背景像素灰度,根據這兩種灰度產生像素數據。另一種方式是通過從連接在FPGA上的SDRAM內讀出圖像作為背景,從與單片機通信得到目標灰度,共同形成像素數據。

2.1 單片機控制模塊及通信模塊

在本設計中單片機作為通信管理芯片。它主要實現與計算機的通信,更改信號發生器所產生信號的各個參數,把各個參數經過整合送給FPGA,以便FPGA根據參數控制目標的運動速度、目標大小、目標灰度及背景灰度。為了保證信號發生器能夠方便地和計算連接,實現人機交互,實時更改產生的視頻信號,并且從通信穩定可靠出發,這里采用RS232通信接口。但是因為計算機每次發的數據較多,這里沒有直接應用電平轉換芯片把計算機和單片機的串口連在一起,而是通過一片16C650把電平轉換芯片和單片機連在一起,這樣的好處在于16C650內部具有32字節的FIFO,可起到數據緩存的作用,使單片機能夠穩定可靠地接收數據。

2.2 視頻制式轉換模塊

因為FPGA產生的視頻信號為TTL電平,而目前數字視頻信號以LVDS制式和CamerLink制式為主,因此需要進行電平轉換。這里主要采用把FPGA產生的TTL電平的數字視頻信號接入SN75LVDS387得到LVDS制式的視頻信號,同時可把該TTL數字信號接入DS90CR285得到CamerLink制式信號。

3 軟件設計

本文軟件設計主要對單片機和FPGA進行編程。其中對單片機編程主要應用C語言進行編程,對FPGA主要應用VHDL語言編寫。其中單片機程序框圖如圖4所示。FPGA程序流程框圖如圖5所示。

4 結論

本文介紹了一種基于FPGA的數字視頻信號發生器,此發生器能夠同時產生CamerLink和LVDS制式的視頻信號,同時此視頻信號發生器可通過人機對話的方式對所產生的視頻信號中的目標、背景灰度、目標大小、運動速度等參數實時更改,從而達到檢測圖像處理平臺目標分辨能力、目標捕獲能力、目標捕獲目標跟蹤速度、目標跟蹤精度等指標的目的。因此具有一定應用價值。