引言

在巨大的市場壓力之下,高功率無線電設計似乎顯得比以往任何時候都更具成本效益。其中,最重要組成部分便是發射機效率。簡單看一下功率放大器(PA)的傳遞函數,就會發現線性度與電源效率之間存在根本的對立關系。在飽和狀態下工作時,PA晶體管的電源效率最高,但線性度不佳。非線性會使頻譜擴展到信號帶寬以外,從而干擾相鄰通道,降低鄰道泄漏比(ACLR)性能。在信號帶寬內,放大器非線性也會導致失真增加,從而降低接收機的誤差矢量幅度(EVM)性能,使誤碼率(BER)增大。

為了滿足空中接口的線性度和頻譜要求,降低功率放大器的輸入信號電平,使其在傳遞曲線的線性部分工作,但這會導致電源效率不佳。這種方法雖然簡單,但會增加系統成本;為了實現所需的功率輸出,必須使用更大、更昂貴的PA。在典型的3G移動基站收發臺(BTS)中,發射效率低于10%,這意味著90%以上的直流功率轉化成了熱量而沒有得到利用。

1 數字預失真技術

對于這個兩難問題,更具成本效益的解決方案是采用設計巧妙的DSP。利用數字預失真(DPD)這種技術,可以通過使發射信號預失真來滿足頻譜要求,同時讓工作在高效率飽和區的PA晶體管有效線性化。DPD需要一個觀測接收機,通過其中的高帶寬ADC,對PA輸出的耦合版本進行下變頻處理。發射波形的數字版本與接收波形相比較,由自適應算法計算或更新一系列參數,以便預加載下一個發射波形。當自適應算法收斂時,即使PA工作在傳遞函數的高度非線性部分,發射機輸出也實現了線性化。DPD可將發射機效率從10%以下提高到35%以上,具體取決于所用的算法和功率放大器拓撲結構。

包含DPD等復雜閉環算法的無線電系統設計不能孤立地進行。針對信號鏈的模擬行為和PA的電氣與熱記憶效應進行建模也不是一件容易的事。失真機制的數量會隨著非線性階數的提高而迅速增加,這意味著PA的輸入驅動電平可能會顯著改變失真行為。一款完整的閉環估算平臺對于優化給定PA的DPD算法可謂無價之寶。

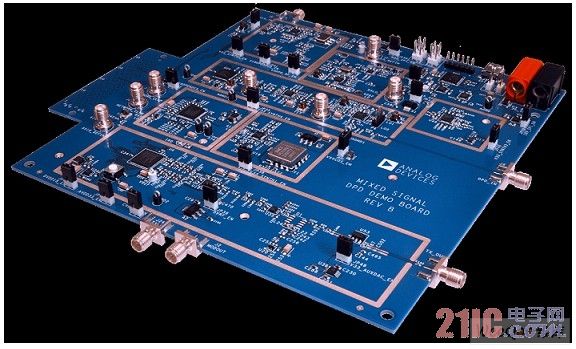

ADI公司已開發出3G/4G兼容發射無線電平臺,支持無線基礎設施設備的設計人員利用功率放大器和數字預失真技術估算閉環性能結果。這款混合信號數字預失真平臺(MSDPD)如圖1所示,它將高性能線性和混合信號器件組合成先進的發射機和DPD觀測接收機。

圖1:混合信號數字預失真(MSDPD)開發板

2 DPD平臺的FPGA優勢

當今許多DPD用戶使用的解決方案要么基于固定功能ASIC,要么基于FPGA。FPGA具有可編程能力,因此用戶能夠靈活地優化解決方案,并能夠適應數據轉換器和功率晶體管技術的未來發展。固定功能ASIC則不允許設計人員輕易改變算法或支持不同版本的標準。可編程器件的好處是可以加速產品上市,靈活且經濟有效地適應新標準和發展中的標準,而不必像ASIC那樣需要重新設計。

隨著FPGA技術的進步,現在使用一個FPGA器件就能實現整個無線電調制解調器,并支持多種標準和多天線,因此可以省去許多信號處理和連接IC,電路板空間得以縮小,BOM成本得以降低。此外,這種集成度讓業界離軟件無線電(SDR)又近了一步,有助于設備制造商快速響應網絡提供商的需求。

MSDPD開發平臺是市場上僅有的一款為無線基礎設施設備的設計人員提供FPGA功能的解決方案。MSDPD板能夠與多種FPGA開發套件無縫連接:通過HSMC接口使用Altera Stratix IV,以及通過FMC接口使用Xilinx Virtex 6。直接與FPGA接口為設計人員提供了一個即時便捷框架,可以快速估算第三方DPD算法,或者通過簡單的FPGA重新編程,在一個閉環環境中設計并優化自己的算法。

3 DPD平臺的架構

MSDPD板的發射鏈和觀測接收路徑均提供同類最佳的性能。無線電采用寬帶設計,可在裝配時進行配置,以支持800MHz至2.7GHz的RF頻段。目前支持125MHz的發射帶寬。根據所用的DPD方法,校正后的發射帶寬在20MHz至40MHz之間。

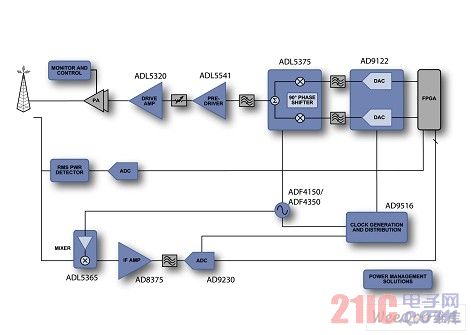

MSDPD板的輸入包括FPGA的基帶數字數據、參考時鐘、觀測到的RF輸出和功率。其輸出包括所需RF載波中心頻率的RF預放大輸出和發射機輸出的IF采樣版本。該板設計為可與外部PA和RF耦合網絡一起工作。MSDPD上使用的發射機和觀測接收機信號鏈如圖2所示

圖2:MSDPD發射與觀測路徑框圖

4 ZIF/CIF發射機

MSDPD板利用16位1.2GSPS雙通道DAC對來自數字處理器的基帶I和Q數據進行采樣,然后調制到所需的RF輸出頻率并放大,產生最高+19dBm的峰值輸出功率,這樣就能傳送到外部PA進行發射。MSDPD板支持零中頻(ZIF)和復中頻(CIF)兩種發射架構。

DAC選用1.2GSPS 16位雙通道DAC AD9122,它具有同類最佳的性能,可滿足MC-GSM 1類要求。高輸入LVDS數據速率支持第一代MSDPD平臺的200MHz輸入帶寬。AD9122的片內32位NCO(數字控制振蕩器)支持以小于1Hz的步長靈活地產生IF頻率,有助于設計人員滿足信道柵要求。如果沒有NCO,則需要使用RF PLL中的分頻器,這種方法可能會降低雜散性能。片內還集成了數字增益、相位和失調補償功能,幫助減少LO饋通及模擬正交調制器引入的無用邊帶,從而將RF濾波要求降至最低。

雙通道DAC后接一個五階低通濾波器,用以消除無用的DAC鏡像或時鐘相關雜散。濾波器截止頻率按照高要求設計,以便在整個發射帶寬內保持平坦的頻率響應和低群延遲變化。濾波之后,ADL5375正交調制器將模擬IF上變頻為最終RF,選擇ADL5375的原因是它具有寬頻帶和極低的噪底(-159dBm/Hz)。ADL5375支持禁用功能,在TDD突發脈沖的Rx部分,可以禁用輸出。

發射路徑的本振(LO)利用ADF4150 PLL和外部VCO在片上產生,以提供出色的相位噪聲性能。復中頻發射架構還有一個好處,因為觀測接收機采用高中頻采樣架構,所以發射和觀測接收路徑可以共用LO。

正交調制器之后是RF放大鏈。由于PA的增益會隨著頻率和溫度變化而改變,因此需要某種模擬增益控制來均衡發射機。為使SNR降幅最小并實現最佳OIP3(輸出三階交調點)性能,建議大部增益范圍調整在各放大級之間進行。ADL5541 15dB固定增益模塊后接一個PIN二極管衰減器,用于模擬增益控制。固定增益模塊的線性度和噪聲性能通常優于VGA(可變增益放大器)。預驅動器寬帶放大器ADL5320是MSDPD板RF放大鏈的最后一個器件,提供13dB的額外增益和42dBm的OIP3,2.1GHz時的噪聲系數(NF)為4.5dB。級聯RF放大鏈提供22dB的增益,最大增益下的OP1dB為24dBm,OIP3為41dBm。

整個DPD帶寬內的通帶平坦度和群延遲變化也是發射機的重要特性參數。數字算法會嘗試均衡上變頻器的頻率響應。這將直接影響發射機的動態范圍,其降幅為整個通帶內的紋波或衰減量。MSDPD板發射路徑的濾波器設計經過優化,整個帶寬內的通帶平坦度小于1dB,群延遲變化小于0.5ns。

5 中頻采樣觀測接收機

MSDPD板內置一個完整的實中頻采樣觀測接收機,旨在對PA的耦合輸出進行數字化處理,并將其提供給DSP元件。此接收機的作用是觀測發射路徑的特性,因此其線性度和噪聲性能應優于受監控的對象,這樣才不會影響整體性能。觀測路徑導致的PA耦合輸出失真增加無法與PA失真區分開來,勢必影響DPD算法的有效性。為了獲得最佳的DPD性能,濾波器在目標頻段內應具有相對平坦的頻率響應和低群延遲變化。

觀測接收機包括一個雙平衡無源混頻器AD5365/7,它工作在900-2500MHz的RF頻段。這個高度線性的混頻器具有36dBm的輸入IP3,并且集成RF和LO巴倫及SPDT開關,支持在兩個LO源中進行選擇。混頻器將RF信號下變頻為184 MHz的典型IF信號,但該IF頻率可根據應用要求而改變。混頻器之后是數字控制可變增益放大器(DGA) AD8375,它提供24 dB的增益范圍,確保ADC的完整動態范圍得以維持。接下來是一個抗混疊濾波器,用以消除諧波和寬帶噪聲,然后由12位250MSPS ADC AD9230對信號進行數字化處理。四載波WCDMA回送結果顯示,ADC輸出端的實測性能為60dB SNRFS和77dBc無雜散動態范圍(SFDR)。

6 閉環性能

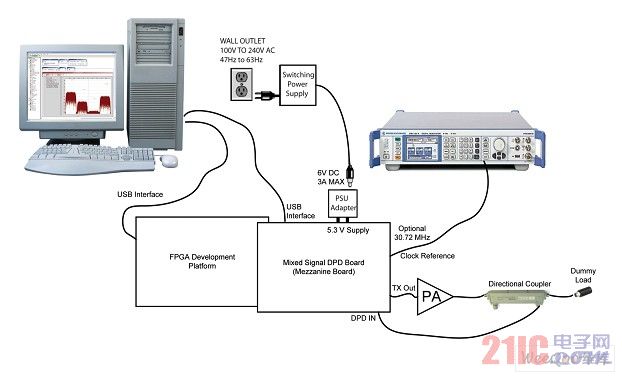

利用MSDPD板進行閉環發射機估算的典型設置如圖3所示。有了FPGA開發套件和MSDPD板之后,只需要電源連接、一臺帶USB接口的計算機和一個PA級就能構成完整的估算系統并運行。

圖3:帶FPGA開發平臺的MSDPD設置

圖4顯示使用MSDPD板進行線性化之前和之后的典型閉環DPD性能,測試信號為2.14GHz的20MHz帶寬LTE信號。結果令人振奮,預示著可以利用更低廉的PA來實現更高的電源效率和線性度。頻譜性能一般可提高至少25dB,具體取決于DPD算法。

圖4:MSDPD閉環性能

7 結語

ADI公司的MSDPD板是一款完備的工具,可供無線公司研究DPD技術在其系統中的作用。通過ADI的混合信號數字預失真平臺,設計人員可以靈活地設計、估算、優化DPD算法,而不必使用預封裝的封閉式解決方案。這款完整的無線電估算平臺不僅能幫助無線基礎設施設備的設計人員估算DPD,而且也為其它使用高功率放大器的應用快速估算DPD的作用開啟了方便之門,如有線廣播系統、微波點對點鏈路和無線中繼器等。理論上,它不僅可以補償高功率PA,也可以補償發射鏈本身的非線性。未來將有更多應用能夠受惠于DPD技術。