引言

為了讓現今的無線蜂窩網絡滿足日益增長的無線數據處理需求,全球加速向LTE/4G遷移的趨勢已經日益明顯。LTE或3.9G通過采用更有效的傳輸技術來提升數據速率,下一步,4G要提升到更高數據率,LTE、4G基礎設施給半導體供應商提出的挑戰是要用數字信號處理器(DSP)來滿足更高的數據處理需求,這些新型DSP的性能要比我們今天所用的DSP高出幾個數量級!

全球移動設備供應商協會(GSA)2010年4月的報告指出,全球已有31個國家承諾將部署64個LTE網絡,預計到2010年底將有22個LTE網絡交付使用,截止2011年年底將有39個或更多LTE網絡交付使用;總計88個運營商已經承諾將在42個國家部署LTE系統,有的已經開始進行測試或進行其他規劃活動。

半導體產業商機巨大但挑戰并存,LTE的性能需求是現今3G網絡性能需求的100到1000倍!相比目前在3G使用的CDMA無線技術,LTE采用的OFDMA技術采用多天線信號處理可以實現更高的頻譜效率,并可以支持更寬的頻譜。不過,OFDMA技術也更為復雜,需要的計算量比CDMA技術大得多。如圖1所示,從GSM遷移到UMTS/HSDPA再遷移到LTE,計算量需求要提升4、5個數量級――從大約10個MOPS(每秒百萬次運算)提高到10萬甚至1百萬MOPS,如此才可以提供LTE所要求的10到100 Mbps數據傳輸性能。

圖1、從GSM遷移到UMTS/HSDPA再到LTE,計算量需求要提升4、5個數量級

LTE還采用了先進的多天線信號處理技術,涉及到兩種最流行的技術MIMO(多輸入多輸出)編程和波束形成,同樣,這也都是高度密集計算型應用,需要新一代優化的專用DSP解決方案。

1 所需的DSP性能達到新高

LTE的運算處理要求如此巨大,因此對DSP的性能提升要求也是巨大的 ――單個通用DSP不能滿足這樣的性能需求,我們需要多顆DSP來實現LTE系統,而且這些DSP必須非常高效。以往的“通用”DSP將無法滿足數據處理要求。半導體供應商和IP供應商都在努力打造全新一代DSP,其性能可以滿足運營商新建基礎設施的需求。

要開發這些新的DSP,我們所面臨的挑戰是難以想像的,它無法通過提升DSP時鐘頻率來實現――這樣做會大幅增加功耗。我們需要針對運算任務優化的全新架構,這不僅意味著硬件層面的開發,也需要開發配套的軟件――因為越來越多的處理正在通過軟件來完成。

早期在開發軟件定義無線電(SDR)方面的嘗試令人失望,因為他們大多基于單一的DSP,其性能無法跟上運算需求的增長。而將密集運算交給RTL模塊的方法從根本上違背了軟件無線電的初衷,因為RTL模塊是不可編程的。然而我們可以用多顆DSP處理器來實現無線射頻系統――多顆針對不同任務進行優化設計的專用DSP。這些全新定制的專用DSP內核在設計之初就是從整個系統的角度出發,完全可以滿足LTE的運算性能需求。

2 所需的處理類型

一個典型的現代通信收發機可以劃分為三個計算域:

信號域:實現復數或實數數據的優化運算,包括FFT、濾波、同步以及矩陣運算等靠近系統中RF一側的運算。

比特軟值域(soft bit domain):包括從軟件解映射模塊到前向糾錯(FEC)解碼模塊等靠近接收端MAC一側的運算。

比特域:通常是在發送端靠近MAC一側,包括CRC編碼、加擾、FEC編碼和比特交織等操作。

這三種根本不同的計算需求需要不同類型的DSP內核(IP內核是必要的,因為從功耗和面積效率的角度看,所有這些功能必須在單芯片而不是分開的芯片上實現)。

3 LTE基帶子系統分析

圖2展示了一個LTE基帶子系統的功能模塊圖。該圖上方顯示了LTE接收端的信號處理通道。有天線連接到接收端RF模塊,它很可能是MIMO配置的多天線系統。RF接收模塊將信號輸出到前端濾波模塊,該模塊驅動隨后的OFDM信道估計和MIMO檢測模塊,這個模塊將來自多天線的信號合并起來而且可以改善接收端的帶寬和信號保真度,信號合并后會進行復數的解調,然后是前向糾錯,最終直接給LTE MAC層提供用于高層協議處理的比特流。在發射端,來自MAC層的比特流通過卷積編碼以及各種頻域變換后、輸出整形,然后送給發射端RF模塊、功率放大器和天線。

圖2 LTE基帶模塊方框圖

針對LTE的ConnX ATLAS參考架構

ConnX ATLAS參考架構是專為滿足從RF一側的前端濾波到MAC一側的傳輸模塊處理需求而開發的,ATLAS參考架構基于LTE 的UE CAT-4系統,支持一個發射天線,兩個接收天線和20MHz帶寬。也可以提供 10MHz及5MHz的ATLAS系統。圖3為ConnX ATLAS UE(用戶設備)的功能方框圖。

圖3 ATLAS LTE用戶設備方框圖

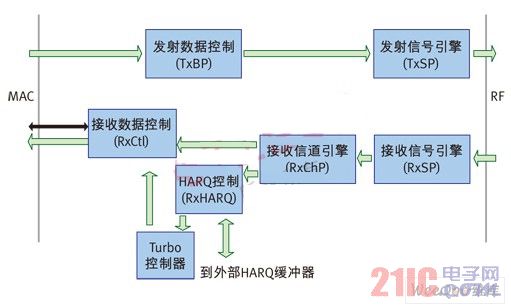

接收鏈路(圖3底端)接收來自前端濾波器的數據并為MAC生成傳輸數據塊,它包含控制器和三個計算域:信號處理域(接收信號處理器或RxSP)、矩陣處理域(接收信道處理器或RxChP)以及比特軟值域(接收混合ARQ 處理器或者叫 RxHARQ、Turbo引擎和接收控制處理器或者叫RxCP)

所有這些DSP包括Turbo 引擎,都可以用Tensilica公司的Xtensa可定制處理器技術實現,從而針對特定的任務進行優化。利用可配置技術還可以同時創建功能齊全的配套軟件工具鏈,所以不需要把時間浪費在開發不同DSP的基本指令集仿真器、調試器方面。

Tensilica公司的基帶引擎ConnX BBE16是構成RxSP和RxChP的基礎,該ConnX BBE16是一個128位、3發射、16MAC的數字信號處理器,能夠在單周期內完成多個復數乘法運算和一個復數基-4FFT運算。RxSP為每個符號產生源數據塊并進行信道估計。源數據塊會立即寫入接收鏈路中的下一個處理器RxChP的輸入緩沖區,RxChP執行MIMO解碼,并產生比特軟值給HARQ模塊。

RxHARQ處理器接受解碼后的比特軟值,并將它們合并為合適的冗余版本,接著執行HARQ重組以產生碼塊,碼塊被寫入Turbo解碼器的輸入緩沖區,完成解碼后又被寫入RxCP的輸入緩沖區。

RxCP是主控制器,執行休眠控制和電源管理。它對信道頭進行解碼以便配置收發鏈路正常工作,它還為MAC處理器提供了控制和數據接口。

4 ATLAS發射鏈路

發射鏈路包括兩個計算域和兩個處理器,發射位處理器(TxBP)和發射信號處理器(TxSP)。

TxBP執行CRC編碼、加擾、Turbo編碼、子塊交織、速率匹配和物理上行控制通道編碼。針對這一過程,Tensilica開發了一種比特流處理器(ConnX BSP3),它是一個32位DSP,增加了一些特殊指令,用于CRC、Turbo編碼和交織運算的加速。

TxSP接收編碼后的比特流,并產生相應的SC–FDMA符號,它們再提供給前端濾波器用于上變頻和MASK兼容, TxSP用Tensilica的BBE16 DSP實現,執行CRC編碼、位加擾、Turbo編碼、格雷碼編碼、RB映射、層映射、DRT、FFT和運營商附加的前綴匹配運算等。

5 基于同一架構的多核體系

ATLAS參考架構的優勢在于,所有的內核都基于Tensilica的Xtensa處理器架構。這意味著所有內核可以共享相同的基本指令集,并使用相同的開發工具。這樣就簡化了整個設計工作,并可以將培訓成本降到最低。

采用多核方案實現LTE系統,因為每個DSP內核是針對不同任務專門優化的,所以可以獲得LTE所需的最大效率和性能。ATLAS架構專為模塊化設計而開發,通過增減不同類型的處理器,它可以很容易擴展為不同性能級別的產品。由于處理器能夠進一步定制,所以設計人員可以貫徹Tensilica公司的設計理念并將其進一步發揚光大,以更好地匹配他們的性能、功耗和成本預算,或者更好地實現他們的獨特算法。

使用小型定制處理器的優勢是,如果不需要這部分處理能力的時候,該內核和它使用的存儲器都可以關斷(與3G和3.5G中的設計類似,在這些設計*耗是最受關注的),這有助于將功耗保持在最低水平。一個優化的多核架構可以允許使用更小、更低功耗的內核而無需提升系統頻率。

針對LTE系統中的關鍵運算定制DSP,還可以提高設計人員的工作效率。由于所有處理器都基于Tensilica的Xtensa可配置處理器內核,它們使用相同的軟件工具鏈。編譯器、調試器、ISS等都可以識別和利用定制的硬件并提高軟件的開發效率。

多顆DSP串行連接的方式也非常適合LTE無線算法中的數據流處理方式。因為一種算法只運行在一個內核上,所以軟件編程模型和調試都變得更加方便,多顆處理器之間的數據傳輸不是基于全局共享總線,而是專門的點對點連接,因此數據無需總線仲裁就可以快速地加載進其他DSP的存儲器中。此外,與典型的基于總線的系統相比,也不會因為更多處理器掛到總線上而降低性能。

6 復雜的LTE軟件

LTE系統中的軟件也相當復雜,需要真正了解需求的專業軟件供應商提供,Tensilica公司一直與mimoOn合作,該公司因軟件專長而倍受產業推崇,mimoOn開發了LTE的物理層軟件堆棧優化程序,可以讓采用ATLAS架構的專用Tensilica DSP發揮最高性能。

7 完整LTE L1 PHY的實現

ConnX的ATLAS LTE的參考架構實現了完整的LTE的L1物理層設計,包括了運算量要求極大的Tubro解碼器,并且完全基于軟件可編程的DSP處理器實現。它可以作為設計團隊實現LTE基帶系統的起點,設計團隊需要把L2的組件和其它的系統互連組件以及ATLAS組件整合在一起。

由于是模塊化設計,所以設計團隊可以部署ATLAS架構中的所有7個模塊,也可以復用他們已有的RTL模塊去替代一個或者更多的ATLAS組件。不管是LTE設計師還是以后的LTE Advanced(4G)設計師,ATLAS LTE參考架構中的模塊化組件都可以讓他們事半功倍。