1.1 用CPLD實現GPIB控制芯片的意義

綜觀現今市場上的測試儀器,不難發現GPIB總線有重要的作用,在研制臺式測試儀器的時候,客戶幾乎均要求具備GPIB接口。可是在實際研發過程中,卻發現GPIB控制芯片很難購買,而且價格昂貴。而且作為測試儀器具備GPIB的接口,一般只需要具有聽、講、串查功能,而不需要控、并查功能,這樣又會造成資源與功能的浪費。所以我們嘗試用CPLD來實現GPIB接口的聽、講、串查功能,不僅可擁有自主知識產權,節省了產品的成本,而且具有很大的靈活性。

1.2 GPIB控制芯片簡介

GPIB也叫HPIB,是一個數字化的24腳并行總線,由16條信號線和8條地線組成。這16條信號線分為8條數據線、5條控制線和3條握手線。8條數據線:從DIO1到DIO8,用來傳送命令、地址和數據;5條控制線:分別為ATN線、IFC線、REN線、SRQ線和EOI線,用來管理通過接口的有序信息流;3條握手線:DAV線、NRFD線和NDAC線,用于控制設備之間消息字節的傳送。發送消息方(源方)和接收消息方(受方)利用這3條握手線進行三線掛鉤,以保證數據線上的消息(命令或數據)能準確無誤地傳送。

在GPIB系統中,把器件與GPIB總線的一種交互作用定義成一種接口功能。GPIB標準接口共定義了10種接口功能。

1.3 設計軟件及設計芯片的選擇

開發工具采用ALTERA公司的MAXplusⅡ10.0。MAXplusⅡ開發工具是美國Altera公司自行設計的一種EDA軟件工具,它具有原理圖輸入和文本輸入(采用硬件描述語言)兩種輸入手段,配備有編輯、編譯、仿真、綜合、芯片編程等功能。

Altera公司是世界上從事可編程邏輯芯片生產的幾家主要廠商之一,其MAX3000A系列可編程邏輯芯片速度快,容量大,性價比高。我們選用的EPM3256ATC144-10,擁有256個宏單元,144個管腳,可自定義使用的管腳達116 個,4.5ns的傳輸延時完全能滿足要求。

2 GPIB控制器各個模塊的設計

我們可以把整個系統劃分為幾個子系統。其中包括和微處理器接口的讀寫電路,與GPIB母線通信的接口功能,以及內部寄存器。對每個子系統的設計也可以采用向下分解為模塊級設計,這樣在調試和組件系統時,不僅具有很強的靈活性,而且方便代碼的調試以及利于代碼的重利用。與微處理器接口的讀寫電路設計可以利用組合邏輯電路設計方法實現,其基本模塊,如:譯碼電路,讀寫電路,相對比較成熟,在設計的時候只要對其基本功能深刻理解的基礎上容易實現。與GPIB母線通信的子系統設計是本課題設計的重點也是難點,它不僅需要對IEEE488協議有深刻的認識,而且在接口功能子集的選擇上也有一定的要求。

2.1 微處理器(MCU)接口電路

微處理器(MCU)接口包括提供正確的寄存器訪問地址的譯碼電路,以及連同WE和DBIN一起構成的訪問GPIB控制器的讀寫電路,NCS用來選通地址譯碼。地址譯碼電路以及數據讀寫電路在數字電路設計中是最為成熟的電路,在此不作更多深入的闡述。值得注意的是GPIB控制器的讀寫信號并不是通常意義上的RD和WR信號,而是由DBIN和WE信號完成。而且,對13個寄存器的譯碼也用的僅僅是RS[0:2],這就需要和DBIN信號的配合來完成譯碼功能。

2.2 內部寄存器

GPIB控制器(參考NAT9914)的內部體系結構有13個寄存器,其中7個可寫寄存器,6個只讀寄存器。它們都是八位的,其中可讀寄存器有中斷狀態寄存器0(ISR0)、中斷狀態寄存器1(ISR1)、地址狀態寄存器(ASR)、總線狀態寄存器(BSR)、命令通過寄存器(CPR)、數據輸入寄存器(DIR);可寫寄存器有中斷屏蔽寄存器0(IMR0)、中斷屏蔽寄存器1(IMR1)、地址寄存器(ADR)、輔助命令寄存器(AUXCR)、串行查詢寄存器(SPR)、并行查找寄存器(PPR)、數據輸出寄存器(CDOR)。在GPIB 控制芯片的設計中對這十三個寄存器進行詳細的描述。本模塊的設計采用圖形方式,利用參數化模塊庫實現各個寄存器。

2.3 接口功能

GPIB標準接口共定義了10種接口功能。每一個接口功能由一組或多組相互聯系而又相互排斥的狀態來定義。在一個時刻,一組互聯又互斥的狀態中必須有一個而且也僅又一個狀態在起作用。在IEEE488協議中對接口功能的每一個狀態還做了兩方面的規定:

1.當某個狀態在起作用時,在接口上可以或必須發送的消息;

2.在什么條件下接口功能必須脫離某一狀態而進入同一組狀態的另一個狀態;這些因素決定了狀態的處理能力。接口功能狀態圖給出了全部狀態以及從一個狀態變遷到另一個狀態一切可能的途徑。由于篇幅的限制,下面以受方掛鉤接口功能AH功能為例,來介紹功能模塊的實現過程及原理。受方掛鉤功能賦予器件保證正確地接收遠地多線消息地能力。一個源方掛鉤功能與一個或多個受方掛鉤功能(分別含于各個器件中)的鏈鎖掛鉤序

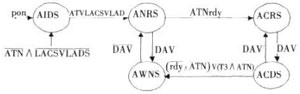

列保證每個消息拜特的異步傳遞。受方掛鉤功能可以延遲多線消息傳遞的開始或結束,直到器件準備好繼續參與傳遞過程為止。狀態圖如圖1:

圖1 AH功能狀態圖

其狀態轉換的VHDL語言描述如下:

process(c_state,n_state)

begin AIDS<='0';ANRS<='0';AWNS<='0';ACDS<='0';ACRS<='0'; case c_state is

when s1=>AIDS<='1';NRFD<='1';NDAC<='1';

IF (ATN OR LACS OR LADS)='1' then n_state<=s2;

else n_state<=s1; end if;

when s2=>ANRS<='1';NRFD<='0';NDAC<='0';

IF ((ATN OR rdy) and not tcs)= '1' then n_state<=s3;

elsif DAV='1' then n_state<=s5;

else n_state<=s2; end if;

when s3=>ACRS<='1';NRFD<='1';NDAC<='0'; IF DAV='1' then n_state<=s4;

ELSIF (NOT ATN AND NOT rdy)='1' THEN n_state<=s2;

else n_state<=s3; end if;

when s4=>ACDS<='1';NRFD<='0';NDAC<='0';

IF ((ATN AND T3) OR (NOT ATN AND NOT rdy))='1' THEN n_state<=s5;

else n_state<=s4; end if;

when s5=>AWNS<='1';NRFD<='0';NDAC<='1'; IF DAV='0' then n_state<=s2;

else n_state<=s5; end if;

end case;

end process;

根據儀器的具體要求,由于大多數測試系統只要求被遠控,并不要求控功能,而并查功能在系統組建中屬于可選項,很少用到,為了簡化系統,設計中徹底去掉此兩項功能。其他功能模塊包括:講者功能(T)、聽者功能(L)、源方掛鉤功能(SH)、受方掛鉤功能(AH)、服務請求功能(SR)、遠控本控功能(RL)、設備觸發功能(DT)和設備清除功能(DC)。其設計原理與AH相同,在這里就不做詳細論述。

2.4 輔助命令譯碼器與多線消息譯碼器

1.輔助命令譯碼器通過對輔助命令寄存器F0到F4位的譯碼來生成輔助命令。輔助命令共有stactic和pulse兩種,即靜態和脈沖兩種信號,靜態命令用電平的高低來表示。而動態命令則通過一個周期的方波脈沖信號來產生,要求脈沖命令至少在寫完輔助命令寄存器后保持一個周期。我們通過VHDL語言來完成本模塊的設計。

2.多線消息是處于相互排斥的編碼集中但又公用一組信號線來傳遞的消息。在母線上,每一時刻只能傳遞一條多線消息(一個消息拜特)。多線消息在遠地消息譯碼單元內進行譯碼。在這個譯碼單元,通過消息傳遞單元(DIO 線)來接收母線上的消息。消息譯碼單元僅在命令工作方式下(ATN=真)期間起作用。這樣的接口消息可能是地址、通令、專令或副令之一。在數據工作方式(ATN=假)中,數據線上攜帶器件消息,這時譯碼單元不起作用。在本GPIB控制器設計中,此模塊還包含了地址比較器,這樣可以得到內部狀態機所需的與地址相關的信號。用VHDL語言完成其設計,并例化成模塊。

2.5 三態I/O通道

需要注意的是芯片數據通道中八條數據線與控制數據流向的八條控制線都是雙向的,所以必須對I/O通道進行設置。實現雙向總線,就需要使用可編程邏輯器件的雙向口構造雙向

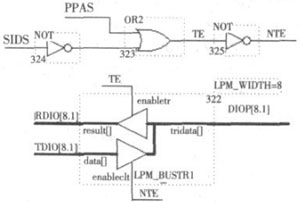

三態總線。三態總線的實現,需要使用三態緩沖器,實現高、低電平和高阻三個狀態。基于ALTERA公司的CPLD系列器件的特點,我們在設計的時候,內部避免使用雙向的三態總線,將雙向的信號分別直接引到外部。在外部設計雙向三態總線。設計中采用圖形方式輸入,利用參數化模塊庫(LPM)實現。這種方法尤為清晰簡便。如圖所示:

圖2 三態總線的實現

在這里用TE信號來作為三態總線的方向控制信號。不考慮控功能,當本設備處于并行點名狀態,或者作為非命令數據的源接受方時,TE信號為真,即TE=PPAS+~SIDS。

2.6 GPIB總線中的三線掛鉤技術的實現

三線掛鉤技術是本設計的關鍵,因為在總線傳輸中,所有的命令和數據的傳送都要通過三線掛鉤來實現。

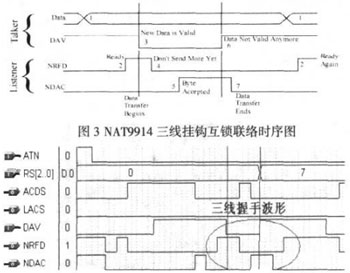

GPIB總線中的三線掛鉤技術(DAV、NRFD、NDAC)可以自動適應測試系統中各種不同器件的傳輸速率。源方作為講者或者控者的器件,發DAV消息。受方作為聽者的器件,發NRFD、NDAC消息。三條握手線,DAV線、NRFD線和NDAC線,用于控制設備之間消息字節的傳送。發送消息方(源方)和接收消息方(受方)利用這3條握手線進行三線掛鉤,以保證數據線上的消息(命令或數據)能準確無誤地傳送。

圖4 本設計三線掛鉤仿真圖

通過對系統的仿真,對比NI公司的GPIB控制器NAT9914數據手冊上的三線掛鉤的時序圖可以看出,本設計成功地實現了三線掛鉤的要求。

2.7 系統調試

調試是軟硬件設計過程中必不可少的一環。最終程序通過ByteBlaster專用下載電纜下載EPM3256ATC144-10芯片中,將下載好程序地CPLD取代原來系統中的NAT9914進行在線 調試。通過反復的試驗,成功地實現了CPLD 代 GPIB 控制器的大部分功能。

3 結 論

本文的創新點:采用低成本的CPLD器件替代了價格昂貴,且難以購買的GPIB控制芯片,成功的實現了具有自主知識產權的IP CORE,并且所有核心模塊完全采用VHDL語言實現,能夠在不同的開發環境上移植,可以根據不同的應用環境,對其進行進行剪裁和優化,不僅大大節省了成本,而且具有很大的靈活性。