直接數字頻率合成技術(Direct Digital Synthesize,DDS)是繼直接頻率合成技術和鎖相式頻率合成技術之后的第三代頻率合成技術。它采用全數字技術,并從相位角度出發進行頻率合成。隨著微電子技術和數字集成電路的飛速發展,以及電子工程領域的實際需要,DDS日益顯露出優于傳統頻率合成技術的一些性能,高分辨率、極短的頻率切換時間、相位噪聲低、便于集成等,逐步成為現代頻率合成技術中的佼佼者。

目前,DDS的設計大多是應用HDL(Hardware Description Language)對其進行邏輯描述。整個設計可以很容易地實現參數改變和設計移植,給設計者帶來很大的方便。Verilog HDL就是其中一種標準化的硬件描述語言,它不僅可以進行功能描述,還可以對仿真測試矢量進行設計。Altera公司開發的QuartusⅡ設計軟件,提供了Verilog HDL的設計界面以及編譯平臺,并且該公司還集成了可供程序下載的FPGA器件CYCLONEⅡ系列芯片,這樣大大縮短了DDS的設計周期。

1 DDS的設計原理

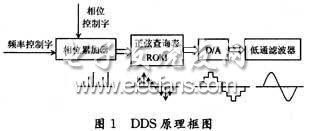

DDS的原理圖如圖1所示。DDS實現頻率合成主要是通過查表的方式進行的。

正弦查詢表是一個只讀存儲器(ROM),以相位為地址,存有1個或多個按0°~360°相位劃分幅值的正弦波幅度信息。相位累加器對頻率控制字進行累加運算,若需要還可以加入相位控制字,得到的結果作為正弦波查詢表的地址。正弦查詢表的輸出為數字化正弦幅度值,通過D/A轉換器轉化為近似正弦波的階梯波,再通過低通濾波器濾除高頻成分和噪聲最終得到一個純正度很高的正弦波。

1.1 建模

如圖2所示正弦波y=sin(2πx),若以f量化的量化頻率對其幅度值進行量化,一個周期可以得到M=f量化個幅度值。將這些幅度值按順序存入到ROM。相位累加器在參考時鐘的驅動下,每來1個脈沖,輸出就會增加1個步長相位增量X,輸出數據作為地址送入ROM中,讀出對應的幅度值形成相應的波形。

1.2 參數設定

DDS輸出信號頻率:

其中,X為頻率累加器設定值;N為相位累加器位數;fc為參考時鐘頻率。

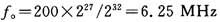

例如,假定基準時鐘為200 MHz,累加器的位數為32,頻率控制字X為:

0x08000000H,即為227,則:

再設定頻率控制字X為0x80000000H,即為231,則:

可見,理論上通過設定DDS相位累加器位數N、頻率控制字X和基準時鐘fc的值,就可以得到任一頻率的輸出。

頻率分辨率為:fres=fc/2N,由參考時鐘和累加器的位數決定,當參考時鐘的頻率越高,相位累加器的位數越高,所得到的頻率分辨率就越高。

1.3 方案的選擇

在利用FPGA制作DDS時,相位累加器是決定DDS性能的一個關鍵部分。一方面可以利用進位鏈來實現快速、高效的電路結構,同時長的進位鏈會減少其他邏輯的布線資源,限制整個系統速度的提高;另一方面可以利用流水線技術提高工作頻率,但系統頻率轉換速度會相對降低。在選擇累加器實現方案時需要綜合考慮。

正弦波查詢表ROM也是制作的重點。在FPGA中ROM表的尺寸隨著地址位數或數據位數的增加呈指數遞增,如何在滿足性能的前提下節省資源開銷。一方面通過相位累加器的輸出截斷方式,例如從32位的相位累加器結果中提取高16位作為ROM的查詢地址,由此而產生的誤差會對頻譜純度有影響,但是對波形的精度的影響是可以忽略的;另一方面可以根據信號周期對稱性來壓縮ROM的尺寸,這時系統硬件設計復雜度會有所增加。因此,需要選取合適的參數和ROM壓縮技術,在滿足系統性能的前提下使得系統盡量優化。

2 Verilog HDL實現DDS模塊

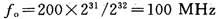

2.1 相位累加器

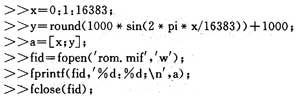

上述為相位累加器的Verilog HDL功能實現,其中數據寬度為32位。同時利用QuartusⅡ進行波形仿真見圖3。對應的模塊符號見圖4。

2.2 ROM正弦查詢表

根據DDS的原理,將正弦波形的量化數據存儲于波形查詢表ROM中,即可完成正弦波發生的功能。Altera公司提供了LPM ROM(ROM兆函數),這里只需借助Matlab生成.mif文件,并加載到LPM ROM中即可得到所需的正弦查詢表ROM。

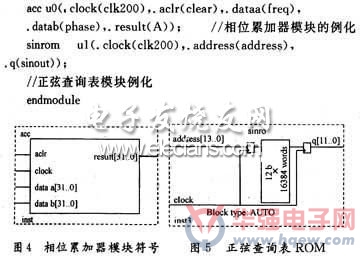

在Matlab中,運行下面的語句可以得到儲存正弦波數字幅度值的.mif文件。例如產生214×12 b的正弦波0~27π幅度值,語句如下:

由此而生成的rom.mif文件內容是正弦波0~2π數字幅度值,但是格式不符合.mif。文件的格式,需要對其進行修改。.mif文件的格式如下:

這樣通過例化LPM ROM得到了正弦波查詢表ROM的模塊,地址寬度為14位,輸出數據為12位。模塊符號見圖5。

2.3 DDS頂層模塊的實現

上述代碼為DDS模塊的Verilog HDL頂層文件。對應的模塊圖見圖6。

若需要利用NIOSⅡ對其進行控制,需要并將DDS模塊加載到NIOSⅡ的系統中。例如,通過NIOSⅡ為DDS模塊的頻率控制字freq和相位控制字phase置數。此時DDS的代碼應改為:

模塊的輸入端口添加了寫信號iwr、地址信號addr和與NIOSⅡ同步的時鐘信號iclk,這樣是為了將DDS模塊連接到Avalon總線上,利用總線和NIOSⅡ進行通信。加載到NIOSⅡ系統之前,需要將該模塊進行仿真和調試。仿真結果如圖7所示。

結論:

對于整個模塊的驅動時鐘,若時鐘源器件的頻率不符合實際需要,需要再設計一個倍(分)頻器將其倍頻或是分頻。例如現有時鐘源為50 MHz,可以使用FPGA中的PLL(鎖相環)實現4倍頻得到200 MHz。