1 任務背景

SDRAM具有大容量和高速的優點,目前其存取速度可以達到100~133MHz,單片容量可以達到64Mbit或更高,因此在需要高速、大容量存儲器的系統中得到廣泛應用,如應用在目前的計算機內存中。但是SDRAM的控制比較復雜,其接口不能直接與目前廣泛應用的普通微處理器如MCS-51系列、Motorola 68000系列連接,這樣就限制了SDRAM在微處理器系統中的應用。

我們的任務是設計一個通用微處理器,它要具有語音、數據、圖像等多種處理功能,并具有RS232、USB等多種接口,另外由于多個通道的數據都需要進行緩存和處理,因此高速大容量的緩存是此系統必須的,所以選用了SDRAM作為緩存器件。來自多個輸入通道的數據在采集后需要暫時存儲在SDRAM中,處理后的數據也需要存儲在SDRAM中,再輸出到輸出通道中。在SDRAM與多個輸入輸出通道之間,采用多個雙口RAM作為接口器件。輸入通道采集的數據首先存儲在雙口RAM中,采集滿后,通過若干條指令將RAM中的數據轉移到SDRAM中的一定位置中,將SDRAM中的數據轉移到RAM中也只需要若干條指令來完成。這樣通過幾條指令來設置RAM起始地址、SDRAM起始地址、傳送數據長度、傳送數據方向之后,SDRAM與RAM之間數據傳送就完全可以通過硬件實現,不必占用微處理器的指令時間。

2 SDRAM簡介

SDRAM具有多種工作模式,內部操作是一個非常復雜的狀態機。SDRAM的管腳分為以下幾類:

(1)控制信號:包括片選、時鐘、時鐘有效、行/列地址選擇、讀寫選擇、數據有效;

(2)地址:時分復用管腳,根據行/列地址選擇管腳控制輸入地址為行地址或列地址;

(3)數據:雙向管腳,受數據有效控制;根據控制信號和地址輸入,SDRAM包括多種輸入命令:① 模式寄存器設置命令;② 激活命令;③ 預充命令;④寫命令;⑤ 讀命令;⑥自動刷新命令;⑦ 自我刷新命令;⑧突發停止命令;⑨ 空操作命令。

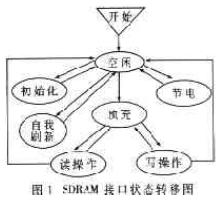

根據輸入命令,SDRAM狀態在內部狀態間轉移。內部狀態包括:①模式寄存器設置狀態;②激活狀態;③預充狀態;④寫狀態;⑤讀狀態;⑥自動刷新狀態;⑦自我刷新狀態;⑧節電狀態。

3 SDRAM接口狀態機設計

根據系統的要求,采用固定型號SDRAM,我們對SDRAM的操作進行了以下簡化:

(1)存取模式,只采用突發讀寫數據模式,固定突發數據長度為2;

(2)DRAM讀命令輸入到數據輸出延時時鐘周期為2;

(3)不采用自動刷新模式;

(4)DRAM的初始化、節電模式由微處理器控制;

(5)DRAM為16位數據總線,RAM為32位數據總線,SDRAM進行一次突發操作,RAM進行一次讀寫操作,以實現速度匹配;

(6)DRAM和RAM讀寫地址采用遞增模式,連續變化。

簡化的SDRAM接口狀態轉移圖如圖1所示。其中,初始化、自我刷新、電源關斷、讀操作、寫操作、預充等狀態又分別各由一組子狀態組成。

為充分利用SDRAM的高速存取特性,讀、寫時序必須仔細設計,應基本可以實現每個時鐘周期進行一次數據存取。

3.1 SDRAM讀操作時序設計

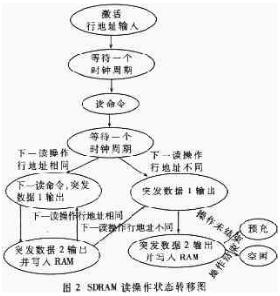

當數據轉移方向為從SDRAM到雙口RAM時,如果SDRAM讀操作行地址未發生變化,可以滿足每時鐘周期輸出一次數據的高速操作。但是當SDRAM行地址發生變化時,必須返回預充狀態,由于從SDRAM的讀命令輸入到SDRAM數據輸出之間有2個時鐘周期的延時,所以判斷下一讀操作的行地址是否發生變化必須提前兩個周期判斷。讀操作部分的狀態轉移圖如圖2所示。

3.2 SDRAM寫操作時序設計

當數據轉移方向為從雙口RAM到SDRAM時,如果SDRAM寫操作行地址未發生變化,可以滿足每時鐘周期寫入一次數據的高速操作。但是當SDRAM行地址發生變化時,必須返回預充狀態,由于從SDRAM的寫命令輸入到SDRAM數據輸入之間沒有延時,所以判斷下一寫操作的行地址是否發生變化無需提前判斷,因此寫操作狀態轉移圖比讀操作部分簡單。寫操作部分的狀態轉移圖如圖3所示。

在所設計的讀、寫操作時序中,SDRAM地址、數據、控制信號和RAM部分的地址、數據、讀寫控制信號均由有限狀態機產生,因此在狀態轉移過程中還必須仔細考慮RAM部分輸出控制信號的時序關系。

4 VHDL實現

硬件描述語言VHDL(Very=High Speed IC Hardware Description Language)是一種應用于電路設計的高層次描述語言,具有行為級、寄存器傳輸級和門級等多層次描述,并且具有簡單、易讀、易修改和與工藝無關等優點。目前VHDL語言已經得到多種EDA工具的支持,綜合工具得到迅速發展,VHDL語言的行為級綜合也已經得到支持和實現,因此利用VHDL語言進行電路設計可以節約開發成本,縮短周期。在VHDL語言輸入中也有多種形式,例如可以支持直接由狀態轉移圖生成VHDL語言。因此在設計SDRAM狀態轉移圖后,可以直接產生VHDL程序,在功能仿真正確后,可以進行綜合、FPGA布局布線和后仿真。

以上介紹了一種應用于通用微處理器系統中的SDRAM與雙口RAM之間的數據轉移接口控制電路,由VHDL語言設計,用Xilinx公司4000系列FPGA實現,目前該電路硬件實現和微處理器系統已經通過驗證,證明可將SDRAM作為高速、大容量存儲器應用在簡單電子系統中。