本文將考察一款新型精密16位DAC,同時(shí)針對(duì)性能可與變壓器媲美的高速互補(bǔ)電流輸出DAC的輸出緩沖談一些想法。

電壓開(kāi)關(guān)式16位DAC提供低噪聲、快速建立時(shí)間和更出色的線性度

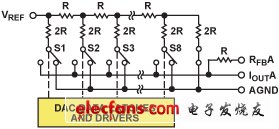

基于突破性10位CMOSAD7520--推出已近40年--的電阻梯乘法DAC最初用于反相運(yùn)算放大器,而放大器的求和點(diǎn) (IOUTA) 則提供了方便的虛擬地(圖1)。

圖1. CMOS乘法DAC架構(gòu)

然而,在某些限制條件下,它們也可用于提供同相電壓輸出的電壓開(kāi)關(guān)配置 其中,運(yùn)算放大器用作電壓緩沖器(圖2)。此處,基準(zhǔn)電壓VIN施加于OUT,輸出電壓VOUT,則由VREF提供。后來(lái)不久即出現(xiàn)了針對(duì)這種用途而優(yōu)化的12位版本。

圖2. 電壓開(kāi)關(guān)模式下的乘法DAC

快速推進(jìn)到現(xiàn)在: 隨著單電源系統(tǒng)的不斷普及,設(shè)計(jì)師面對(duì)一個(gè)挑戰(zhàn),即在維持高電壓下的性能水平的同時(shí)控制功耗。對(duì)能用于這種模式的更高分辨率(最高16位)的器件的需求也日益增加。

在電壓開(kāi)關(guān)模式下使用乘法DAC的顯著優(yōu)勢(shì)是不會(huì)發(fā)生信號(hào)反相,因此,正基準(zhǔn)電壓會(huì)導(dǎo)致正輸出電壓。但當(dāng)用于該模式時(shí),R-2R梯形架構(gòu)也存在一個(gè)缺陷。相對(duì)于同一DAC用于電流導(dǎo)引模式的情況,與R-2R梯形電阻串聯(lián)的N溝道開(kāi)關(guān)的非線性電阻將導(dǎo)致積分線性度(INL)下降。

為了克服乘法DAC的不足并同時(shí)保持電壓開(kāi)關(guān)的優(yōu)勢(shì),人們開(kāi)發(fā)出了新型的高分辨率DAC,比如AD5541A,(如圖3所示)。AD5541A采用一個(gè)部分分段的R-2R梯形網(wǎng)絡(luò)和互補(bǔ)開(kāi)關(guān),在16位分辨率下可實(shí)現(xiàn)±1-LSB精度,在?40°C至+125°C的整個(gè)額定溫度范圍內(nèi)均無(wú)需調(diào)整,其噪聲值為11.8 nV/√Hz,建立時(shí)間為1?s.

圖3. AD5541A架構(gòu)

性能特點(diǎn)

建立時(shí)間: 圖4和圖5比較了乘法DAC在電壓模式下的建立時(shí)間以及AD5541A的建立時(shí)間。當(dāng)輸出上的容性負(fù)載最小時(shí),AD5541A的建立時(shí)間約為1?s.

圖4. 乘法DAC的建立時(shí)間

圖5. AD5541A的建立時(shí)間

噪聲頻譜密度: 表1比較了AD5541A和乘法DAC的噪聲頻譜密度。AD5541A在10kHz下的性能略占優(yōu)勢(shì),在1 kHz下優(yōu)勢(shì)非常明顯。

表1. AD5541A與乘法DAC的噪聲頻譜密度

積分非線性: 積分非線性(INL)衡量DAC的理想輸出與排除增益和失調(diào)誤差之后的實(shí)際輸出之間的最大偏差。與R-2R網(wǎng)絡(luò)串聯(lián)的開(kāi)關(guān)可能會(huì)影響INL.乘法DAC一般采用NMOS開(kāi)關(guān)。當(dāng)用于電壓開(kāi)關(guān)模式時(shí),NMOS開(kāi)關(guān)的源極連接至基準(zhǔn)電壓,漏極連接至梯形電阻,柵極由內(nèi)部邏輯驅(qū)動(dòng)(圖6)。

圖6. 乘法DAC開(kāi)關(guān)

要使電流在NMOS器件中流動(dòng), VGS必須大于閾值電壓, VT.在電壓開(kāi)關(guān)模式下, VGS = VLOGIC – VIN必須大于VT = 0.7 V.

乘法DAC的R-2R梯形電阻設(shè)計(jì)用于將電流平均分配至各個(gè)引腳。這就要求總接地電阻(從各引腳頂部看)完全相同。這可以通過(guò)調(diào)節(jié)開(kāi)關(guān)來(lái)實(shí)現(xiàn),其中,各個(gè)開(kāi)關(guān)的大小與其導(dǎo)通電阻成比例。如果一個(gè)引腳的電阻發(fā)生變化,則流過(guò)該引腳的電流將發(fā)生變化,結(jié)果導(dǎo)致線性度誤差。VIN不能大到會(huì)使開(kāi)關(guān)關(guān)閉的程度,但必須足以使開(kāi)關(guān)電阻保持低位,因?yàn)閂IN的變化會(huì)影響VGS 從而導(dǎo)致導(dǎo)通電阻發(fā)生非線性變化,如下所示:

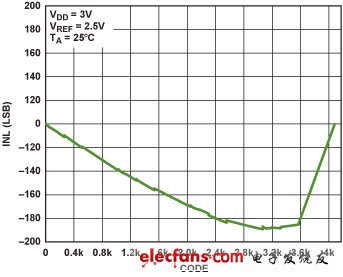

導(dǎo)通電阻的這種變化會(huì)使電流失衡,并使線性度下降。因此,乘法DAC上的電源電壓不能減少太多。相反,基準(zhǔn)電壓超過(guò)AGND的值不得高于1V,以維持線性度。對(duì)于5V電源,當(dāng)從1.25V基準(zhǔn)電壓變化至2.5V基準(zhǔn)電壓時(shí),線性度將開(kāi)始下降,如圖7和圖8所示。當(dāng)電源電壓降至3V時(shí),線性度將完全崩潰,如圖9所示。

圖7. INL of IOUT 乘法DAC在反相模式下的INL,( VDD = 5 V, VREF = 1.25 V)

圖8. INL of IOUT乘法DAC在反相模式下的INL(VDD = 5 V, VREF = 2.5 V)

圖9. 乘法DAC在反相模式下的INL( VDD = 3 V, VREF = 2.5 V)

為了減少這種影響,AD5541A采用互補(bǔ)NMOS/PMOS開(kāi)關(guān),如圖10所示。現(xiàn)在,開(kāi)關(guān)的總導(dǎo)通電阻來(lái)自NMOS和PMOS開(kāi)關(guān)的共同貢獻(xiàn)。如前所示,NMOS開(kāi)關(guān)的柵極電壓由內(nèi)部邏輯控制。內(nèi)部產(chǎn)生的電壓,VGN,設(shè)置理想柵極電壓,以使NMOS的導(dǎo)通電阻與PMOS的相平衡。開(kāi)關(guān)的大小通過(guò)代碼調(diào)節(jié),以使導(dǎo)通電阻隨代碼調(diào)節(jié)。因此,電流將上下調(diào)節(jié),精度將得以維持。由于基準(zhǔn)輸入的阻抗隨代碼變化,因此,應(yīng)通過(guò)低阻抗源驅(qū)動(dòng)。

圖10. 互補(bǔ)NMOS/PMOS開(kāi)關(guān)

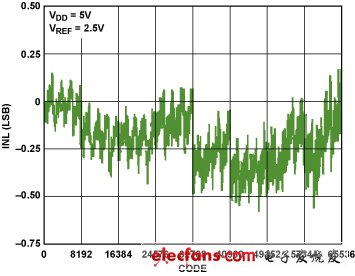

圖11和圖12所示為AD5541A在5 V和2.5 V基準(zhǔn)電壓下的INL性能。

圖11. AD5541A的INL( VDD = 5.5 V, VREF = 5 V)

圖12. AD5541A的INL( VDD = 5.5 V, VREF = 2.5 V)

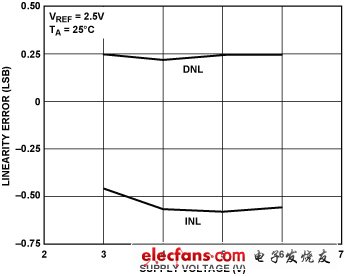

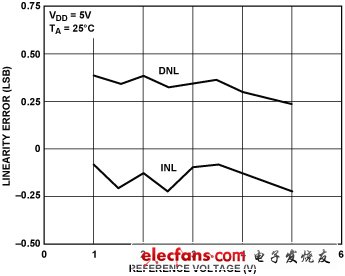

如圖13和圖14所示,線性度在較寬的基準(zhǔn)電壓和電源電壓下變化極小。DNL行為與INL類似。AD5541A線性度的額定范圍以溫度和電源電壓為基礎(chǔ);基準(zhǔn)電壓可能從2.5V變化至電源電壓。

圖13. AD5541A INL與電源電壓

圖14. AD5541A INL與基準(zhǔn)電壓

AD5541A的更多詳情

AD5541A串行輸入、單電源、電壓輸出nanoDAC+數(shù)模轉(zhuǎn)換器提供16位分辨率和±0.5LSB典型積分/微分非線性特性。特別適合將乘法DAC用于電壓開(kāi)關(guān)模式的應(yīng)用。在額定溫度范圍和電源電壓范圍內(nèi)均有優(yōu)異表現(xiàn),可實(shí)現(xiàn)出色的線性度,并可用于需要精密直流性能和快速建立時(shí)間的3V至5V系統(tǒng)。采用2V至電源電壓范圍內(nèi)的外部基準(zhǔn)電壓時(shí),無(wú)緩沖電壓輸出可以將60kΩ負(fù)載從0V驅(qū)動(dòng)至VREF.該器件可以在1?s內(nèi)建立至? LSB,噪聲為11.8nV/√Hz,并具有低毛刺特性,非常適合部署在各種醫(yī)療、航空航天、通信和工業(yè)應(yīng)用中。其3線式低功耗SPI串行接口能夠以高達(dá)50 MHz時(shí)鐘速率工作。AD5541A采用2.7V至5.5V單電源供電,功耗僅125?A.它提供8引腳和10引腳LFCSP及10引腳MSOP封裝,額定溫度范圍為–40°C至+125°C,千片訂量報(bào)價(jià)為6.25美元/片。

高速電流輸出DAC緩沖器

變壓器通常被認(rèn)為是將高速電流輸出DAC的互補(bǔ)輸出轉(zhuǎn)換為單端電壓輸出的最佳選擇,因?yàn)樽儔浩鞑粫?huì)增加噪聲,也不會(huì)消耗功率。盡管變壓器在高頻信號(hào)下表現(xiàn)良好,但它們無(wú)法處理許多儀表和醫(yī)療應(yīng)用所需要的低頻信號(hào)。這些應(yīng)用要求一個(gè)低功耗、低失真、低噪聲的高速放大器,以將互補(bǔ)電流轉(zhuǎn)換成單端電壓。此處展示的三個(gè)電路接受來(lái)自DAC的互補(bǔ)輸出電流,并提供單端輸出電壓。將后兩者的失真與變壓器解決方案進(jìn)行比較。

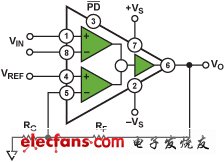

差分放大器: AD8129和AD8130差分轉(zhuǎn)單端放大器(圖15)用于第一個(gè)電路(圖16)。它們?cè)诟哳l下具有極高的共模抑制性能。AD8129在增益為10或以上時(shí)保持穩(wěn)定,而AD8130則在單位增益下保持穩(wěn)定。它們的用戶可調(diào)增益可以由, RF 和 RG.兩個(gè)電阻的比值來(lái)設(shè)置。AD8129和AD8130在引腳1和引腳8上具有很高的輸入阻抗,不受增益設(shè)置的影響。基準(zhǔn)電壓 (VREF, 引腳4)可以用來(lái)設(shè)置偏置電壓,該偏置電壓被乘以與差分輸入電壓相同的增益。

圖15. AD8129/AD8130差動(dòng)放大器

圖16. 采用AD8129/AD8130的DAC緩沖器

方程1和方程2所示為放大器的輸出電壓與DAC的互補(bǔ)輸出電流之間的關(guān)系。端接電阻RT,執(zhí)行電流-電壓轉(zhuǎn)換;RF 與RG 之比決定了增益。 VREF 在方程2中被設(shè)為0.

![]() (1)

(1)

(2)

(2)

在圖16中,該電路采用一個(gè)四通道高速、低功耗、14位DAC,其中,互補(bǔ)電流輸出級(jí)將提高速度,降低低功耗DAC的失真。

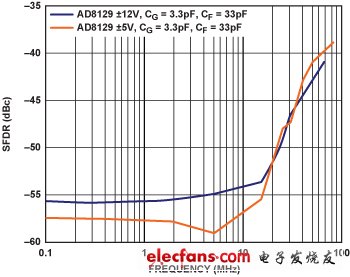

圖17展示的是電路的無(wú)雜散動(dòng)態(tài)范圍(SFDR),它是頻率的函數(shù),采用DAC和AD8129,其中,RF = 2k?, RG = 221?, RT = 100?, 且VO = 8Vp-p, 兩個(gè)電源電壓對(duì)應(yīng)的不同值。此處選擇了AD8129,因?yàn)樗峁┹^大的輸出信號(hào),在G = 10時(shí)保持穩(wěn)定,與AD8130相比,具有較高的增益帶寬積。兩種情況下,SFDR一般都要好于55dB,超過(guò)10MHz,在低電源電壓下,約有>3dB的改善。

圖17. DAC和AD8129的失真 VO = 8 V p-p

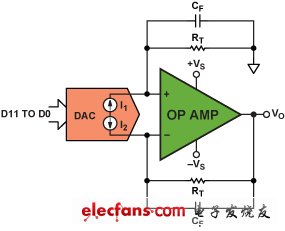

單位增益下的運(yùn)算放大器: 第二個(gè)電路(圖18)采用了一個(gè)高速放大器與兩個(gè) RT電阻。該放大器只是通過(guò), RT將互補(bǔ)電流I1和 I2, 轉(zhuǎn)換成單端輸出電壓, VO這個(gè)簡(jiǎn)單的電路不允許以放大器為增益模塊放大信號(hào)。

圖18. 采用運(yùn)算放大器的簡(jiǎn)單差分到單端轉(zhuǎn)換器

方程3所示為VO 與DAC輸出電流之間的關(guān)系。失真數(shù)據(jù)通過(guò)與RT并聯(lián)的5pF電容進(jìn)行測(cè)量

![]() (3)

(3)

為了展示這個(gè)電路的性能,DAC與ADA4857 和 ADA4817 運(yùn)算放大器配對(duì),其中T = 125? (and CT = CF = 5 pF與RT 并聯(lián),以實(shí)現(xiàn)穩(wěn)定性和低通濾波)。單通道ADA4857-1和雙通道ADA4857-2為單位增益穩(wěn)定型、高速、電壓反饋放大器,具有低失真、低噪聲和高壓擺率等特點(diǎn)。作為眾多應(yīng)用(包括超聲、ATE、有源濾波器、ADC驅(qū)動(dòng)器等)的理想解決方案,其帶寬為850 MHz,壓擺率為2800 V/μs,0.1%建立時(shí)間為10ns--全部都是在5mA的靜態(tài)工作電流下實(shí)現(xiàn)。ADA4857-1和ADA4857-2具有寬工作電壓范圍(5V至10V),特別適合需要寬動(dòng)態(tài)范圍、精密、高速度和低功耗的系統(tǒng)

ADA4817-1(單通道)和ADA4817-2(雙通道)FastFET?放大器是具有FET輸入的單位增益穩(wěn)定、超高速電壓反饋型運(yùn)算放大器。它們采用ADI公司的專有超快速互補(bǔ)雙極性(XFCB)工藝制造,具有超低的噪聲(4nV/√Hz和2.5fA/√Hz)和極高的輸入阻抗。其輸入電容為1.3pF,最大失調(diào)電壓為2mV,功耗低(19mA),?3dB帶寬較寬(1050MHz),非常適合數(shù)據(jù)采集前端、光電二極管前置放大器以及其他寬帶跨阻應(yīng)用。它們具有5V至10V的寬電源電壓范圍,可采用單電源或雙電源供電,適合包括有源濾波、ADC驅(qū)動(dòng)和DAC緩沖在內(nèi)的各種應(yīng)用。

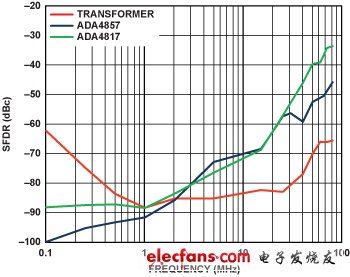

圖19比較了該電路在VO = 500mV p-p 時(shí)相對(duì)于一個(gè)采用變壓器的電路的失真和頻率之間的關(guān)系。變壓器的失真低于放大器,后者的增益在高頻下不斷下降,但采用變壓器的失真卻在低頻下不斷變差。在此,可在有限范圍內(nèi)實(shí)現(xiàn)接近90dB的SFDR,在高達(dá)10MHz時(shí)優(yōu)于70dB.

圖19. DAC、ADA4857和ADA4817的失真 VO = 500 mV p-p, RL = 1 k?

具有增益運(yùn)算放大器: 第三個(gè)電路(圖20)也使用了相同的高速運(yùn)算放大器,但所含電阻網(wǎng)絡(luò)拉遠(yuǎn)了放大器與DAC之間的距離,支持增益設(shè)置,并可以利用VREF1和 VREF2兩個(gè)基準(zhǔn)電壓之一調(diào)整輸出偏置電壓。

圖20. 支持增益和偏置功能的差分到單端轉(zhuǎn)換

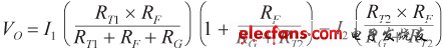

方程4定義了DAC輸出電流與放大器輸出電壓在 VREF1 = VREF1 = 0. 時(shí)的關(guān)系。為了匹配DAC之外的放大器網(wǎng)絡(luò)的輸入阻抗RT1 和 RT2, 兩個(gè)端接電阻必須單獨(dú)設(shè)置,同時(shí)要考慮放大器的特性。

(4)

(4)

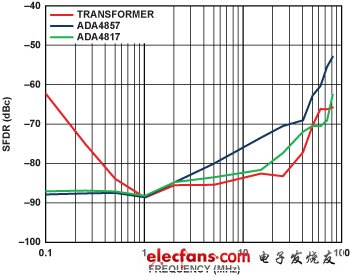

圖21比較了放大器在這種配置下的失真以及變壓器電路的失真。 RT1 = 143?, RT2 = 200 ?,RF = RG = 499?, CF = 5pF出于穩(wěn)定性和高頻濾波考慮--且 RL = 1k?. 在此ADA4817的性能可與變壓器在高頻下的性能相媲美,在最高70MHz時(shí),其SFDR可維持在優(yōu)于-70dBc的水平。與變壓器相比,兩個(gè)運(yùn)算放大器都能維持出色的低頻保真。

圖21. DAC、ADA4817和ADA4857的失真 VO = 500 mV p-p

本文討論了將低失真、低噪聲、高速放大器用作DAC緩沖器的一些優(yōu)勢(shì),并將其性能與變壓器進(jìn)行了比較。同時(shí)比較了采用兩種不同架構(gòu)的三類應(yīng)用電路。數(shù)據(jù)顯示,放大器在頻率低于1MHz時(shí)的性能優(yōu)于變壓器,在頻率不超過(guò)80 MHz時(shí),非常接近變壓器。在權(quán)衡考慮功耗和失真時(shí),放大器的選擇非常重要。