摘 要: 介紹了一種新的實時工業以太網總線技術EtherCAT,該工業以太網技術的高度實時性、靈活的拓撲結構、簡單的配置方法、技術的開放性等能有效緩解傳統以太網總線技術傳輸數據量小、實時性不高、通信接口不統一帶來的工業控制領域瓶頸問題。從EtherCAT的運行原理及其從站硬件電路設計所需芯片選型入手,對芯片的選擇以及外圍電路設計進行了詳細的描述。通過對幾種實時工業以太網通信技術的比較證明了該種實時工業以太網技術的數據傳輸的高速性。

關鍵詞: EtherCAT;PHY芯片;從站控制器;硬件電路

0 引言

隨著伺服控制系統日益復雜,傳統的現場總線技術已經無法給伺服控制領域帶來飛躍性的成就。因此,國內外公司紛紛提出其他工業以太網協議以改善這種情況,其中德國Beckhoff開發的EtherCAT以其卓越的性能及基于普通以太網標準的特點,逐漸成為伺服控制總線技術的主流。因此,深入研究EtherCAT并將其實際應用于伺服控制領域具有重要意義。

1 EtherCAT原理

EtherCAT采用主從式通信結構。主站向各個從站發送以太網數據幀,數據幀經過各個從站時經從站分析其中的指令進行數據的提取或插入從站自身的數據,并將工作計數器(Working Counter,WKC)更新。最終與主站事先設置的預期WKC值作比較,以判斷是否經過了所有的從站并被正確處理。由于從站對數據幀的接收與編碼及轉發、數據的提取與插入都是通過硬件完成,所以數據幀在每個從站停留的時間極小,保證了EtherCAT的實時性。經過最后一個從站處理后的數據幀將返回主站,主站接收并處理后,一次通信完成[1]。這種通信方式不會引起通信通路的堵塞,可保證網絡的實時性和正確性。整個通信過程如圖1。

2 EtherCAT從站硬件設計

凡是能夠發送和接收以太網數據幀的設備都可以作為主站,而且主站功能完全由軟件實現[1]。從站的建設則需要專用的集成電路搭建,這也是本文研究的重點。

2.1 EtherCAT從站硬件結構

根據DSP是否支持EtherCAT,相應的設計方法也不同。

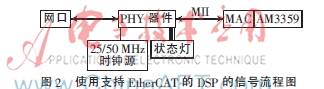

如果使用DSP支持EtherCAT,如TI的AM3359,則信號流程圖如圖2。

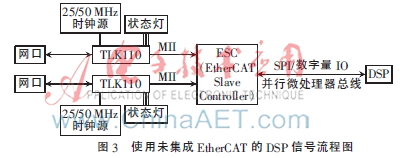

但是目前更多的芯片內部并沒有集成EtherCAT模塊,在這些芯片上實現性能更加優異的EtherCAT正是本文所要研究的重點。使用未集成EtherCAT模塊的DSP建立從站硬件的信號流程圖如圖3所示[1]。

2.2 EtherCAT從站硬件芯片選擇

目前常用的從站硬件建設方法是使用德國Beckhoff公司提供的從站控制器(EtherCAT Slave Controller,ESC),常用的兩種從站控制專用芯片如表1所示[1]。

如果只有一個從站,則只需要一個MII端口。但是考慮到EtherCAT可以完成一個主站和多個從站的通信,為長遠考慮,選擇ET1100。ET1100使用MII接口時,對外接的PHY器件特別是其時鐘源有如下要求:

(1)PHY芯片和ET1100使用同一個時鐘源;

(2)PHY的TX_CLK信號和PHY的輸入時鐘之間的相位關系必須固定,最大允許5 ns的抖動;

(3)ET1100不使用PHY的TX_CLK信號,以省略ET1100內部的發送FIFO。

符合以上要求的PHY芯片很多,這里選擇TI公司的TLK110。

TLK110是單口10M/100M以太網物理層信號收發器,它支持標準MII接口,供電靈活,3.3 V獨立供電,也可以使用3.3 V/1.5 V聯合供電。功耗低,小于205 mW,使用25 MHz時鐘源。

2.3 EtherCAT從站硬件電路設計

采用的網口為普通網口,給TLK110傳遞的信號為兩組差分信號RD+/RD-和TD+/TD-。另外C_YLW/C_GRN信號燈主要用來判別網口是否正確連接和是否正常工作。TLK110通過MII接口與ET1100通信,其外圍電路設計如圖4。

MII_RXD[3:0]要使用2.2 kΩ的電阻上拉到3.3 V,因為TLK110的RXD管腳發送網絡信號給ET1100,使用上拉一方面可保證發送的信號不存在0或1以外的不確定狀態,即信號的確定性;另一方面,管腳上拉提供驅動能力,確保信號能到達ET1100。該PHY芯片管腳所接信號既有模擬信號,又有數字信號,在做PCB設計時容易引起數模串擾。所以在設計原理圖時將22號管腳經0 Ω電阻直接接到數字電源。同樣的方法處理15、19的地信號,從而保證TLK110所接均為數字信號,便于PCB設計同時避免模數信號串擾引發問題。TLK110的時鐘信號由ET1100提供,輸入到TLK110的XI管腳,而復位信號則由FPGA提供。要實現EtherCAT的多從站通信,需要兩塊TLK110芯片,另一塊芯片與該TLK110接線一致。

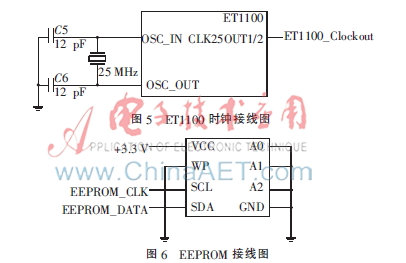

本設計中,ET1100通過SPI接口與FPGA相連,同時通過MII接口連接兩個PHY芯片,并給PHY器件提供時鐘信號。由于ET1100自身沒有如EEPROM一類的存儲器件,所以選擇帶I2C接口的EEPROM來存儲設備的配置信息。圖5、6為ET1100的時鐘接線圖以及外掛EEPROM接線圖。

ET1100的I/O管腳可以使用3.3 V或5 V供電,并且該電壓值決定所有輸入輸出信號的電壓。一般選擇 3.3 V電壓供電。所有VCCIO和GNDIO之間都要接濾波電容。ET1100內核和PLL供電電壓為2.5 V,既可由外部提供也可由芯片內部通過轉換I/O口電壓得到。同時,VCCcore和GNDcore之間也需要使用濾波電容連接。如圖7。

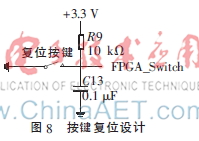

該芯片復位為低電平復位,復位信號來源為FPGA,按鍵復位設計如圖8。

一般情況下FPGA_Switch置于高電平,需要復位時手動按下復位按鍵,FPGA_Switch變成低電平,此時FPGA經內部編程實現給其他芯片提供低平復位信號。

在本設計中,ET1100不直接與DSP相連,信號流程圖如圖9所示。

ESC與DSP之間可通過過程數據接口(Process Data Interface,PDI)連接,一般使用的有數字量I/O接口、SPI從站接口、并行微處理器總線接口。由于SPI接口占用的管腳比較少,其他的管腳可以作為普通的I/O口使用,包括16個通用數字輸入引腳和16個通用數字輸出引腳[1],所以采用SPI接口連接ESC與DSP。一般情況下,ET1100直接與DSP相連,但是這里在中間加入FPGA,雖然運行時間會因此增加幾微秒,但是由于硬件電路的可變更性比較低,作為實驗板卡的設計,要盡量考慮功能的豐富性以及使用的長遠性,所以這里將網口數據通過FPGA,以便于日后需要作出更改時,不必更改硬件線路,只需改寫FPGA程序。另外,加入FPGA便于引出測試點,可隨時監測傳輸的數據。

3 實驗性能分析

在表2的實驗條件下,對各個以太網協議傳輸速率進行比較,得到如表3[2]所示數據。

表3中的數據顯示各個實時工業以太網協議在同一實驗條件下的數據傳輸時間。由表中數據明顯可以看出,EtherCAT傳輸等量數據所用時間遠遠小于其他以太網協議,即EtherCAT的高速性相對突出。

4 結論

本文針對傳統以太網總線技術存在的短板,介紹了一種新的實時工業以太網技術EtherCAT。通過對EtherCAT運行原理的分析,詳細描述了如何利用不含EtherCAT控制模塊的DSP搭建EtherCAT從站硬件,包括從站硬件設計中的芯片選型以及電路設計,并通過比較各個工業以太網協議的數據傳輸速率,最終證明了EtherCAT高速傳輸方面的卓越性能。但是由于時間、實驗條件以及個人能力所限,對EtherCAT的探究目前僅限于實驗室中。如何將這種優秀的工業以太網技術應用到實際工業控制領域中需要進行更加深入的研究。

參考文獻

[1] 郇極,劉艷強.工業以太網現場總線EtherCAT驅動程序設計及應用[M].北京:北京航空航天大學出版社,2010.

[2] ETG. EtherCAT_Introduction_CN[EB/OL].(2012-09-20)[2014-02-26]. http://www.ethercat.org.cn.