張學軍,溫 煒

( 南京郵電大學 電子科學與工程學院,江蘇 南京 210003)

摘要:提取腦電信號是進行腦電信號分析的第一步,其中關鍵的技術之一就是信號調理電路的設計。腦電信號是極其微弱的生物信號,對噪聲極為敏感、對放大器性能要求較高。設計了預處理電路中的放大以及濾波電路,具有元器件簡單、價格低廉等特點。測試結果表明,該系統具有良好的放大及濾波性能。

關鍵詞:腦電信號;放大電路;濾波器

0引言

生物科學尤其是腦科學的研究已經進入高速發展的時期,現階段用于腦電信號分析的儀器設備通常是腦磁圖儀或者腦電圖機。而腦磁圖儀因其體積龐大、價格昂貴,只能被專業機構使用。腦電圖機的普及相對容易,更易被用戶接受。

腦電圖機的性能、價格、體積、是否易于普及等特性,在很大程度上取決于腦電信號調理電路的設計,這也是腦電圖機最為關鍵的技術之一。

腦電信號(EEG)是極其微弱的生物信號,頻率集中在0.5~100 Hz,幅值只有5~100 μV[1]。因此EEG信號極易被淹沒在噪聲之中。噪聲包括外部噪聲,如50 Hz工頻干擾、環境中高壓電源的噪聲、人體與電流耦合的噪聲等;以及內部噪聲,如電極引出信號時的噪聲、元器件內部的熱噪聲等。此外,小信號的放大也是難點之一。要將EEG信號放大至能被A/D轉化器所識別的大小,整個系統至少需要達到上萬倍的增益。腦電信號調理電路的主要任務就是對腦電信號進行濾噪及放大。

1系統總體設計

系統總體設計思路是保證系統具有“三高兩低”的特性,即高增益、高輸入阻抗、高共模抑制比和低噪聲、低漂移[2]。該系統電路分為放大電路、濾波電路以及電平抬升電路。由于腦電信號的特殊性質,為避免噪聲影響,EEG放大無法一次到位,需分2~3級逐級放大。濾波電路用來濾除0.5 Hz以下以及100 Hz以上的信號,同時濾除50 Hz的工頻干擾噪聲[3]。調理電路總體設計框圖如圖1所示。

2調理電路設計

按照總體框圖中各個模塊分部分闡述具體電路的設計工作。

2.1EEG輸入

國際上把頭皮電極定位的標準方法稱為10-12系統法。本系統采用單通道,將兩片醫用電極分別貼在太陽穴的兩側,第三片電極貼在耳垂處起到接地的作用。采集到的頭皮信號同步送入下一級差分放大電路。

2.2放大電路

2.2.1前置放大電路

該電路是除了電極之外首先接收并處理腦電信號的模塊。腦電信號只有μV級別,需要放大上萬倍。但是初次放大不宜過大,此時噪聲沒有被濾除,它對EEG信號的影響極大,過度放大極易使噪聲淹沒有效信息。由此考慮,設置初級放大的增益為20,器件選取AD620。AD620能夠滿足放大需求,并且具有抗干擾能力、功耗低、價格便宜等特點[4]。其增益G的計算公式為:

G=49.4 kΩ/RG+1(1)

外接電阻RG取2~3 kΩ,此時G約為20,共模抑制比約為110 dB。

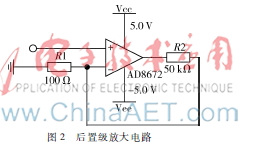

2.2.2后級放大電路

經過初次放大,放大增益仍不能滿足設計需求,需要第二級放大。后級放大電路設計增益大約為500倍,如式(2)所示,電路如圖2所示。

其增益G的值與R1和R2有關,將R2設置為滑動變阻器即可動態調節增益。不同受試者或同一受試者處于不同狀態時,其腦電信號振幅會有所差異,可適時調節。

2.3濾波電路

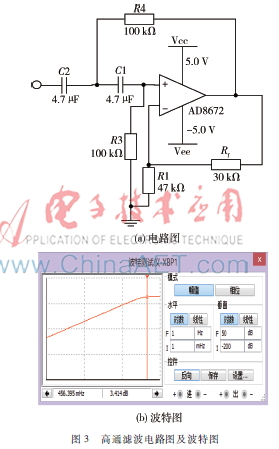

2.3.1高通濾波電路

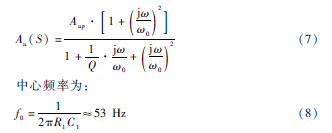

此電路負責濾除0.5 Hz以下的信號,采用了壓控電壓源二階高通濾波器。其傳遞函數為:

其中,C1=C2=4.7 μF,R1=47 kΩ,Rf(R2)=30 kΩ,R3=R4=100 kΩ,得到截止頻率為:

電路圖以及波特圖如圖3所示。

2.3.2低通濾波電路

腦電信號的主要頻率集中在100 Hz以內,因此可將大于100 Hz的信號直接濾除,該電路傳遞函數為:

電路圖以及波特圖如圖4所示。

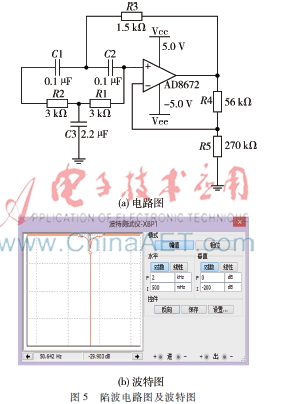

2.3.3陷波電路

我國市電電壓的頻率為50 Hz,它同樣會對設備造成嚴重的干擾,這一干擾稱為工頻干擾,抑制它的電路是陷波電路。通常情況下,采用的解決方案是“雙T”陷波電路[5]。傳遞函數為:

電路圖以及波特圖如圖5所示。

2.4電平抬升電路

A/D轉化器能識別的標準電壓大多在0~3.3 V,呈單極性。保證EEG信號負電壓的部分不受損失,需要將其抬升至標準電壓內。電平抬升電路如圖6所示。

調理電路設計并制作完成后,對系統性能進行測試,結果如下。

3.1低通濾波電路測試

設計的截止頻率為100 Hz,測試時,維持濾波器輸出端的電壓為10 V,改變輸入信號的頻率,結果如表1所示。

電壓在100 Hz截止頻率之后出現快速的衰減,在95 Hz的時候仍能保持較高的峰峰值。

3.2陷波電路測試

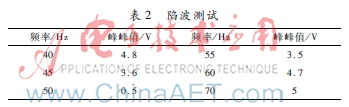

測試方式與上文相同,結果如表2所示。

3.3系統整體測試

本系統前置放大電路實際增益為19,后級放大為578,總體增益為10 982倍,達到設計需求。

4結論

本文設計了腦電信號調理電路,完成了信號的頭皮采集、放大、濾波等預處理工作,并對該調理電路的性能做了分析。總體上達到了設計目標。該電路仍有可改進的地方,如加入緩沖電路、右腿驅動電路等。

參考文獻

[1] 陳長偉,谷秀鳳. 備考江蘇省計算機等級考試(二級VFP)策略[J].經濟研究導刊,2010(4):8586.

[2] 鐘文華. 基于ARM的腦電信號采集系統[J]. 電子設計工程,2008(2) :13 15.

[3] 謝宏,李亞男,夏斌. 基于ADS1299的可穿戴式腦電信號采集系統前端設計[J].電子技術應用,2014,40(3):8689.

[4] 李永建,李舜酩,郝青青,等. 微弱振動信號自適應采集系統設計[J]. 現代電子技,2009,32(5):187 190.

[5] 史駿,彭靜玉. 基于雙T網絡的50Hz陷波電路設汁[J]. 科技信息,2011(21):121122.