魏智偉

(重慶郵電大學,重慶400065)

摘要:在使用Digital Signal Processor (DSP)芯片進行數字信號處理時,由于數據量大,線程較多,通常采用多片DSP協同處理。本文旨在研究DSP間數據和信息傳輸的實現,并以三片TI的 TMS320C6474芯片為例,基于SRIO協議,設計一種傳輸架構,實現了DSP間的數據傳輸。最終實現DSP間2.520 Gb/s的數據傳輸速率,為理論值的50.40%,但如果除去線程調度和DSP間同步所用時間,其SRIO接口的數據傳輸速率可達到3.886 Gb/s,為理論值的77.72%。該設計具有較大的通用性,對其他同類型的芯片間的數據傳輸設計具有極大的參考性。

關鍵詞:多核;DSP;SRIO;DSP間數據傳輸

中圖分類號:TP368.2文獻標識碼:ADOI: 10.19358/j.issn.1674-7720.2017.04.011

引用格式:魏智偉.多核DSP間基于SRIO數據傳輸的設計與實現[J].微型機與應用,2017,36(4):36-39.

0引言

伴隨著DSP所需處理的數據量和開發的功能模塊的增多,單片DSP運行的進程數增多,負載過大,系統越來越難以滿足實時處理的要求。如果選擇多片DSP協同運行,不僅可以減少單片DSP的負載,提高系統的處理性能和響應速度,從而達到實時處理的要求,還能進行更多功能模塊的開發,對于數字信號處理系統來說定是有益的。但多片DSP進行協同運行時,DSP間需要設計完成數據交互的功能。本文依據Rapid IO協議的標準,結合TI的TMS320C6474芯片的特點,在Digital Signal Processor_Basic Input Output System(DSP_BIOS)的開發平臺上,設計和實現了多核DSP間的數據傳輸。本文首先介紹了該設計所需的各個功能模塊,然后闡述整體設計的流程和具體實現的方式,最后對DSP間數據傳輸性能進行了測試。

1DSP間通信所需功能模塊簡介

1.1Mailbox(郵箱)

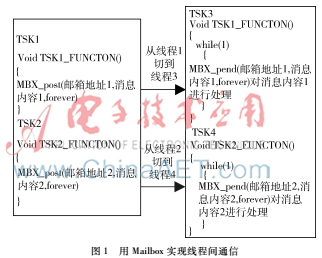

基于DSP_BIOS的開發平臺,TI提供了一個Mailbox(MBX)模塊,開發者可以通過TI的用戶接口函數來進行管理,使用該模塊。Mailbox用來圖1用Mailbox實現線程間通信實現DSP內部的同一個核內的不同進程(TSK)間的相互通信[1]。MBX_post()用于發送端,MBX_pend()用于接收端,其實現示例如圖1所示。

1.2Semaphore(信號通信)

TI提供了一個Semaphore[2]模塊,該模塊可以用于管理對共享資源的訪問。其訪問模式有三種:直接模式,間接模式,綜合模式。本文采用的是直接模式:讀取寄存器DIRECT的值,如果DIRECT的值為1,則表明該共享資源可用,允許訪問,并獲得該信號量;反之如果DIRECT的值為0,則表明該共享資源正在被其他進程訪問。當對共享資源操作完成后,需要對DIRECT寫1,以釋放對該資源使用的權利。

1.3Rapid IO

1.3.1Rapid IO簡介

Rapid IO協議是一個開放的點對點分組交換標準,是面向嵌入式系統開發提出的高可靠、高性能、基于包交換的互聯技術[3],傳輸速率能達到1 Gb/s以上。其最主要的特點包括:(1)有錯誤檢測機制; (2)低負載高帶寬;(3)引腳少[4]。

1.3.2Rapid IO架構

SRIO總線是一種開放式的基于包交換的高速串行標準總線[5],Rapid IO協議采用三層分級體系結構:

(1)邏輯層:規定了端點間傳輸的協議和包格式。

(2)傳輸層:定義了在系統中傳輸的包所需的路由信息。

(3)物理層:包含了硬件級接口的信息,比如電氣特性、錯誤數據管理、基本數據流控制。

1.3.3SRIO包結構

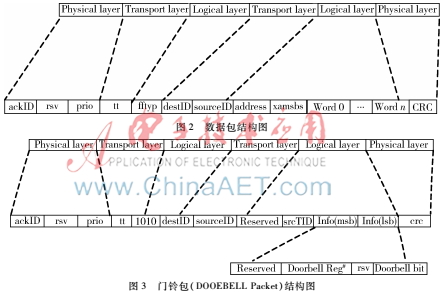

在SRIO的包結構中,包的種類有很多,主要用到的為數據包和門鈴包。數據包用于在源地址和目的地址間進行數據傳輸,其結構如圖2所示。門鈴包主要用于觸發相應的中斷,通知相應DSP的某個核進入中斷響應函數,執行相應的操作,但門鈴包不攜帶數據信息,其門鈴包的結構如圖3所示。

其中包結構各個段的含義是:AckID:交換結構期間將使用控制符號來確認是哪一個包;Prio:表明該包的優先級;tt:指定Device ID是用8 bit或16 bit表示;fftyp:表示包的類型;destID:包傳送的目的地址ID;sourceID:發送包的源地址ID;CRC:包結構的校驗保護;Info:門鈴中斷觸發控制。

1.3.4Rapid IO包傳輸

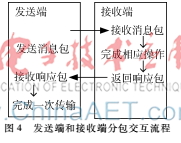

包結構(packets)是SRIO傳輸兩個端點之間傳輸的單位,其傳輸是基于請求包和響應包。圖4發送端和接收端分包交互流程

其一次數據傳輸流程為:發送發起端產生一個請求包給接收端,接收端收到后返還一個響應包給發送發起端[6]。圖4表明了發送端和接收端的包交互流程。

2DSP間通信的設計與實現

2.1資源的配置

2.1.1SRIO端口連接

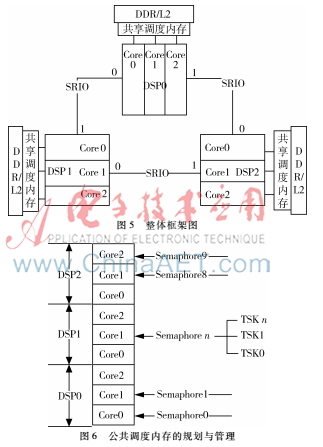

每片TMS320C6474芯片有兩個SRIO實體端口(分別命名為Port0,Port1),將其分別與另外兩片DSP的任意一端口相連,如圖5所示。通過該連接,可以保證任意一片DSP能與其他兩片DSP直接連接。當發送端DSP和接收端DSP都已確定時,相應SRIO端口的選擇也就確定了。

2.1.2DDR共享內存的分配與管理

每塊DSP上都外掛一片DDR存儲器。DSP的任意一個核Core0、Core1、Core2都能訪問該存儲器(TMS320C6474 為三核處理器,將三個核依次命名為Core0、Core1、Core2)。在DSP0,DSP1,DSP2的DDR存儲器里指定一塊內存用于存儲DSP間任務調度的信息(以下稱該段內存為共享調度內存),如圖5所示。每片DSP上分配的公共調度內存的規劃與管理如圖6所示。對每個DSP三個核的內存分別分配一個Semaphore(信號通信)用于管理對接收端DSP的共享調度內存的訪問。

2.1.3中斷的分配與運用

當發送端將消息發送給接收端后,通知接收端相應的核來處理該消息。此次設計的方案是通過SRIO口傳輸門鈴包(DOOEBELL Packet),門鈴包攜帶接收端相應核的信息, 觸發接收端相應核的中斷。

當發送端發送DOORBELL包時,此包被用作初始化CPU中斷,包結構中INFO段表明相關DOORBELL寄存器的相關中斷位被設置,如圖3所示。一個DSP有4個DOOEBELL寄存器,每個寄存器有16 bit,有64個中斷源產生中斷。通過ICR(Interrupt Condition Routing)寄存器,可以將每位路由給任意核。本文將DOORBELL寄存器的最低的三位分別分配給DSP的三個核(Core0,Core1,Core2)。即若DOOEBELL的最低位為1,則DSP的Coer0響應該中斷。

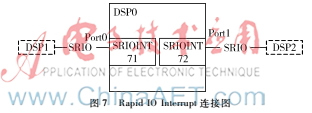

每個DSP都有兩個SRIO口,如圖5所示,前面已經將DSP互連的SRIO口進行了編號(0,1),按照SRIO口的編號(0,1)分別分配以DOOEBELL 0和DOOEBELL 1寄存器,DOOEBELL 0和DOORBELL 1寄存器又分別映射到SRIO的兩個中斷通道(71~RapidIO Interrupt(2n),72~ RapidIO Interrupt(2n+1)),將此兩個中斷分別分配給兩個SRIO口,使之分別響應SRIO口的中斷。該Rapid IO Interrupt主要用于判斷發送端的DSP的編號。如圖7所示,接收端為DSP0,若中斷通道71~RIOINT被觸發,則判斷發送端為DSP1,若中斷通道72~RIOINT被觸發,則判斷發送端為DSP2。

通過以上中斷的配置,可以保證發送端的任意DSP都能通過DOOEBELL消息包通知到消息接收端的任意核,同時接收端也能判斷出發送端為哪個DSP。

2.2設計思路與具體實現

2.2.1設計思路

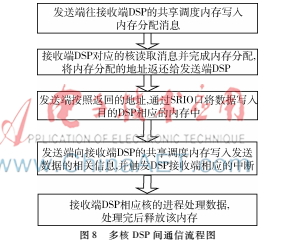

實現多核DSP間的數據交互主要完成兩方面的工作:(1)實現數據的搬移;(2)通知接收端的DSP數據存儲的位置和長度。其實現流程圖如圖8所示。

2.2.2具體實現流程

(1)SRIO初始化。①SRIO電源模塊的初始化:對SRIO相關的模塊提供電源。②SRIO的SERDES模塊初始化:配置PLL,配置RX0、TX0和TX1、TX1的傳輸通道,配置SRIO的端口0和1。③檢查SRIO口是否配置完成。

(2)選擇SRIO端口。根據發送端的DSP和接收端的DSP決定選擇SRIO口,即選擇數據傳輸的物理鏈路。

(3)獲取向接收端的共享調度內存寫入消息的信號量。通過Semaphore(信號通信)管理不同發送端對接收端DSP的共享調度內存的訪問,若該信號量被占用,則一直等待該信號被釋放。

(4)通過SRIO口傳輸數據包。配置Load/Store Register完成消息包的組成。其關鍵配置有:配置LSUn_REG2中的DSP Address,完成待傳輸數據(payload)的源地址和目的地址的配置;配置LSUn_REG3中的Byte_count完成待傳輸數據的長度;配置LSUn_REG5中的Packet Type完成包種類的配置。配置完成后,使能傳輸。其Load/Store Register相應字段的配置會映射到數據包中,待傳輸數據通過SRIO口存到了公共調度內存中。

(5)通過SRIO口傳輸DOOEBELL包:該包用于通知接收端DSP的相應核的共享調度內存有消息待處理。通過對LSUn_REG5的Drbll Info段進行配置,使之映射到DOORBELLn_ICRR寄存器中,本文將DOOEBELLn_ICRR的第0位、第1位和第2位,通過ICR(Interrupt Condition Routing)寄存器使之分別路由到核0、核1、核2。則通過DOOEBELL包就能在接收端DSP相應的核上產生中斷。第(2)步已經獲得了相應的SRIO的端口號,通過SRIO端口號為0或1決定DOORBELLn_ICRR為DOORBELL0_ICRR或DOORBELL1_ICRR。該DOORBELL0_ICRR和DOORBELL1_ICRR分別對應著接收端DSP相應核上的兩個SRIO_INT中斷。在2.1.3節中已經介紹,借此來判斷發送端的DSP的編號。由此接收端能判斷出數據在共享調度內存中的存儲位置,如圖9所示。以發送端為DSP0_Core0、接收端為DSP1_Core1為例,其消息應存儲在DSP1的共享內存中的DSP0、Core1段。

(6)接收端DSP相應的核讀取共享調度內存的數據,解析收到的消息并通過Mailbox(郵箱)模塊,在接收端DSP相應的核內進行核內線程調度,觸發相應的任務。

(7)接收端DSP執行完相應的任務后,給發送端返回相應的數據,發送端DSP和Core的編號都會在傳輸的過程中保存,所以接收端往發送端返回消息時按照前幾個步驟的逆過程進行數據傳輸。

通過以上幾個步驟后,多核DSP間的數據傳輸已經實現。

3數據傳輸測試

本文對多核DSP間的數據傳輸進行測試[7],SRIO口的工作速率設置為3.125 Gb/s,經過物理層8B/10B編碼,數據包實際傳輸速率為2.5 Gb/s,使用兩個1x通道,理論傳輸數據為5 Gb/s。

數據傳輸正確性的測試:從DSP0Core0發送2k次的數據給DSP1Core2,DSP1Core2收到數據后將數據轉發給DSP2Core1,DSP2Core1收到數據后再發送回DSP0Core0,DSP0Core0最后將收到的數據與最初發送的數據進行對比,檢測數據有無錯誤。本文采用每隔1 s發送一次數據,測試一星期未發現出錯。

傳輸性能的測試:任意選取兩片DSP的任意核進行不同數據長度的回環測試。例如數據從DSP1發送至DSP2,DSP2收到數據后將數據返回給DSP1。從DSP1剛開始發送數據和剛接收完數據后分別利用_itoll(TSCH,TSCL)函數獲取CPU的Cycle值,計算兩次值之差,即可測出速率[8]。

通過數據分析可以得出,數據的傳輸速率為2.520 Gb/s左右,為理論值的50.4%。但傳輸長度為64 B時,傳輸的數據較少,可近似為線程調度和DSP間同步所需的時間,若將傳輸32 000 B的時間減去傳輸64 B時間(線程調度和DSP間同步所需時間),再計算傳輸速率的值為3.886 Gb/s,為理論值的77.72%。由于數據包的組包和解包,以及DDR上讀取數據的開銷等,實際數據會小于理論值。

4結束語

本文在DSP_BIOS操作平臺上,基于Rapid IO協議,實現了多核DSP間的數據傳輸。此次設計不僅適用于2個多核DSP間的數據傳輸,同時也適用于3個甚至3個以上多核DSP間的數據傳輸。該架構能協同多個DSP進行大量的數據處理,相對減少了單個DSP處理的時延和負擔,提高了系統的處理能力和響應速度,對數字信號處理系統的發展具有一定的推動作用。

參考文獻

[1] Texas Instruments Group. TMS320 DSP/BIOS v5.42 User’s Guide (SPRU4231) [EB/OL].(2013-08-xx)[2016-09-20]http://www.ti.com.

[2] Texas Instruments Group. TMS320C6474 DSP Semaphore User’s Guide (SPRUG14)[EB/OL].(2016-09-20)[200810xx]http://www.ti.com.

[3] 陳婷,岳強,汪洋.FPGA和DSP間基于SRIO的高速通信系統設計[J].單片機與嵌入式系統應用,2016(3):37-40.

[4] Texas Instruments Group. TMS320C6474 DSP Serial Rapid IO(SRIO) User’s Guide (SPRUG230) [EB/OL].(2011-10-xx)[20160920]http://www.ti.com.

[5] 王磊,王輝球.基于高速串行總線SRIO的數據傳輸[J].電子制作,2015(5):16-18.

[6] 黃克武,吳海洲.基于TMS320C6455的高速SRIO接口設計[J].電子測量技術,2008,31(9) :143147.

[7] 馮超,張濤.TMS320C6678高速串行接口的傳輸性能研究[J].單片機與嵌入式系統應用,2015,15(11):52-55.

[8] 侯普.基于TI KeyStoneⅡ多核DSP技術的研究與運用LTEA基帶板處理板設計與實現[D].北京:北京郵電大學,2015.