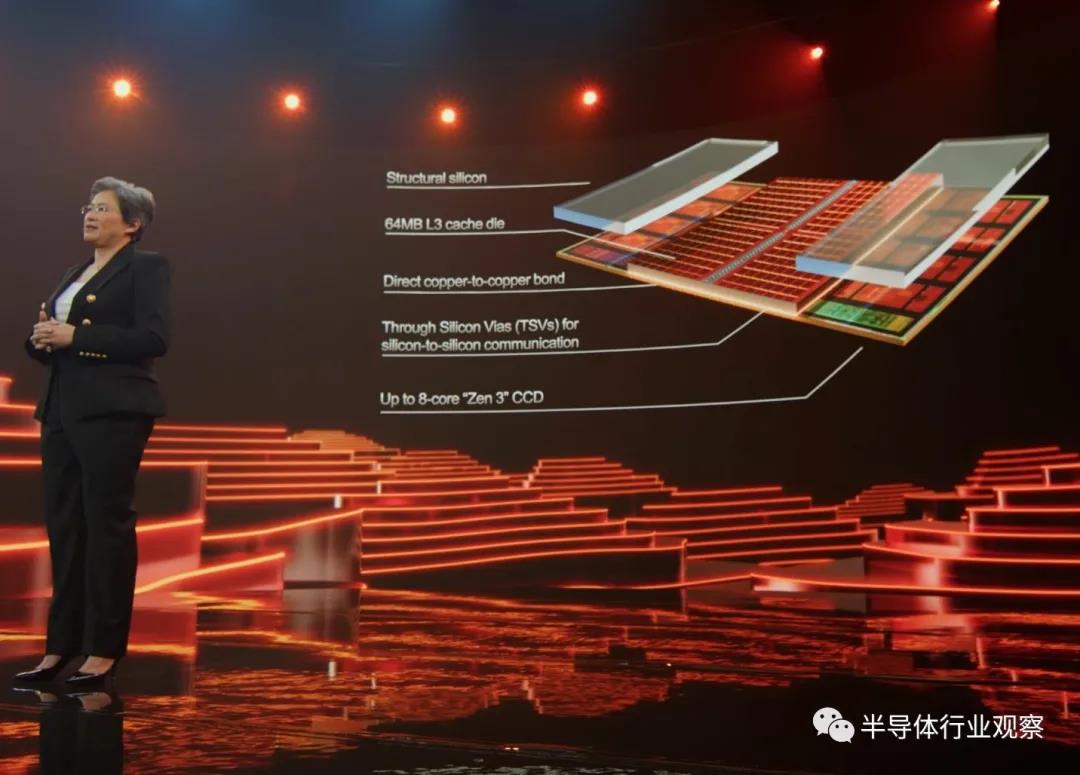

在上周舉辦的Computex上,AMD發布了其實驗性的產品,即基于3D Chiplet技術的3D V-Cache。該技術使用臺積電的3D Fabric先進封裝技術,成功地將包含有64MB L3 Cache的chiplet以3D堆疊的形式與處理器封裝在了一起。

在AMD展示的概念芯片中,處理器芯片是Ryzen 5000,其原本的處理器Chiplet中就帶有32 MB L3 Cache,而在和64 MB的3D V-Cache做3D封裝后,每個Ryzen 5000 Chiplet可以訪問總共96 MB的L3 Cache。而在每個包含多個Ryzen 5000 Chiplet的處理器中,則最多可以訪問高達192MB的L3 Cache。

先進封裝已經成為推動處理器性能提升的主要動力

隨著半導體工藝節點越來越接近物理極限,每一代半導體工藝節點提升對于芯片性能帶來的收益也越來越小,通常在15%左右。而在AMD發布的帶有3D V-Cache的處理器則在工藝不變(仍然使用7nm臺積電工藝)的情況下,在3D游戲等對于處理器性能有高需求的應用場景中實現了約15%的性能提升。這一點說明先進封裝在今天已經能實現原來需要半導體工藝節點前進整整一代才能實現的性能提升;而在未來隨著半導體工藝越來越接近極限,每一代工藝帶來的性能增益越來越小,先進封裝可望取代半導體工藝成為芯片性能提升的主要推動力。

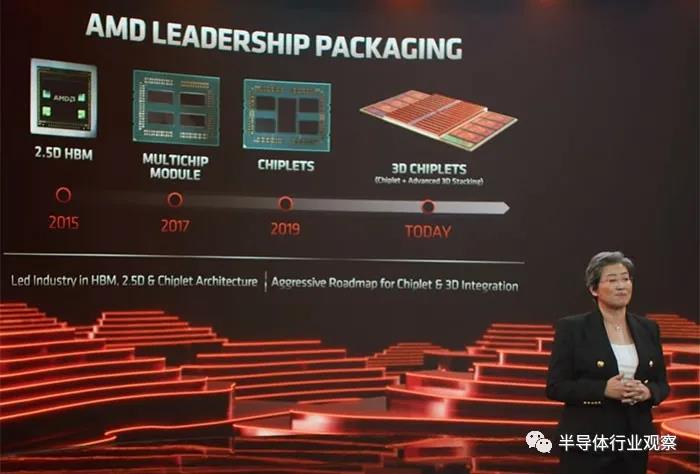

而在先進封裝領域,AMD已經有了多年的積累,從2015年開始使用HBM技術,到2019年推出使用chiplet的產品,到今天推出3D chiplet,每一步都可以看見AMD對于先進封裝領域投入的決心。

在先進封裝領域,有兩條由應用驅動的技術路徑。一條的主要訴求是提升互聯密度,從而解決芯片之間的通信帶寬,其代表產品就是基于2.5D/3D高級封裝的HBM DRAM接口標準,使用HBM可以將DRAM和處理器(CPU,GPU以及其他ASIC)之間的通信帶寬大大提升,從而緩解這些處理器的內存墻問題。目前,HBM已經成為高端GPU的標配,同時也應用于不少針對云端處理的AI芯片(例如谷歌的TPU)中。

除此之外,另一條技術路徑是chiplet,即在封裝系統里面不再使用少量的大芯片做集成,而是改用數量更多但是尺寸更小的芯片粒(chiplet)作為基本單位。使用chiplet的第一個優點是提升了良率,如果使用大芯片的話,如果在芯片的晶圓面積上出現瑕疵,那么整個芯片就有了瑕疵,無法作為良品使用;但是如果把同樣面積的芯片拆分為多個chiplet,那么出現瑕疵的話就僅僅是瑕疵出現的那個chiplet無法使用,而其他chiplet則不受影響,這樣就提升了良率,而這對于良率存在挑戰的先進半導體工藝至關重要。Chiplet另外的潛力在于可以實現更靈活的異構集成,在同一封裝系統中不同的chiplet可以使用不同的半導體工藝實現,從而進一步降低成本(例如某些對于邏輯性能需求不高的模組可以使用成熟工藝)并提升性能。

而這次AMD的3D Chiplet則是把兩條先進封裝的技術路線匯合到了一起。AMD發布的3D V-Cache中,首先處理器和堆疊的L3 Cache都使用了chiplet,另外在3D V-Cache和處理器chiplet之間,也使用了先進封裝帶來的高密度互聯,其互聯密度較2D chiplet高兩百多倍,相比傳統的3DIC技術也能提高15倍。我們認為,AMD將3D Chiplet投入商用對于先進封裝領域來說,將是類似HBM進入GPU這樣的里程碑式事件。

臺積電進一步鞏固在代工領域的地位

在AMD發布的3D chiplet背后,是臺積電的先進半導體工藝技術和先進封裝技術。臺積電作為同時掌握了最先進半導體工藝和封裝技術的代工廠,其全球最頂尖代工廠的地位得到了鞏固,同時其在先進技術領域也將變得更加強勢。

早在2019年的VLSI Symposium中,臺積電就發表了類似這次AMD 3D Chiplet的技術。臺積電把這個技術System on Integrated Chips(SOIC),其主要解決的就是進一步提升3D封裝中的互聯密度。傳統3DIC技術的連線密度受到bump尺寸的限制,從而限制了集成總線的帶寬和互聯成本。而臺積電SoIC技術一個關鍵優勢就是無須bump,只要將兩塊要堆疊的芯片的銅互聯做部分裸露并對準,之后即可通過熱處理工藝完成兩塊芯片的電路連接。這樣一來,兩塊堆疊芯片之間的走線密度以及信號傳輸功耗都可以大大改善。在今年的ISSCC中,臺積電又一次展示了SOIC技術,這次臺積電為該技術商用起了一個正式的名字(3DFabric),并且公布了更多互聯密度相關的數據,其互聯密度相比傳統的基于bump的3DIC技術可以提升16倍,該數據與AMD這次在Computex發布的相關數字(相比3DIC互聯密度提升15倍)也大體相符。

如前所述,隨著摩爾定律的半導體工藝節點提升接近極限,先進封裝技術將會慢慢接班半導體工藝節點而成為芯片性能提升的推動力。臺積電在擁有最先進半導體工藝的同時,也在先進封裝領域領跑全球,其在半導體代工領域的領導者地位將延續下去。于此同時,在AMD首發基于3DFabric的產品之后,預計在未來會有更多芯片設計公司跟進使用3DFabric來實現高性能芯片,從而進一步推廣下一代先進封裝技術的應用。

3D Chiplet在AI時代大有作為

我們認為,類似3D Chiplet的技術在AI時代將會有廣泛應用。

目前,人工智能已經成為推動半導體行業市場收入的重要引擎。基于神經網絡的人工智能需要強大的算力支撐其模型訓練和部署,因此高性能計算芯片在AI時代至關重要,這也是全球范圍內出現了不少AI芯片初創公司的原因。對于AI計算來說,內存訪問已經越來越成為性能的瓶頸,因此如何提升處理器(AI芯片)與存儲器之間的內存訪問速度和效率變得越來越重要。為了解決這個問題,目前云端AI芯片使用HBM DRAM配合大容量的片上SRAM已經成為標配(例如谷歌的TPU)。HBM DRAM和大容量SRAM缺一不可,其中HBM DRAM容量大,但是存取需要較大的延遲,因此常用來存儲系統調度算法中在未來可能會用到的數據;而SRAM的帶寬大于HBM,延時也較小,但是容量也遠小于DRAM,常用來存取在當前立即需要用到的數據。在人工智能領域,隨著GPT-3這樣的巨型模型越來越多,對于DRAM和SRAM容量的需求都越來越大,而SRAM擴容目前看來最有希望的方法之一就是使用類似3D Chiplet的技術,使用3D堆疊的方式來獲得更大的容量(如這次AMD在使用3D V-Cache后SRAM容量就擴大到了三倍),因此我們認為隨著臺積電的3DFabric技術進一步成熟,AI芯片很可能是下一個使用該技術的產品,并且隨著人工智能市場越來越大,AI芯片也將進一步將3D Chiplet帶向主流,同時使用HBM加3D Chiplet技術的芯片產品將會進入更多產品中獲得使用。