1 參數化

FPGA 設計的硬件語言Verilog中的參數化有兩種關鍵詞:define 和 paramerter,參數化的主要目的是代碼易維護、易移植和可讀性好。

Parameter關鍵詞類似于C語言中的形參可在其他模塊調用時實例化參數,這個參數在運行過程中不能修改,在編譯時就已經確定好了。

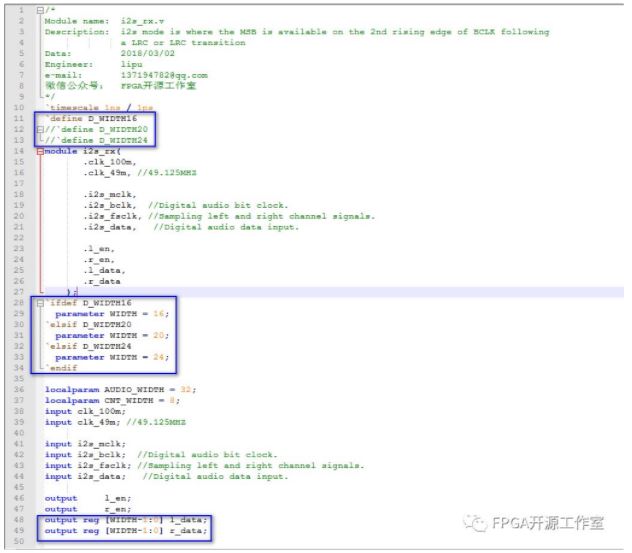

示例:

模塊引用如下:

方式一:

方式二:

第一種方式必須按照順序,而第二種方式可以順序顛倒。所以在參數化比較多的情況下,盡量采用第二種方式,以避免順序的錯亂。

Define關鍵詞類似于C語言中的define 。主要用于本地模塊的一些定義,例如狀態機。

示例:

2 條件編譯

一般情況下,Verilog HDL源程序中所有的行都將參加編譯。但是有時希望對其中的一部分內容只有在滿足條件才進行編譯,也就是對一部分內容指定編譯的條件,這就是“條件編譯”。

有時,希望當滿足條件時對一組語句進行編譯,而當條件不滿足是則編譯另一部分。

條件編譯命令有以下幾種形式:1) `ifdef 宏名 (標識符)程序段1`else程序段2`endif

2) `ifdef 宏名 (標識符)程序段1`endif

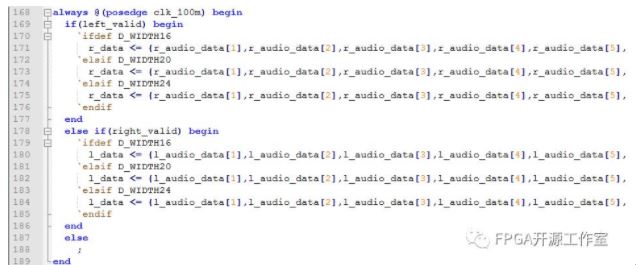

示例:

如上所示我們在寫I2S的時候會遇到不同位寬的I2s數據,這就意味著對于不同的數據模塊我們就要寫一個文件。

如果采用條件編譯就可以只寫一個文件。當需要修改時只需要修改`define D_WIDTH16

//`define D_WIDTH20

//`define D_WIDTH24

就可以完成不同i2s數據位寬的修改。

更多信息可以來這里獲取==>>電子技術應用-AET<<

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。