文章來源:芯智訊

原文鏈接:https://mp.weixin.qq.com/s/wSxSoqqRS1QmjZHLFyWd1A

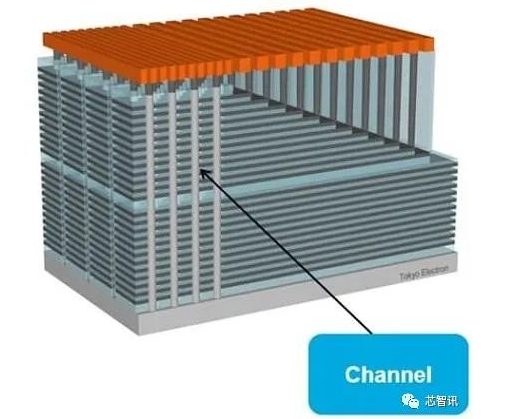

6月12日消息,日本半導體設備大廠東京電子(TEL)宣布,其等離子體蝕刻系統的開發和制造基地已經開發出一種創新的通孔蝕刻技術,可以用于堆疊超過400層的先進3D NAND Flash閃存芯片。開發團隊的新工藝首次將電介質蝕刻應用帶入低溫范圍,從而打造了一個具有極高蝕刻率的系統。

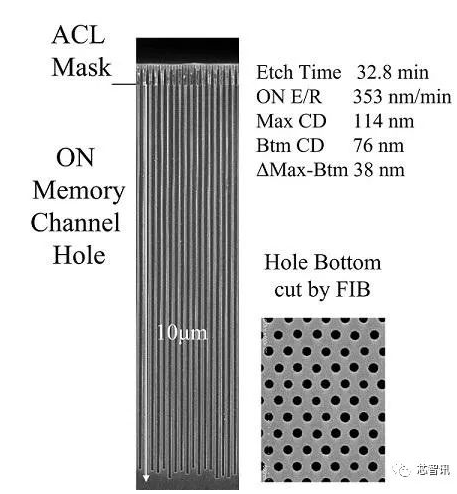

據介紹,這項創新的技術不僅能在短短33分鐘內完成10微米深度的高縱橫比蝕刻,縮減了耗時,而且蝕刻結構的幾何形狀相當明顯,也有助于制造更高容量的3D NAND閃存芯片。

東京電子還提供了蝕刻后的相關圖像,展示了開發的成果。其中包括顯示了蝕刻后通孔圖案的橫截面SEM圖像,以及孔底的FIB切割圖像,另外還有東京電子的3D NAND閃存芯片的一個案例。

東京電子預告稱,開發該項技術的團隊將于2023年6月11日至6月16日,在京都舉行的2023年超大規模集成電路技術和電路研討會(2023 VLSI)上發表最新的研究成果報告。據悉,VLSI是最負盛名的國際半導體研究會議之一,利用這一機會,東京電子將展示為半導體技術創新和全球環境所做的努力。

值得一提的是,今年也是東京電子成立60周年。東京電子認為這是一個新的轉型點,迎接未來的新挑戰,繼續為社會發展作出貢獻。

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。