5月11日消息,據wccftech報道,AMD最新的基于Zen 6內核架構的第六代EPYC Venice CPU的更多細節被曝光,除了將采用臺積電2nm制程,預計將擁有多達256個內核,緩存也將比上代的Turin提高了一倍。

更早之前的報道顯示,AMD的第六代EPYC Venice CPU將有兩種版本,一種是基于標準的Zen 6內核版本,另一種是更密集的Zen 6C內核版本。這些將出現在SP7和SP8插槽中,前者是高端解決方案,而后者則針對入門級服務器解決方案,該平臺將同時支持16和12通道內存。另外每個CCD據稱最多可包含128 MB的L3緩存(未確認是Zen 6還是Zen 6C)。

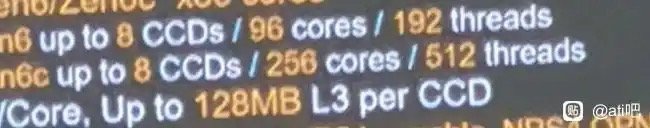

最新的來自百度貼吧及X平臺@Bionic_Squash 的爆料顯示,基于Zen 6內核版本的Venice CPU將擁有最多8個CCD,每個CCD包含12個Zen 6內核,即最多擁有96個內核和192個線程,中間還有多個IOD,這將進一步擴展這些服務器平臺上的I/O功能,TDP功耗約350-400W。

相比之下,Zen 6C內核版本的Venice CPU將擴展到256個內核和512個線程,TDP功耗將達600W。

EPYC 9006 "Venice" With Zen 6C: 256 Cores / 512 Threads / Up To 8 CCDs

EPYC 9005 "Turin" With Zen 5C: 192 Cores / 384 Threads / Up To 12 CCDs

EPYC 9006 "Venice" With Zen 5: 96 Cores / 192 Threads / Up To 8 CCDs

EPYC 9005 "Turin" With Zen 5: 96 Cores / 192 Threads / Up To 16 CCDs

根據AMD在今年4月15日公布的信息顯示,其第六代EPYC Venice CPU成為業界首款基于臺積電2nm(N2)制程工藝完成投片(tape out)的高性能計算(HPC)產品。這也是AMD首次拿下臺積電最新制程工藝的首發,而以往則都是由蘋果公司的芯片首發。根據預計,Venice CPU可能將會在明年某個時間點上市。