摘 要: 給出了DPLL的基本概念,闡述了DPLL的缺點,并結合最新的模擬鎖相" title="鎖相">鎖相和數字鎖相技術,提出了一種基于FPGA的全新鎖相倍頻系統的設計方法,簡單地介紹了設計的思路、原理及其算法,并對該方案的性能進行了分析,給出了仿真波形。

關鍵詞: DPLL FPGA 倍頻 分頻

隨著數字時代的到來,越來越多的領域采用集成電路來設計電路,FPGA/CPLD等EDA設計更為廣大硬件工程師所接受。其模塊化設計為設計人員帶來了很多方便,節約了系統的開發時間,使設計人員只需要調用這些模塊或者IP核,然后組合起來就可以實現一個簡單的功能。全數字鎖相環(DPLL)就是其中一個典型的例子。然而DPLL在應用時存在很多缺陷,例如鎖相時間長、捕捉帶窄等。為了避免這些缺點,本文設計了一種全新的相位跟蹤倍頻系統,有效地改善了DPLL的這些指標,并在項目中得到了良好的應用。

1 全數字鎖相環的概念

所謂全數字鎖相環路,就是環路部件全部數字化,采用數字鑒相器" title="鑒相器">鑒相器(DPD)、數字環路濾波器(DLF)、數控振蕩器(DCO)構成鎖相環路。典型全數字鎖相環的結構如圖1所示。它采用的鑒相器是導前-滯后型數字鑒相器。鑒相器在每一個周期內得到輸入時鐘的相位比本地估算時鐘相位超前或滯后的信息,這樣鑒相器的相位誤差輸出只有超前或滯后兩種狀態。將誤差相位的超前或滯后信息送到序列濾波器后,產生對DCO的“加”或“減”脈沖控制指令去改變DCO的時鐘周期,使本地估算時鐘的相位與輸入時鐘相位靠攏。

環路濾波器采用了K計數器。其功能就是對相位誤差序列計數即濾波,并輸出相應的進位脈沖或借位脈沖來調整I/D數控振蕩器輸出信號的相位,從而實現相位控制和鎖定。然而相位鎖定時間與相位抖動之間是一對矛盾體,K值取得大,對抑止噪聲有利,因為K值大,計數器對少量的噪聲干擾不可能計滿,所以不會有進位或借位脈沖輸出。但這樣捕捉帶會變小,而且加大了環路進入鎖定狀態的時間。反之,K值取得小,可以加速環路的入鎖,但K計數器會頻繁地產生進位或借位脈沖,從而導致相位抖動,增大了同步誤差,相應地對噪聲的抑制能力也隨之降低。因此對于一般的DPLL,選擇適當的K值很重要。

對于倍頻電路,目前大部分都是基于鎖相環技術開發的,因此不可避免地也會將鎖相環中設計存在的矛盾帶入倍頻設計中。即使系統倍頻的范圍很寬,但由于PLL的自身缺陷所帶來的頻譜純度差、抖動明顯、噪聲大等缺點是不可避免的。

2 新方案的提出

近幾年來,越來越多的科研機構致力于開發新型的鎖相倍頻系統,無論在數字還是模擬領域,都有了嶄新的突破。在模擬方面,Fordahl開發了一種如圖2所示的新倍頻模擬方法。該方法在高頻和低頻段工作良好,同時有效地改善了在鎖相環設計中所帶來的缺陷。在數字方面,一種全新構架的無類比全數字鎖相倍頻電路已經由某科研機構研制開發成功,并已經投入使用,其結構如圖3所示。該設計完全基于FPGA/CPLD設計開發而成,鎖相時間短(只需要一個系統時鐘" title="系統時鐘">系統時鐘周期tpd的延時),同時具有無類比電路、無抖動、無內部振蕩器、功耗低等優點。

本文結合上述兩種方法,根據FPGA流水線的操作思想,設計了一種全新的相位鎖定倍頻系統。在具備上述兩個倍頻電路優點的同時,增強了倍頻的精度,擴大了倍頻范圍,在系統資源允許的范圍內,合理地利用芯片面積與速度的關系,以較少的邏輯單元,設計出高速倍頻系統。

3 原理及算法

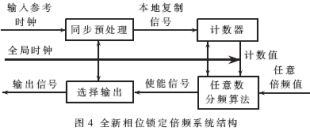

這種全新相位鎖定倍頻系統由四大模塊組成:同步預處理模塊、計數器模塊、算法模塊、選擇輸出模塊。其結構如圖4所示。

3.1 原理

首先,對輸入參考時鐘(CLK_IN)進行同步處理,對輸入信號進行復制,使得輸入信號與全局時鐘(SYSCLK)達到同步(即使復制后的信號與輸入參考時鐘存在誤差,

誤差也小于一個SYSCLK周期),然后以SYSCLK為基準對CLK_IN進行計數。如果信號CLK_IN抖動很小或者周期恒定,則以n(n>1)個周期為單位進行計數;如果抖動很大(一般與外部環境及物理因素有關),則以一個周期為單位進行計數,并將計數值作為輸入傳送給算法模塊。算法模塊經過一系列算法流程后,得到一個使能信號(/EN)。最后利用建立時間(Tsu)和保持時間(Th)的特性,以使能信號/EN低有效對SYSCLK選擇輸出,得到所需要的倍頻信號。

從PLL倍頻的原理出發,輸入參考時鐘倍頻后的頻率不可能大于系統時鐘頻率,因此對輸入時鐘的倍頻問題歸根結底就是對系統時鐘的分頻" title="分頻">分頻問題。系統時鐘分頻后,一方面作為信號輸出,一方面作為反饋信號。頻率除以N(倍值)后,得到本地估算信號,經過DPLL環路,使之與參考時鐘同相,這樣就得到了與輸入參考時鐘的同相N倍頻輸出信號。從這里可以看出,基于DPLL的倍頻電路是系統相位鎖定與時鐘倍頻同時進行的。因此倍頻過程中,必然受到DPLL自身因素的制約。而本文設計的倍頻系統,系統同步過程和倍頻過程是兩個獨立的過程,相互之間不存在依附關系,因此可以將兩個過程分別做優化處理。

(1)鎖相問題。可以把它轉化為“同步”問題來考慮。同步過程中最重要的概念就是“參照系”,對于鎖相環而言,本地估算信號是以輸入參考時鐘為參照進行運算得來的;而若以系統時鐘作為參照,本地復制信號必然與系統時鐘同步,且與輸入參考時鐘同相。這樣做的優點是相位鎖定快,提高了芯片系統速度(頻率)。

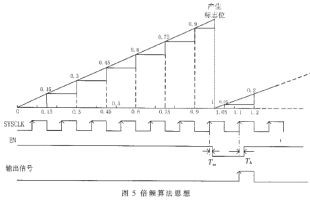

(2)倍頻問題。既然本地復制時鐘是與系統時鐘同步的,而一切與系統時鐘同步的信號必然與復制信號同步,那么對本地復制信號的倍頻問題,就可以簡化為對系統時鐘的分頻問題。例如,假設輸入參考信號的頻率為64kHz,系統時鐘的頻率為64MHz,現要求設計一個電路,其輸出信號與輸入參考信號同相,且頻率為9.6MHz時鐘。通過運算可得到輸出信號是輸入參考信號的1 500倍,是系統時鐘頻率的20/3分頻。因此只要設計出20/3分頻電路,就可得到輸出信號是輸入參考時鐘1 500倍的倍頻信號。其算法思想如圖5所示。

3.2 算法

以SYSCLK作為累加器" title="累加器">累加器的系統時鐘,累加器的位寬根據分頻的精度而確定,累加操作在系統時鐘的上升沿有效,累加器的初始值為0。因為是20/3分頻,所以累加器在時鐘的上升沿時增加0.15,同時判斷0.15和1的大小,由于0.15<1,所以/EN=1。在時鐘的第二個上升沿到來時,在累加0.15等于0.3后,同時判斷0.3和1的大小,由于0.3<1,所以/EN=1。依此類推,在時鐘的第七個上升沿到來時累加器的值應該是1.05,由于1.05>1,所以/EN=0。再將1.05減去1的差0.05作為累加器的初始值進行下次運算,依次進行下去就可以得到/EN信號。

在FPGA的設計中,一般經常用到的是時鐘的上升沿,根據FPGA的建立時間Tsu和保持時間Th,雖然在建立時間不能采到SYSCLK的上升沿,但在保持時間卻可以采到第八個上升沿。這樣就可以得到頻率為9.6MHz的輸出信號。

4 性能分析

4.1 相位鎖定時間

因為本設計以系統時鐘為參照,所以本地復制信號與輸入參考信號的相位誤差最大為一個SYSCLK周期,本設計使用的是Altera公司的Cyclone系列EP1C3T144-8芯片,系統時鐘頻率最高能達到105.65MHz,因此最大誤差為9.465ns。如果再經過優化,可以達到在7ns以內。

4.2 倍頻范圍及其精度

本設計采用任意數分頻算法,倍頻后輸出信號的頻率范圍可以從0Hz到系統時鐘的最高頻率。因此,對于精度,可以做到小數點后任意值,但是刻意地追求精度,是以浪費芯片面積為前提的,所示選擇精度值還要根據芯片的邏輯單元多少來決定。

5 仿真結果

仿真的部分波形圖如圖6所示,放大效果圖如圖7所示。

本文提出的全新鎖相倍頻系統方案已經在項目中得到應用,并在實踐中得到檢驗,性能完全達到預期要求,效果良好。

參考文獻

1 EDA先鋒工作室, 吳繼華,王 誠.Altera FPGA/CPLD 設計(高級篇).北京:人民郵電出版社,2005

2 徐 躍,王 奇,何秋陽. 一種可編程的全數字鎖相環路的實現.電子技術應用,2004;30(11)

3 龐 浩,王贊基. 一種基于FPGA實現的全數字鎖相環.電子技術應用,2005;31(5)