引言

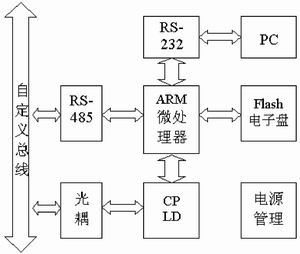

由于交通需求的不斷增加,有越來越多的環形感應線圈檢測器用于交通檢測。這些埋設在道路表面下的線圈可以檢測到車輛通過時的電磁變化進而精確地算出交通流量。交通流量是交通統計和交通規劃的基本數據,通過這些檢測結果可以用來計算占用率(表征交通密度),在使用雙線圈模式時還可以提供速度、車輛行駛方向、車型分類等數據,這些數據對于交通管理和統計是極為重要的。通常高速公路車輛檢測系統由多通道環形檢測單元LD4和控制單元CCU組成,本文采用PHILIPS公司最新推出的ARM7內核微處理器LPC2114設計實現了車輛檢測系統控制單元部分,并且和5個LD4環形檢測器一起構成10通道高速公路車輛檢測系統,其原理框圖如圖1所示。

圖1 車輛檢測系統原理框圖

圖2 控制板系統原理框圖

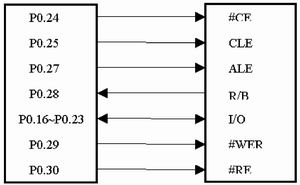

圖3 LPC2114和電子硬盤連線示意圖圖

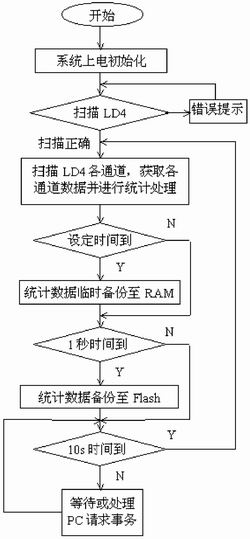

圖4 主程序流程圖

總體方案設計

本文設計的控制板系統原理框圖如圖2所示,以LPC2114為核心控制單元,該芯片是一種支持實時仿真和跟蹤的16/32位基于ARM7TDMI-S 內核的CPU。內部集成了4路10 位A/D轉換器,兩個32位定時器、一個實時時鐘和看門狗,多個串行接口,包括兩個工業標準的UART、高速和兩個SPI總線接口,外部多達46個與TTL電平兼容的通用I/O口,非常適用于作為主控單元。CPLD EPM7128作為微處理器的擴展輸入/輸出,通過光電耦合和LD4標準定義總線相連,該標準定義的總線基于RS-485總線通信協議。LD4和控制板通過標準總線進行數據交換,控制板每隔10秒掃描并發送一次請求數據的命令,相應LD4通道返回請求數據或者無效信息,ARM處理器對獲得的各通道數據進行相應的統計運算處理。每隔用戶設定的間隔時間就將統計數據存儲于靜態RAM,供中心站定時獲取,同時,以分鐘為單位將統計的數據備份至Flash電子硬盤中。中心站可以通過請求備份數據命令獲取相應時間段的數據,并存入數據庫。中心站和控制板采用RS-232串口方式通信,利用調制解調器實現遠程數據傳輸。為了解決大容量存儲問題,系統使用了三星公司提供的K9F2808來作為電子硬盤,16MB的容量能夠存儲11天備份數據,并且該電子硬盤能夠靈活升級。

; LPC2114與電子硬盤的接口實現

為了防止傳輸及中心站故障等問題而導致數據丟失,系統要求對一段時間內的數據進行備份,因此在系統設計的過程中需要考慮大容量存儲問題。

設定本系統每分鐘需要備份一次統計數據,根據環形檢測器LD4的數據格式,一次數據量為1026B,若采用靜態RAM作為存儲單元,需要多片大容量RAM級聯使用,價格昂貴,且存儲容量擴展困難。若使用動態RAM作為存儲單元,缺點在于控制困難,需要動態RAM控制器輔助操作。Flash作為存儲器使用簡單,容量大,盡管使用壽命有限,考慮到系統每1分鐘存儲1026B,就16MB容量而言,11天左右寫滿一次,那么一個月擦寫約3次,以此計算,一年擦寫約36次,而Flash壽命一般為擦寫10萬余次,所以本系統完全可以采用Flash作為電子硬盤用在車輛檢測系統中。另外,Flash還具有掉電非易失特性,更適合應用于本系統。

為了便于存儲容量的升級擴展,本系統選用K9F2808作為存儲器。K9F2808為48腳表面封裝器件,芯片內部有(16M+512K)×8 bit的存儲空間,可組成32768行,528列,其中后備的16列的列地址編碼為513~527,可進行528字節為一頁的讀、寫和32頁為一塊的擦除操作。此外,K9F2808的特點還在于其命令、地址和數據信息均通過8條I/O總線傳輸,接口標準統一,易于存儲容量升級。

圖3為LPC2114和Flash電子硬盤之間的連線示意圖,由于LPC2114沒有外部總線,所以對Flash操作只能采用I/O操作方式。K9F2808各種操作具有共同特點,即在I/O端口首先發送操作命令字到命令寄存器,其后的連續3個周期發送需要操作單元的地址,順序為:A0~A7,A9~A16,A17~A23,其中A8由命令字確定。

下面以頁編程操作為例,給出K9F2808的ARM驅動程序(基于ADS1.2開發環境),而頁讀以及塊擦除等方法與頁編程類似,只是讀是由#RE信號來鎖存數據,而擦除時只須送兩個周期的地址。

row_add為頁號,需要左移9位得到行地址。erase_flash( )——擦除Flash函數

write_command( )——寫命令函數

write_address( )——寫地址函數

write_data( )——寫數據函數

read_data( )——讀數據函數

void flash_store(uint32 row_add, uint8 *buffer )

{ uint16 i;

uint32 statue,address;

//變量定義

IO0DIR |= 0x00ff0000;

//設定IO方向

if((row_add== 0)|| ((row_add%32)==0))

{address = row_add<<9;

address &= 0x00fffe00;

erase_flash(address);}

//擦除Flash

write_command(0x80);

//寫命令80H

address = row_add<<9;

address &= 0x00fffe00;

write_address(address);

//寫地址

statue = IO0PIN;

//獲取狀態

while((statue&fr_b)==0)

{statue = IO0PIN;}

//忙,等待

for(i=0;i<528;i++)

//寫528字節

{write_data(*(buffer+i));}

//寫入數據

write_command(0x10);

//寫命令10H

statue = IO0PIN;

//獲取狀態

while((statue&fr_b)==0)

{statue = IO0PIN;}

//忙,等待

write_command(0x70);

//寫命令70H

statue = read_data(); &nbs

p;

//獲取狀態

if(statue&0x01)

{IO0SET |= errorled;}

//操作失敗

}

LPC2114串口通信實現

控制系統通過LPC2114的兩個UART實現和LD4以及中心站的數據交換,兩個UART具備觸發點可調的16B收發FIFO。其中,UART1比UART0增加了調制解調器接口。UART的基本操作方法和傳統51內核單片機相似。

首先,設置I/O連接到UART;然后設置串口波特率(如U0DLM、U0DLL);接著設置串口工作模式(如U0LCR、U0FCR);這時就可以通過寄存器U0THR和U0RBR發送/接收數據了,發送/接收模塊的狀態信息可以通過U0LSR寄存器讀取。

系統通過RS-485總線和LD4板卡通信,采用MAX3485作為RS-485總線控制器和LPC2114的UART1通信。MAX3485是3.3V供電的半雙工收發芯片,將差分RS-485總線信號轉換成ARM核能夠接受的串口信號。為了實現和PC機通信,系統采用3.3V工作電壓的MAX3232作為RS-232電平轉換芯片。

LPC2114設計注意事項

LPC2114在開發的過程中有一些需要特殊注意的問題,總結如下:

(1) 當用戶程序寫入Flash后不能運行時,首先,需要考慮中斷向量表是否正確,中斷向量表累加和必須為0。其次,需要考慮向量表的定位,向量表是否已經定位在0x00000000地址。然后,需要考慮MEMMAP寄存器的設置是否正確,否則中斷無法執行。此外,還需要考慮ISP硬件條件是否滿足,LPC2114的P0.14腳在#RESET為低時,該引腳線上的低電平將強制芯片進入ISP狀態,硬件設計時必須在該引腳加10KW上拉電阻,否則,該引腳不穩定,對設備啟動將會有影響。

(2) LPC2114共有46個GPIO,這些I/O可以任意配置,但是個別引腳開漏輸出(P0.2、P0.3),需加上拉電阻。另外,Flash存儲器K9F2808狀態輸出引腳R/#B開漏輸出,需加10KW的上拉電阻。

(3) LPC2114芯片加密后,只能通過ISP對芯片全局擦除后才能恢復JTAG調試以及下載等功能。當#RESET為低時,P1.26的低電平使P1.26~P1.31復位后作為調試端口,注意在P1.26引腳和地之間需接一個弱偏置電阻。

系統軟件設計思想及注意事項

車輛檢測系統ARM軟件采用分層設計思想,整個軟件由驅動程序和應用軟件兩部分構成。驅動程序部分封裝了Flash操作、RS-485操作、實時時鐘(RTC)操作、RS-232操作和I/O等操作。應用軟件分成基本函數庫和主程序。其中,主程序流程如圖4所示。

在32位ARM核應用系統中,為了進行系統初始化,往往采用一個匯編文件作為啟動代碼,來實現堆棧、中斷、系統變量、I/O初始化以及地址重映射等操作。開發平臺ADS的策略是不提供完整的啟動代碼,不足部分需要開發人員自己編寫。

系統設計的啟動代碼包含中斷向量表、堆棧初始化以及相應的中斷服務程序與C語言的接口。對LPC2114而言,為了使向量表中所有數據32位累加和為0 ,向量表中設置保留向量值,將中斷向量表中的32個字節數累加,其中,保留向量值不用累加,然后取累加值的補碼,這個補碼的低32位就是保留向量的值。該保留向量值將被BOOT裝載程序用作有效的用戶程序關

鍵字。當向量表中所有數據累加和為0時,且ISP外部硬件條件不滿足時,BOOT裝載程序將執行用戶程序。

結語

本文基于PHILIPS公司最新的ARM7內核微處理器LPC2114實現了高速公路車輛檢測系統的控制單元部分的設計。LPC2114使用簡單、開發容易、具有較高的性價比,非常適用于嵌入式系統中。目前本系統已經推向市場,并取得了較好經濟效益。

參考文獻

1周立功等. ARM微控制器基礎與實踐.北京航空航天大學出版社. 2003. 11

2馬忠梅等. ARM嵌入式處理器結構與應用基礎.北京航空航天大學出版社.2002