在工業控制" title="工業控制">工業控制領域,數字I/O以其簡單、靈活的特性,得到了廣泛的應用。以往對于數字I/O的應用和數量增加的方法通常用GAL和專用I/O芯片采用譯碼擴展等方式來實現,這種方式盡管能夠滿足一定程度上的要求,但對于更大數量的I/O應用,比如幾十甚至上百路的數字I/O,就勉為其難了。為了滿足這種要求,并且進一步提高數字I/O的使用效率,專門針對多路數字I/O進行了基于STD總線" title="STD總線">STD總線的設計,應用Xilinx公司的CPLD" title="CPLD">CPLD進行編程開發,實現了64位數字輸入DIN 0~DIN 31和64位數字輸出DOUT O~DOUT 31,同時每一路I/O可以獨立編程,既可以作為輸入又可以作為輸出。

1 STD總線

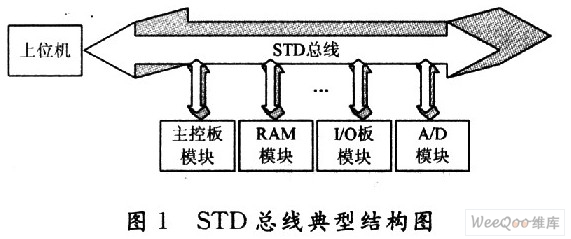

目前,STD標準總線已成為工業控制領域內最流行的標準總線之一,主要用于8位微處理機和單片機工業控制系統。STD總線的典型結構如圖1所示。

在工業控制系統的實際應用中,上位機、主控模塊等往往需要通過STD總線,根據STD總線的協議、特性訪問其他的單片機系統。例如,在某測量設備中,上位機、主控模塊可以通過總線上的I/O模塊、A/D模塊接口,采集傳感器的量值,通過STD總線訪問RAM模塊,以及通過STD總線進行主控模塊與總線上其他控制器之間,主控模塊與上位機之間的通信與數據交換等,構成了一個微型的工業控制網絡。本文的多路數字I/O就是STD總線中的一個模塊。

2 多路數字I/O的硬件設計

2.1 電路組成

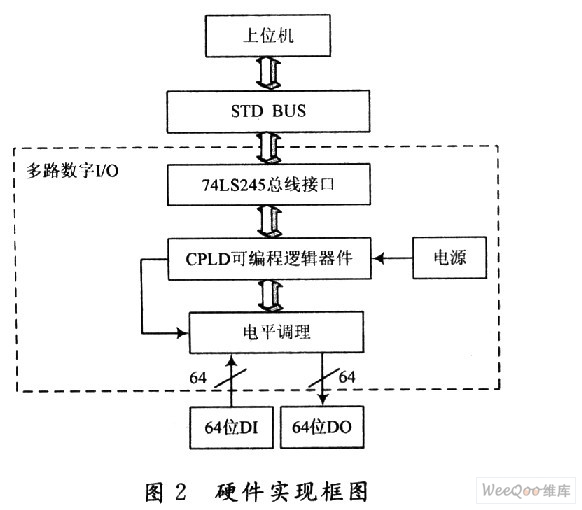

主要由可編程邏輯電路、電平調理電路、總線接口電路以及電源電路等組成。可編程邏輯硬件采用Xilinx公司的CPLD器件XC95288,應用。Xilinx公司的Project Navigator(ISE)集成開發環境進行編程開發;電平調理電路采用74LS245,具有輸入輸出電平轉換的功能,還可以通過接繼電器或者光電隔離器與外設接口;總線接口電路采用74LS245,對74LS245的DIR(方向)進行讀寫編程,實現了與STD總線的數據通信,電源電路為CPLD以及電平轉換電路等提供必需的電源系統。

硬件實現框圖如圖2所示,虛線框內為多路數字I/O的硬件電路部分。

2.2 性能特點

數量多 CPLD芯片XC95288具有208個管腳,其中用戶I/O管腳數量達到168個,除了地址總線、數據總線以及片選信號等所占用40個I/O之外,其余的128個I/0完全可以作為通用I/0編程使用;

面積小 如此眾多數量的I/O,完全由一片CPLD來實現,簡化了電路設計程序,減少了PCB的設計面積,又提高了數字I/O的穩定性;

靈活性高 由于每一個I/O都可獨立編程,因此在使用過程中變得非常靈活,可以根據現場需求隨時改變其輸入、輸出,在工業控制應用領域為產品的增強與升級提供了極大的靈活性。

此外,該設計還具有傳輸速度高(由CPLD的傳輸特性決定)及電平兼容性好等特點,可滿足用戶在測試、控制及設計應用中的多種需求。

3 多路數字I/O的程序設計

該系統使用業界領先的FPGA設計環境XilinxISE,其將先進的技術與靈活性、易使用性的圖形界面結合在一起,可以在最短的時間,獲得最佳的硬件設計。XC95288 CPLD是低功耗3.3 V器件,288個宏單元,6 400個可用邏輯門,168個用戶I/O,再加上靈活、高度優化的VHDL硬件描述語言,實現了128位數字I/O的程序化設計。

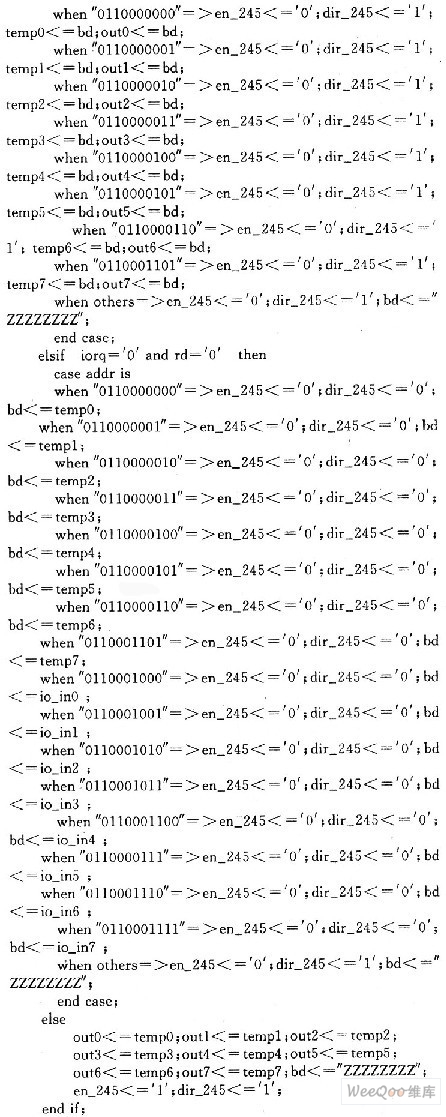

3.1 部分程序代碼

部分程序代碼如下:

其中:addr是10位地址總線;bd是8位數據總線;en_245和dir_245分別是STD總線接口芯片74LS245的片選使能與方向信號;tempx是片內寄存器;io_inx和outx分別是8位輸入、8位輸出I/O口。

3.2 性能描述

多路數字I/O口的選擇由10位地址決定,不同的地址操作不同的。I/O端口,在I/O非動態情況下,數據總線處于高阻狀態,避免了總線沖突,同時也提高了I/O端口的穩定性,減少了高速數據傳輸條件下引起不必要的錯誤,根據現場對I/O輸入、輸出的需要,可以修改程序,靈活改變端口的功能,另外,對于輸出端口,加入了數據寫出后讀回的功能,使得上位機能夠隨時驗證寫出數據的正確性,對于外設信號,通過信號調理板實現電平匹配,進一步增加了本設計的功能可靠性。

4 結語

以CPLD器件為核心,選用Xilinx公司的ISE作為硬件開發平臺,并采用VHDL編程語言,充分應用了可編程邏輯器件的特點,發揮了VHDL硬件描述語言的編程優點。減少了芯片數量,既做到了系統小型化又降低了成本。程序已通過綜合實驗,應用了STD總線的通訊特點,與總線上的其他板卡、設備通訊也極為方便,既解決了工業通信網絡的一般問題,又達到了工業通用I/O的較高要求。總之,該多路數字I/O設計容量高、功耗低、速度快,不僅具有通用性、實用性,而且具有靈活性和移植性,便于調試,為高速I/O開發設計提供了一種很好的嘗試,相信在很多行業都會有廣闊的應用前景。