1 引言

CPLD ( Complex Programmable Logic Device ) 是新型的可編程邏輯器件,與傳統ASIC相比,具有設計開發周期短、設計制造成本低、開發工具先進等優點,特別適合于產品的樣品開發和小批量生產。傳統的數字電壓表多以單片機為控制核心,芯片集成度不高,系統連線復雜,難以小型化,尤其在產品需求發生變化時,不得不重新布版、調試,增加了投資風險和成本。而采用CPLD進行產品開發,可以靈活地進行模塊配置,大大縮短了開發周期,也有利于數字電壓表向小型化、集成化的方向發展。

2系統原理及組成

系統組成原理框圖如圖1所示。系統的控制核心是一片CPLD芯片,它由三個功能模塊構成: A/D轉換時序控制模塊、碼制變換模塊以及顯示控制/驅動模塊。三個模塊的功能分別為發出控制信號啟動A/D轉換及讀取采樣值、對AD采樣值進行碼制轉換、發出控制信號驅動LED/LCD顯示相應數據。

系統工作原理:測量信號經過信號預處理,變換為0~2.5V范圍內的有效信號后送入A/D轉換電路中,然后A/D轉換時序控制模塊發出控制信號,啟動A/D轉換器進行轉換,A/D采樣得到的數字信號在碼制變換模塊中轉換為相應的顯示代碼,最后經顯示控制/驅動模塊發出控制與驅動信號,推動外部的顯示模塊(LED/LCD)顯示相應的數據。

3CPLD功能模塊設計

智能數字電壓表的控制核心CPLD的三個功能模塊皆用VHDL語言編程實現,下面主要介紹CPLD的三個功能模塊的設計。

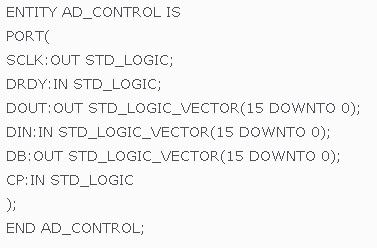

3.1 A/D轉換時序仿真模塊AD_CONTROL

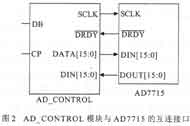

ANALOG DEVICES公司生產的AD7715是一片16位的∑-Δ ADC集成電路。它的主要特性有:3V/5V工作電壓,單/雙極性輸入;可編程改變增益為1,2,32,128倍;在單極性輸入狀態下模擬電壓輸入范圍允許為0~20mV, 0~80mV, 0~1.25V, 0~2.5V不等(有利于提高精度);三線串行接口;支持差分輸入;低功耗(450 mF [email=Max@3V]Max@3V[/email])。在本系統中AD7715的作用是將0~2.5V的輸入模擬信號轉換為16位的高精度的數字信號供CPLD處理。AD_CONTROL模塊用于控制AD7715的啟動、讀、寫等操作。設計的AD_CONTROL模塊如圖2所示,其VHDL語言的ENTITY定義部分如下:

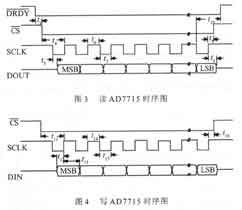

如圖所示,二者的接口信號線直接連接并由AD_CONTROL模塊模擬產生AD7715芯片的各個接口信號,完成ADC的啟動、讀、寫操作。AD7715的工作模式由內部寄存器(Communications Register,Setup Register,Test Register,Data Register)中的控制字決定。內部寄存器的數據寫入和讀出都由CS,DRDY,SCLK信號控制。當 AD7715被訪問時,SCLK腳應出現一次帶上升沿的高電平,其時鐘頻率應為9.2kHz。這是關鍵信號,其他信號均以此信號作為時基。因此,CPLD中的AD_CONTROL模塊的功能之一就是提供SCLK 以及其他信號的嚴格時序。圖3、圖4分別為AD_CONTROL模塊讀、寫AD7715時序圖。

3. 2 碼制變換模塊DATA_CONVERSION

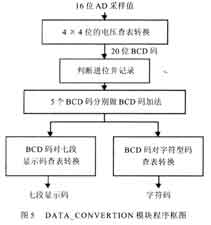

在此碼制變換模塊DATA_CONVERSION中主要實現的功能是將AD采樣送來的16位的二進制數轉換為可被LED/LCD識別的七段LED顯示碼或字符型LCD碼。在本系統中此模塊包含了這兩種轉換功能以適應顯示端不同的配置。為了達到這一目的,首先要將16位二進制碼變換為BCD碼,然后再分別進行轉換,得到七段顯示碼及字符型碼。在此模塊中各個BLOCK部分的碼制變換的VHDL程序可通過WHEN-ELSE語句進行查表來實現。轉換的過程如圖5所示。

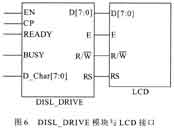

3.3 顯示控制及驅動模塊DISL_DRIVE

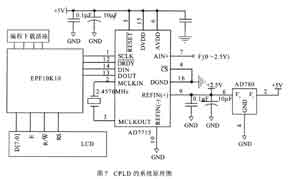

電壓值的顯示可由LED或LCD實現。在本系統中對于電壓值的顯示分為mV和V兩檔,所以需要在后面加上單位來明確,且本系統為低功耗系統,若用LED則功耗相對過大,所以選用了一塊8×2字符型液晶顯示模塊MDSL81809-03,實現了低功耗,而且可帶單位雙排顯示,字體美觀大方。 DISL_DRIVE示,整個電路十分簡潔。系統工作過程首先由 CPLD對AD7715及LCD進行初始化,然后當有輸入信號V i(0~2.5V)到AIN+端后,由CPLD通過接口向AD7715的寄存器中寫入控制字,使其對輸入的模擬信號進行轉換,變為16位的數字信號送到DOUT端,由CPLD經過碼制變換等處理后,再通過與LCD的接口驅動并發送數據,將電壓值及單模塊與LCD的接口如圖6所示。圖中LCD的RS端需輸入方波驅動,這可由CPLD編程提供。當AD7715采樣完成后,由DATA_CONVERSION模塊將采樣數字信號轉換為LCD可識別的字符型數據后,送至DISL_DRIVE模塊,再由其驅動LCD,將字符型數據送到LCD的D0~D7端,實現顯示。

4系統設計和邏輯仿真

CPLD的三個功能模塊用VHDL語言描述,進行綜合仿真后連接起來的系統電路原理圖如圖7所位顯示在LCD上。

本系統采用的CPLD芯片為ALTERA公司的EPF10K10LC84-4芯片,邏輯門數為10000門,用MAX+PLUSⅡ10.0軟件工具開發。設計輸入完成后,進行整體的編譯和邏輯仿真,然后進行轉換、延時仿真生成配置文件,最后下載至CPLD器件,完成結構功能配置,實現其硬件功能。

5 總結

本系統是用CPLD實現的智能數字電壓表。隨著EDA技術的廣泛應用,CPLD已成為現代數字系統設計的主要手段,CPLD目前正朝著更高速、更高集成度、更強功能和更靈活的方向發展。