Blackfin處理器功耗由內部功耗、外部功耗和實時鐘功耗組成。內部功耗由內部動態電流和靜態電流引起。外部功耗取決于處理器內外設的使用情況,在不同的應用場合,片內外設的使用有所不同,外部功耗也會不同。實時鐘功耗一般處于特定范圍之內,工作溫度為25~85℃時,實時鐘功耗范圍為0.067~0.1825mW。Blackfin系列處理器提供了動態電源管理功能,靈活的對時鐘頻率、工作模式及內核電壓進

行調整,以Blackfin533為例闡述Blackfin系列處理器低功耗設計的具體方法。

1 時鐘頻率控制

現代DSP芯片中大量使用CMOS FET(Complementary Metal-oxide Semiconductor FET互補金屬氧化物場效應管)開關,穩定時或者處于完全打開狀態(很低的負載),或者處于完全關閉狀態,但是在兩種狀態轉換過程中會產生漏電流,所以開關頻率很高時,FET充放電會引起很大的電源功耗。因此,通過降低系統時鐘頻率可以有效降低系統功耗。

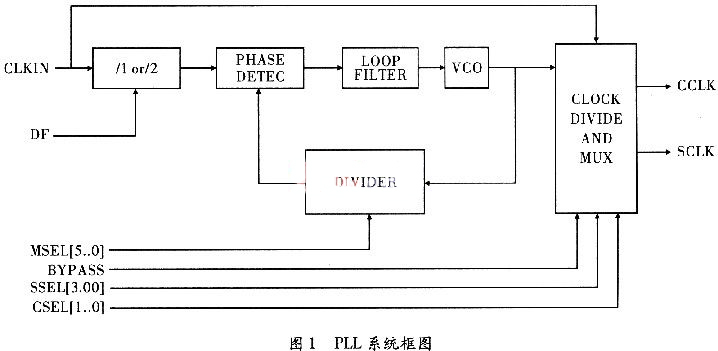

Blackfin533通過外部時鐘輸入引腳CLKIN接收外部時鐘源(10~40 MHz)的時鐘輸入,再通過鎖相環(PLL),電路模塊產生內核時鐘(CCLK)和系統時鐘(SCLK),通過設置PLL相關寄存器實現對CCLK和SCLK的頻率控制。PLL系統如圖l所示。

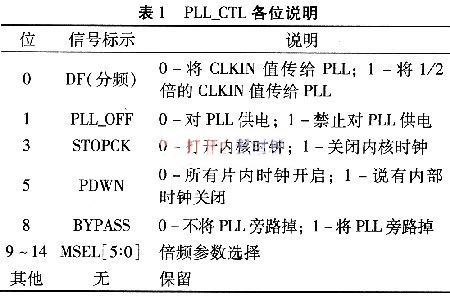

CCLK和SCLK均由VCO(Voltage-ControlledOscillator-壓控振蕩器)輸出的時鐘分頻后得到。VCO輸出時鐘頻率由PLL控制寄存器(PLL_CTL)設置,CCLK和SCLK對VCO的分頻因子由PLL分頻寄存器(PLL_DIV)設置。PLL_CTL各位說明如表1所示。

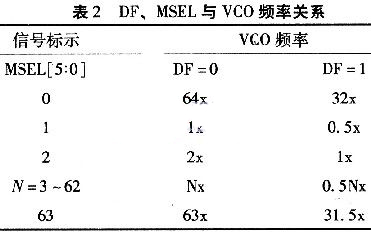

對于不同的DF和MSEL值,VCO輸出相應的時鐘頻率,對應關系如表2所示。

需要注意的是VCO最小輸出時鐘頻率為50 MHz,最大輸出頻率為內核時鐘CCLK頻率的最大值。對BlackfinBF533,CCLK最大值為600 MHz,而BF532/531的CCLK最大值為400 MHz。所以VCO輸出頻率不應超出范圍50MHz~CCLK。

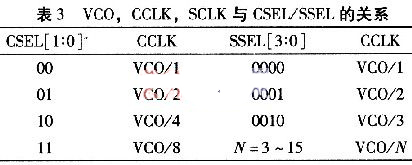

通過設置PLL分頻寄存器PLL_DIV中的CSEL(PLL_DIV的4~5位)確定CCLK,設置SSEL(PLL_DIV的0~3位)確定SCLK,具體對應關系如表3所示。

由于SCLK頻率不能高于CCLK的頻率,所以在對SSEL參數設置時,需要確定當前CCLK的頻率。

假設外部時鐘輸入CLKIN=27 MHz,將CCLK設置為594 MHz(27×22),SCLK設置為118.8 MHz(594/5),程序代碼如下

2 工作模式轉換

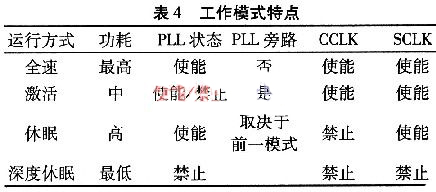

Blackfin533具有4種工作模式:全速、激活、睡眠、深度睡眠,功耗大小關系為:全速>激活>睡眠>深度睡眠。不同模式下處理器的內核電壓及時鐘設置不同,如表4所示。所以靈活調整系統的工作模式可以有效的降低系統的功耗。

在轉換工作模式時,應該明確處理器當前的工作模式,而系統的工作模式由PLL控制寄存器(PLL_CTL)中的PLL_OFF,BYPASS,STOPCK和PDWN狀態位共同確定。圖2說明了各種工作模式轉換之間的聯系以及轉換條件。

通過設置PLL_CTL寄存器實現工作模式的轉換,新的設置不會立即生效,需要先執行下面的一個程序段

從當前工作模式轉換至另一個工作模式的具體過程簡述如下

(1)設置喚醒請求,目的:將處理器喚醒,使PLL_CTL中新的設置生效以便進入新的工作模式。

(2)按模式轉換條件,設置PLL_CTL。

(3)禁止一切中斷,將處理器置入空閑狀態,等待喚醒請求。

(4)喚醒后恢復中斷,PLL_CTL中設置的新值開始生效,處理器進入新的工作模式,繼續執行其他指令。

默認狀態下,所有的中斷都能產生1個喚醒請求,即當1個中斷產生時,處理器內核就會收到1個喚醒請求,如果此時處于空閑狀態,則會退出此狀態,處理相應(中斷)程序。通過系統中斷喚醒使能寄存器(SIC_IWR)設置中斷與喚醒請求之間的對應關系,其中24~31位保留,其他位分別對應了不同的中斷源,如定時器中斷、看門狗定時器中斷、DMA中斷等,某一位如果置1,則相應中斷發生時就會產生1個喚醒事件。系統復位后,SIC_IWR中的所有位均為1。

工作模式轉換的關鍵就是對PLL_CTL的設置,這就要求確認系統當前的工作模式,再根據圖2所示的轉換條件設置PLL_CTL寄存器。另外必須設置喚醒請求,因為它有助于確定處理器何時被喚醒,進入預期的工作狀態。

下面是一個從全速模式到激活模式轉換的實例:

對喚醒請求進行設置,本例中利用看門狗定時器中斷來產生這個喚醒請求。

(1)設置定時器的計數值:通過看門狗計數寄存器(WDOG_CNT)設置。

(2)設置相應事件:當定時器計數至O時產生中斷,即看門狗控制寄存器(WDOG_CTL)第3位置1,其余位為0。

(3)利用看門狗中斷產生喚醒請求:SIC_IWR寄存器第24位置1,其他位為0,使能看門狗中斷喚醒請求。

3 片內外設控制

系統設計中不是所有外設都能用到,而系統具體運行過程中,有些外設也不需要一直工作。所以,在適當的時候可以通過禁用不使用的外設來降低系統的功耗。Blackfin535有專門的外設時鐘寄存器(PLL_IOCK),統一控制所有外設的時鐘,禁用某外設只需要將PLL_IOCK中對應位置0即可。Blackfin533/532/531沒有這種統一的時鐘控制寄存器,只能通過每個外設的控制寄存器來使能或禁用外設。

4 內核電壓控制

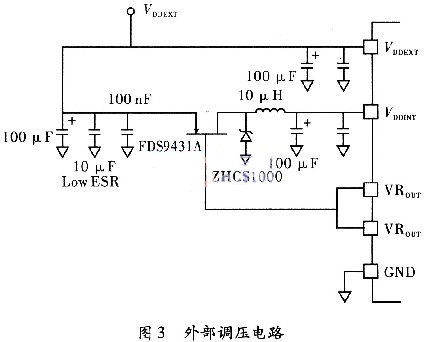

Blackfin系列處理器通過片內的調壓器可以將外部的2.2~3.6 V的供電電壓轉換成0.85~1.2 V,為內核供電。由于功耗與電壓的平方成正比,降低內核電壓可有效降低系統功耗。片內的調壓器需要搭配一定的外部電路才能實現其調壓功能,外部電路圖3所示。

VDDEXT為I/O供電電壓,VDDINT為內核供電電壓,VROUT為外部FET/BJT驅動,用于控制開關頻率。

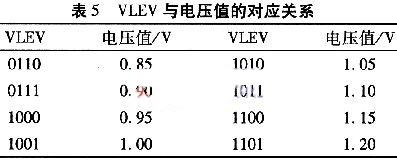

通過調壓器控制寄存器(VR_CTL)的VLEV(4~7位)來設置內核電壓值,VLEV與電壓值的對應關系,如表5所示。

修改VR_CTL的VLEV值可將內核電壓控制在0.8~1.2 V,也可以將內核供電完全關閉,即將VR_CTL中的FREQ(O~1位)設置為00,此時內核時鐘和系統時鐘都會停止工作,而內核電壓為0。修改內核工作電壓的程序段需要放在對PLL_CTL設置程序之后執行。