摘 要: 介紹了10G" title="10G">10G以太網的技術特點、協議層結構及幀格式,并概述了UTOPIA接口。為了實現10G以太網的物理層和數據鏈路層" title="鏈路層">鏈路層之間的連接,采用UTOPIA level4協議并介紹了實現10G以太網UTOPIA接口的設計方案與實現,給出了功能模塊圖。為降低芯片功耗,采用并行設計方案。

關鍵詞: 10G以太網 MAC UTOPIA XGMII 功耗

以太網以其成本低、高可靠性、安裝簡便、維護容易和易擴展等優點成為非常流行的局域網技術。從1973年問世至今,以太網不斷改進,速率等級從10Mbps、100Mbps提高到1000Mbps,應用范圍從局域網擴展到城域網。由于匯聚的1000Mbps需要更高速率的以太網技術" title="以太網技術">以太網技術,于是10G以太網應運而生。10G以太網標準IEEE802.3ae在IEEE802.3的基礎上,添加了廣域網接口,不僅繼承了以太網技術,而且提高了MAC(Media Access Control, 介質訪問控制層)子層速率到10Gbps,使得局域網用戶更有效地使用多媒體以及其它數據應用。這種技術能夠應用到多種類型的網絡,并能利用統一的以太網技術建立范圍更廣闊的網絡[4][9][12]。10G以太網有以下主要特點[13]:

(1)網絡連通性、可靠性和可擴展性高;

(2)只支持全雙工模式,傳送媒體只能是光纖;

(3)不使用載波偵聽多路訪問和沖突檢測協議;

(4)使用64B/66B和8B/10B兩種編碼方式;

(5)具有支持局域網和廣域網的接口,網絡范圍擴展到40km。

1 10G以太網協議層結構

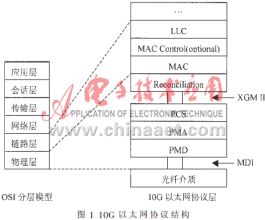

10G以太網基于下面的技術:位于OSI模型中數據鏈路層的MAC層,以及介于MAC層和物理層的XGMII(10G Media Independent Interface,10G介質無關接口)。物理層又包括PCS(Physical Coding Sublayer,物理編碼子層)、PMA(Physical Media Attachment,物理介質附屬子層)、PMD(Physical Media Dependent,物理介質相關子層)。

圖1是10G以太網的協議結構[1~2]。其中LLC(Logical Link Control, 邏輯鏈路控制層)在網絡層和介質訪問控制之間提供連接。MAC層負責對網絡的訪問、MAC尋址、幀類型識別等與幀相關的操作。Reconciliation(適配層)是MAC層和物理層之間的通路。XGMII在MAC層和物理層之間提供了一個標準接口,使得MAC層能適應不同的物理層。PCS(Physical Coding Sublayer,物理編碼子層)主要負責對來自MAC層數據的編碼和解碼。PMA(Physical Media Attachment,物理介質附屬子層)負責把編碼轉換為適應物理層傳輸的比特流,同時完成數據解碼的同步。PMD(Physical Media Dependent,物理介質相關子層)負責信號的傳送包括信號的放大、調制和波的整形。不同的PMD設備支持不同的物理介質。MDI(Media Dependent Interface,介質相關接口)定義了對應于不同的物理介質和PMD設備所采用的連接器類型。10G以太網協議在XGMII接口下增加WIS子層(WAN Interface Sublayer,廣域網接口子層),可以讓10G以太網幀能夠在目前廣域網中廣泛使用的SONET/SDH體系中傳輸。

2 幀格式

10G以太網的MAC幀不必像千兆以太網那樣拆分/封裝幀結構,更適合高速交換。圖2為10G以太網的MAC幀格式[1]。為了在現有的廣域網上傳輸10G以太網幀,MAC層還負責把10Gbps速率匹配成9.058464Gbps速率。

3 UTOPIA接口實現

3.1 UTOPIA接口

UTOPIA(Universal Test & Operations PHY Interface for ATM)接口是ATM論壇定義的一個重要的設備內部接口,是物理層與上層邏輯邊界的具體物理實現。目前有四個等級的UTOPIA規范,本文采用的UTOPIA level4[3]協議,它支持點對點的高速互聯。其數據寬度可以是32比特、16比特或者8比特,基本的接口工作速度可達415MHz。除了數據信號,還有時鐘信號和控制信號" title="控制信號">控制信號。控制信號控制數據或控制字是否在數據總線上傳輸。流控、尋址和其他控制功能均通過數據總線帶內傳輸,減少了接口信號線的數量。由于對稱性,UTOPIA level4協議非常適合鏈路層端對端通信。當數據包在物理層和鏈路層傳輸時,發送方向(Tx)指從鏈路層到物理層,反之為接收方向(Rx)。圖3是UTOPIA接口示意圖,顯然它是物理層和鏈路層之間的數據傳輸通道,并可在芯片內部實現[6]。

3.2 UTOPIA接口實現

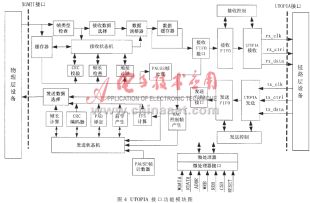

UTOPIA接口的信號采用圖2所示的MAC幀格式,幀長度從64字節到1518字節。圖4是10G以太網的UTOPIA接口功能模塊圖,分為數據接收端口和發送端口[5][7][8][10]。發送端口從鏈路層發送下行數據到物理層,接收端口從物理層發送數據到鏈路層。端口的地址總線寬度為8比特。接收端口有32比特的rx_data信號、rx_ctrl控制信號和rx_clk時鐘信號,發送端口有32比特的tx_data信號、tx_ctrl控制信號和tx_clk時鐘信號。

接收方向的模塊主要完成以太幀的接收,并根據MAC控制幀進行流量控制。來自XGMII接口的數據首先送入“幀類型檢查”模塊,此模塊分辨幀的類型,判斷接收的數據是幀頭還是幀尾,并把要送入FIFO的域值送入“接收數據選擇”模塊。為了在FIFO中實現數據首單元的對齊,采用了“數據調整器”。如果選擇存儲轉發工作模式,調整整齊的數據將進入“數據緩存器”模塊。此模塊緩存收到的數據幀的目的地址、源地址、長度/類型以及標簽控制信息,并直接刪除錯誤幀。如果采用穿通工作模式,數據則直接進入FIFO接口模塊。“接收狀態機”控制且并行執行三個模塊:“CRC校驗”模塊、“幀長檢查”模塊和“地址過濾”模塊。“CRC校驗”模塊判斷是否剝離或者保留CRC;“幀長檢查”模塊計算并比較收到幀的長度是否與長度域的值一致,如果不一致就提供報錯信息;“地址過濾”模塊過濾出單播和組播地址。圖4中未標識出的“接收統計”模塊統計接收方向系統收到的幀個數、正確幀個數、超長幀個數等統計信息。“UTOPIA接收”模塊讀出接收FIFO里的數據并在每個時鐘的上升沿輸出8個字節到UTOPIA接口。“接收控制”模塊控制對發送FIFO的讀寫,防止其溢出和讀空。

在發送方向,來自UTOPIA接口的數據進入“UTOPIA發送”模塊,并寫入“發送FIFO”里。“發送控制”模塊控制對發送FIFO的讀寫,防止其溢出和讀空。“發送狀態機”模塊從發送FIFO里讀出數據,并控制“幀長計算”模塊、“CRC編碼器”模塊、“PAD添加”模塊、“前導產生”模塊與“IFS計算”模塊并行對數據進行操作。“幀長計算”模塊計算來自發送FIFO里的數據的幀長,截斷過長包;“CRC編碼器”模塊對數據進行CRC計算并在幀的CRC域添加CRC值;“PAD添加”模塊填補過短包使之達到以太幀的長度;“前導產生”模塊生成幀的前導域值;“IFS計算”模塊則計算幀間隔。圖4中未標識出的“發送統計”模塊統計在發送方向系統發送幀的個數、發送幀的長度、類型等統計信息。從“發送狀態機”出來的數據以XGMII的數據格式(8個字節的數據和8個比特的控制)發送到XGMII接口。

通過“微處理器”模塊和“微處理器接口”模塊可以對芯片內部的寄存器值進行配置或者讀取寄存器值。

4 降低功耗的考慮

集成電路的功耗估算公式為:P=k f V2,其中P、 f和V 分別為芯片功耗、工作頻率" title="工作頻率">工作頻率和工作電壓。根據此公式可知工作頻率的提高會導致芯片功耗的增加。為了減少芯片功耗,可以從降低芯片工作頻率入手。但是較低的工作頻率會使得芯片面積增大,而芯片面積的增大同樣也會導致芯片功耗的增加。有兩種實現方案:一是采用了并行設計方法降低芯片工作頻率,這樣提高了設計的復雜性并因此增加了芯片門個數從而增大了芯片面積。二是不采用并行設計方法,這樣不增加芯片的門個數,但是芯片面積比較大,從而芯片功耗也比較大。另外,由于芯片面積還受制于其他因素如制造工藝等,而目前國內的制造工藝還實現不了太大的芯片面積。綜合考慮功耗和工作頻率及芯片面積之間的關系,權衡利弊,本文采用方案一來達到它們之間最好的平衡。

本設計采用64位比特并行處理使得內部工作頻率降低為10Gbps的1/64。圖4中所需的FIFO選用FPGA片內集成RAM構成,代替外置FIFO以提高芯片的集成度,減少了芯片間高速通信。

10G以太網是以太網技術發展的一個新臺階,它使得網絡實現低成本、簡單化、可管理、高帶寬和易操作等目標成為可能。本文介紹了10G以太網的技術特點、協議層結構及幀格式,并概述了UTOPIA接口,詳細描述了采用UTOPIA level4實現10G以太網的物理層和數據鏈路層連接的功能模塊圖。為降低芯片功耗,本設計采用并行設計方案。實際結果證明此方案是可行的。目前還可采用SPI-4(System Packet Interface Level 4)協議實現10G以太網的物理層和鏈路層之間的互連,這將是作者的下一步研究工作。

參考文獻

1 IEEE Std. 802.3. 2000 Edition (Incorporating IEEE Std 802.3, 1998 Edition, IEEE Std 802.3ac-1998, IEEE Std 802.3ab-1999, and 802.3ad-2000)

2 IEEE Std. 802.3aeTM -2002(Amendment to IEEE Std. 802.3 (Amendment to IEEE Std. 802.3TM-2002)

3 ATM Forum Technical Committee.UTOPIA Level 4. AF-PHY-0144.001

4 Do-Yeon Kim, Sang-Min Lee, Chang-Ho Choi, Hae-Won Jung, and Yeong-Seon Kim.Trend of 10 Gigabit Ethernet Switch Development in korea. Proceedings of 2003 IEEE Pacific Rim Conference on Communications, Computers and signal Processing, 2003;2(28~30):1032~1035

5 劉雅娟,田素芬,冉茂儒.網絡接入設備的ATM UTOPIA接口設計與實現.微處理機, 2003;3(3):50~53

6 劉 熹,徐子平.UTOPIA接口技術與應用.軍事通信技術,2001;22(1):50~54

7 孟李林,徐 敏.接入網中V5.2接口ASIC芯片設計.半導體技術,2001;26(7):31~34

8 劉紅軍,遲澤英,游明俊.ATM傳輸匯聚子層及其UTOPIA接口的FPGA實現.光通信技術, 2002;15(4):25-27

9 黃 榮,林錦賢.萬兆以太網技術及應用.福州大學學報(自然科學版),2003;31(3):289~292

10 章立生,韓承德.SOC芯片設計方法及標準化. 計算機研究與發展, 2002;39(1):1~8

11 溫小勇,葛元慶.一種低功耗CPU卡的設計. 微電子學, 2002;32(5):369~373

12 Hurwitz, J.,Wu-chun Feng. Initial end-to-end performance evaluation of 10-Gigabit Ethernet.Proceedings of 11th Sym-posium on High Performance Interconnects,2003: 116~121

13 沈曉強,于娟,邵鐘浩.10G以太網—一種新的廣域網傳輸技術.現代電信科技,2003;3(3):28~31