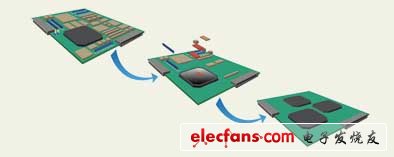

如今,由于可編程器件(如FPGA)容量大、性能高、成本相對(duì)較低的特性,這種平衡又在發(fā)生變化,以前硬件設(shè)計(jì)元素(如處理器及其外圍器件和邏輯塊)也可以轉(zhuǎn)移到軟領(lǐng)域(圖1)。因此,在整個(gè)開(kāi)發(fā)周期內(nèi),靈活性可能更大,更改關(guān)鍵設(shè)計(jì)也更加方便,比如可以更改軟件與硬件實(shí)現(xiàn)之間的功能分區(qū),甚至更改處理器的選擇。

與大量使用分立的現(xiàn)有處理器開(kāi)發(fā)嵌入式系統(tǒng)相比,目前開(kāi)發(fā)基于FPGA的處理器應(yīng)用程序的做法仍很少。盡管FPGA已確實(shí)廣泛應(yīng)用于與嵌入式系統(tǒng)處理器密切相關(guān)的外圍邏輯中,但除了可編程設(shè)計(jì)之外,處理器及其重要外圍器件仍保持著導(dǎo)線連接。

圖1:隨著用戶(hù)買(mǎi)得起的高性能可編程器件的問(wèn)世,設(shè)計(jì)工程師可將相當(dāng)部分的硬件設(shè)計(jì)從硬連線平臺(tái)轉(zhuǎn)移到“軟”環(huán)境中,從而節(jié)省設(shè)計(jì)時(shí)間、簡(jiǎn)化電路板設(shè)計(jì)并降低制造成本。

部分原因來(lái)自于成本。FPGA的體積大、性能高,盡管能提供一個(gè)處理器的應(yīng)用平臺(tái),但與性能相當(dāng)?shù)姆至CU相比,它也更加昂貴。因此,采用FPGA方案所產(chǎn)生的額外費(fèi)用限制了FPGA方案的應(yīng)用范圍。不過(guò)最近,賽靈思Spartan-3系列等器件消除了價(jià)格上的限制,當(dāng)這些器件與合適的基于FPGA的處理器內(nèi)核相結(jié)合時(shí),成本與收益的平衡將被打破。

即使價(jià)格不再是限制FPGA作為主流嵌入式系統(tǒng)平臺(tái)的唯一障礙,但仍存在另一個(gè)更難處理的問(wèn)題,即我們需要改變對(duì)可編程邏輯器件的總體看法。我們不能僅僅把它們看成集成邏輯塊的有效方法,而是需要擴(kuò)大視野范圍,重新評(píng)估在器件(如FPGA)可重新配置的情況下我們對(duì)整個(gè)設(shè)計(jì)過(guò)程的看法。

對(duì)“界面友好”開(kāi)發(fā)模型的需求

如果在更大范圍內(nèi)審度與嵌入式設(shè)計(jì)相關(guān)的FPGA現(xiàn)象,線索也許就在于微處理器本身的歷史。微處理器最初用于計(jì)算器,后來(lái)用于個(gè)人電腦。當(dāng)器件價(jià)格只占一小部分產(chǎn)品成本時(shí),隨著技術(shù)的進(jìn)步,用戶(hù)界面友好的開(kāi)發(fā)模型開(kāi)始得到廣泛應(yīng)用(如高級(jí)編程語(yǔ)言C語(yǔ)言的應(yīng)用)。

由于軟件具有很好的靈活性和強(qiáng)大功能,所以它們可以創(chuàng)建一種新的設(shè)計(jì)模式,該模式可以自由創(chuàng)建和修改大部分系統(tǒng)功能而無(wú)需重新設(shè)計(jì)硬件。采用C語(yǔ)言編寫(xiě)嵌入式應(yīng)用程序,意味著眾多設(shè)計(jì)工程師可以獲得其強(qiáng)大功能和靈活性,這促使基于處理器的嵌入式設(shè)計(jì)成為電子產(chǎn)品的主流設(shè)計(jì)。

FPGA可以大大增加系統(tǒng)中“軟”器件的數(shù)量,從而具有類(lèi)似于引發(fā)設(shè)計(jì)革命的潛力。正如前文所述,大型可編程器件現(xiàn)在的價(jià)格使之足以與離散處理器系統(tǒng)競(jìng)爭(zhēng)。為推動(dòng)設(shè)計(jì)工程師采用FPGA器件作為嵌入式應(yīng)用平臺(tái),需要一種用戶(hù)界面友好的開(kāi)發(fā)方法。該方法既容易被大多數(shù)工程師理解,又能方便地將處理器、外圍硬件和軟件輕松集成在可編程平臺(tái)中。除此之外,一種在板極設(shè)計(jì)過(guò)程中集成FPGA設(shè)計(jì)的方法,可以讓用戶(hù)輕松應(yīng)對(duì)在新的“軟”設(shè)計(jì)模型中發(fā)生的變化。

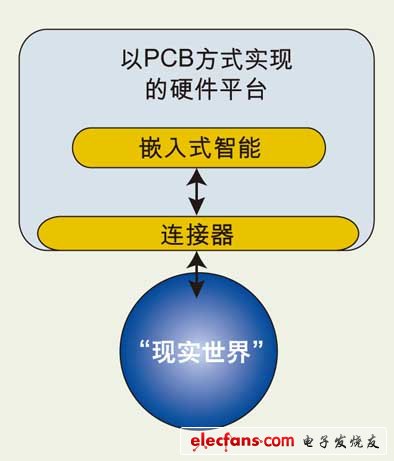

圖2:嵌入式產(chǎn)品智能包括軟件以及包含在FPGA中的軟連接系統(tǒng)器件,PCB僅成為器件智能連接外部世界的一個(gè)平臺(tái)。

但當(dāng)我們把FPGA看作系統(tǒng)平臺(tái)時(shí),在HDL領(lǐng)域獲得必需的系統(tǒng)器件(例如處理器與外圍器件),并在寄存器轉(zhuǎn)換級(jí)實(shí)現(xiàn)它們的過(guò)程十分復(fù)雜。對(duì)那些目前還不是FPGA專(zhuān)家的大多數(shù)工程師來(lái)說(shuō),這是一個(gè)令人生畏的過(guò)程。

但是,工程師在板級(jí)上開(kāi)發(fā)同樣復(fù)雜的設(shè)計(jì)系統(tǒng)不會(huì)遇到這些困難,因?yàn)樵诎寮?jí)上,系統(tǒng)的復(fù)雜性表現(xiàn)在用來(lái)創(chuàng)建設(shè)計(jì)的現(xiàn)有器件上,而工程師只是簡(jiǎn)單地使用這些器件,并不需要了解其內(nèi)在復(fù)雜性。

因此,挖掘FPGA作為主流嵌入式系統(tǒng)平臺(tái)的潛能,關(guān)鍵就在于提供當(dāng)前板級(jí)設(shè)計(jì)與基于FPGA的系統(tǒng)設(shè)計(jì)之間的無(wú)縫轉(zhuǎn)換。未來(lái)的設(shè)計(jì)工具與嵌入式智能

設(shè)計(jì)解決方案供應(yīng)商Altium公司提供的電子產(chǎn)品開(kāi)發(fā)系統(tǒng)Altium Designer,近年來(lái)引領(lǐng)著設(shè)計(jì)工具的發(fā)展趨勢(shì)。Altium Designer為FPGA提供圖形輸入環(huán)境,其中包含高級(jí)FPGA器件庫(kù)。這些器件包括一系列處理器內(nèi)核和外圍器件,它們?yōu)榇罅磕繕?biāo)FPGA器件提供預(yù)綜合。由于器件是現(xiàn)成的,所以創(chuàng)建系統(tǒng)硬件幾乎成了“拖放”操作。

這個(gè)系統(tǒng)包含自行設(shè)計(jì)、免費(fèi)的32位處理器TSK3000,該處理器可被用于大量FPGA器件及其它系列產(chǎn)品中。其它能支持的運(yùn)行平臺(tái)包括賽靈思MicroBlaze內(nèi)核和內(nèi)嵌于Virtex II Pro器件中的硬PowerPC處理器。

Altium Designer廣泛使用免費(fèi)的開(kāi)放式Wishbone處理器互連總線。為便于處理器和外圍器件的互連,它還提供多個(gè)可配置總線連接器件。基于Wishbone的封裝內(nèi)核可用于MicroBlaze和PowerPC等處理器,并且可以重新定位處理器之間的設(shè)計(jì)而無(wú)需重新設(shè)計(jì)該系統(tǒng)。一個(gè)通用的編譯引擎和集成工具鏈在軟件層支持這個(gè)過(guò)程。

這種方案的優(yōu)勢(shì)是嵌入式開(kāi)發(fā)人員可以為他們的應(yīng)用軟件選擇最合適的運(yùn)行平臺(tái)。他們可以采用TSK3000開(kāi)始設(shè)計(jì),如果以后需要更高性能,則可以將設(shè)計(jì)移植到PowerPC,或者移植到MicroBlaze解決方案。

Altium Designer系統(tǒng)最基本的優(yōu)勢(shì)在于,任何硬件開(kāi)發(fā)商都可以利用現(xiàn)有技術(shù),將系統(tǒng)復(fù)雜度由板級(jí)設(shè)計(jì)轉(zhuǎn)移到“軟”的可編程邏輯領(lǐng)域。這使得大量的設(shè)計(jì)工程師可從硬連接系統(tǒng)器件中解脫出來(lái),并能發(fā)揮在快速變化的硬件和軟件環(huán)境中進(jìn)行設(shè)計(jì)所帶來(lái)的優(yōu)勢(shì)。

設(shè)計(jì)流程朝“軟件”方向的轉(zhuǎn)變始于低成本微處理器的供應(yīng)。由于FPGA技術(shù)的進(jìn)步,這種轉(zhuǎn)變正走向一個(gè)新的階段。如今,電子產(chǎn)品的大部分智能主要取決于嵌入式軟件。通過(guò)FPGA,嵌入式智能將跨越可編程平臺(tái)中的軟件和軟連接器件(圖2),這種可能性將刺激FPGA的廣泛使用,并為未來(lái)電子產(chǎn)品的開(kāi)發(fā)奠定基礎(chǔ)。