引言

隨著圖形處理的巨額運算量,CPU變得不堪重負。此時,需要使用特定的硬件設備來為嵌入式CPU承擔圖形處理的任務。

具有三維圖形硬件加速能力的ARM+FPGA架構嵌入式圖形系統就是其中一種解決方案。其中,ARM處理器負責運行嵌入式操作系統、執行上層圖形應用程序,而三維圖形處理所需的大量運算則由FPGA實現的GPU(圖形處理單元)進行。

圖形API簡介

在圖形系統中預先定義了一組圖形API,作為一個抽象層將圖形應用程序和圖形系統的具體實現隔離開來。具體的圖形應用程序都將通過這些圖形API來完成所有與繪制圖形相關的工作。這樣,同樣的應用程序就可以在不同的目標圖形系統上運行。

目前應用較為廣泛的標準圖形API主要有Direct3D和OpenGL。OpenGL定義了與具體硬件實現無關的軟件接口,并且不受制于具體的窗體系統。

本文選用23條OpenGL中最常用的API作為本系統的圖形API。在執行應用程序時,具體的圖形API被轉換成GPU可以處理的渲染列表數據格式,從而將計算任務轉交由GPU完成,實現對三維圖形處理的硬件加速。

系統硬件設計

系統硬件結構

本文設計的嵌入式圖形系統由基于ARM處理器的最小系統、FPGA實現的圖形加速、LCD控制器等功能模塊,以及常用外設接口電路組成,如圖1所示。

圖1 系統硬件結構

基于ARM處理器的最小系統是本系統的核心模塊,主要由嵌入式處理器、系統內存SDRAM和FLASH存儲器組成。SDRAM為處理器運行操作系統和執行應用程序提供內存空間,FLASH用來存放系統引導代碼、操作系統內核和應用程序。

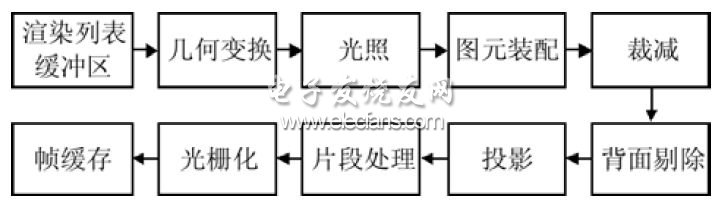

圖形加速模塊是使用FPGA實現的嵌入式GPU,是系統能夠實現硬件加速的關鍵部件。它通過內部圖形處理流水線處理CPU生成的渲染列表,并最終形成像素數據寫入幀緩沖SRAM中供LCD進行顯示。該模塊在三維圖形處理中使用固定功能的圖形處理流水線,如圖2所示。

圖2 圖形處理流水線示意圖

圖形加速模塊在一片SRAM中生成完整幀數據后將其控制權交給LCD控制器,并使用另一片SRAM繼續下一幀數據的計算。在新的一幀數據完成后便再次與LCD控制器交換控制權。LCD控制器通過SRAM仲裁模塊從當前顯示的幀緩存中讀出幀數據,生成符合LCD顯示屏要求的時序,完成三維數據的顯示。

系統中存在兩組LCD總線。一組是ARM處理器提供的LCD總線,用來顯示嵌入式操作系統的圖形用戶界面;另一組是進行三維圖像顯示的LCD控制器的LCD總線。總線切換模塊負責兩類總線的切換,將合適的LCD總線掛接到LCD屏上進行顯示。系統硬件實現

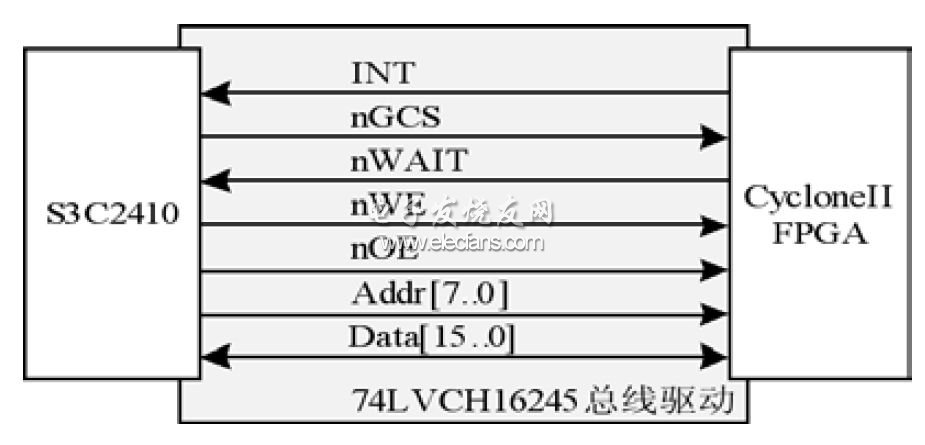

本文選用S3C2410嵌入式處理器和Cyclone II系列FPGA實現圖形加速以及其他功能模塊,輔以LCD屏、串口等外圍電路實現整個圖形系統。

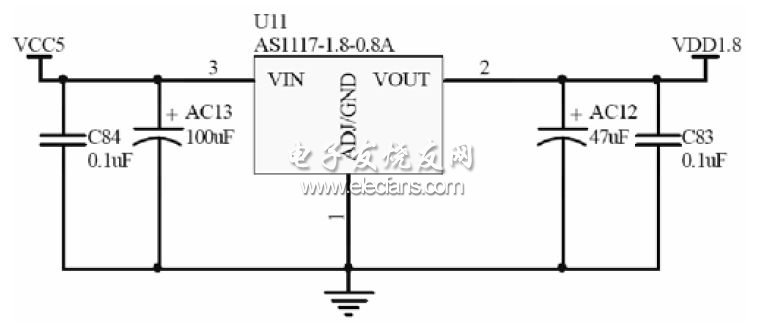

電源設計

本系統需要多個不同電壓值的直流電源供電,包括5V、3.3V、1.8V和1.2V。其中5V電源從外部直流電源直接引入,而其他電壓值則由5V電壓變換得到。

S3C2410的內核電壓為1.8V,外部I/O和存儲器電壓為3.3V。系統選用低壓差穩壓器AS1117實現這兩種電壓的轉換,固定輸出時只需三個引腳,如圖3所示。

圖3 1.8V電源電路

本文使用TPS70345為FPGA提供1.2V內核電壓和3.3V IO電壓。

ARM與FPGA接口電路

生成三維圖形時,嵌入式微處理器上運行的圖形應用程序生成三維圖形的渲染列表,并將渲染列表寫入到FPGA的渲染列表緩沖區中,等待圖形加速模塊的處理。ARM與FPGA接口電路既要保證可以完成渲染列表的寫操作,又要能夠對FPGA中總線接口模塊、圖形加速模塊、LCD控制器等的內部寄存器進行讀寫操作。接口電路如圖4所示。

圖4 ARM與FPGA接口電路

系統軟件設計

系統軟件架構

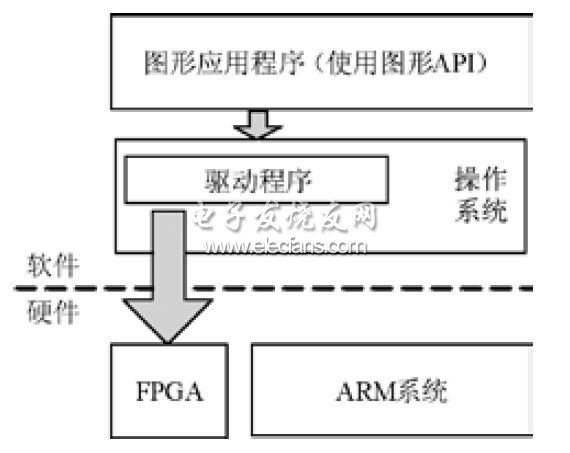

本文使用FPGA實現整個三維圖形處理流水線,由硬件完成三維圖形生成和處理。運行在操作系統上的圖形應用程序通過調用圖形API實現具體應用,而驅動程序將圖形API的調用轉換成渲染列表,從而將具體的三維圖形處理任務交給硬件完成,如圖5所示。

圖5 系統軟件架構

考慮到嵌入式圖形系統除了進行三維圖形處理之外,還應當能夠為用戶提供友好的用戶圖形操作界面,本文采用了Windows CE操作系統。驅動程序設計

設備驅動程序在操作系統和硬件設備之間建立了一個橋梁,讓操作系統能夠識別設備并為應用程序提供設備服務。

本文中FPGA實現的圖形加速模塊作為一個設備掛接在系統中。系統在軟件上只需要將渲染列表寫到該設備的地址空間,因此本文使用了簡單的流式接口驅動,所有的流接口驅動程序都使用相同的一組流接口函數。

渲染列表的傳遞是不需要反饋的,系統將渲染列表寫入設備(GPU)后并不需要從設備中獲取數據,因此流接口函數GPU_Read()并不需要實現具體功能,只在GPU_Write()中將渲染列表寫入到設備中。另外,系統在普通圖形界面和三維顯示兩種顯示模式下使用的是不同的LCD控制器。前者使用S3C2410中集成的LCD控制器,而后者使用的是FPGA模塊中實現的LCD控制器,兩種模式下通過LCD總線切換模塊進行切換。

結語

本文設計了基于ARM和FPGA的嵌入式圖形系統,使用FPGA在硬件上實現三維圖形處理,緩解嵌入式CPU在處理三維圖形時因計算量過大而導致系統效率降低的問題。圖像顯示符合人眼對圖像連續性的要求。