無線網絡流量正日漸以數據為主。目前高速3G的全面鋪開,以及速度更快的4G業務即將上線,無線數據速率隨之水漲船高,因此,能否高效處理流經基站的大量數據已變得至關重要。只要采用合適的硅芯片技術和設計,基站就能夠從容應對4G巨大的網絡流量需求。營運商正轉向異構網絡,同時采用宏蜂窩及小型蜂窩解決方案來提供更出色的用戶體驗。多輸入多輸出(MIMO)天線陣列和高級接收器是新無線標準的關鍵元件,可提高網絡帶寬。將理想的處理元件用于小型蜂窩基站,可幫助開發人員按客戶要求的速度提供所需的數據帶寬。

TMS320TCI6612與TMS320TCI6614均是最新無線基站片上系統(SoC),可實現能夠同時支持3G和4G雙運行模式的業界最高性能小型蜂窩基站解決方案。TCI6612和TCI6614是當前滿足無線網絡營運商對4G小型蜂窩基站以數據為中心性能的理想選擇。多個TMS320C66xDSP核(其中TCI6612為兩個,TCI6614為四個)可提供可編程性能,而新型硬件加速器則可集中精力處理比特速率,幫助基站制造商實現較常規解碼技術高出40%的頻譜效率。此外,每個SoC中的完整ARMRISC內核還可進行控制處理,幫助開發人員為小型蜂窩基站設計低功耗的高性能解決方案。

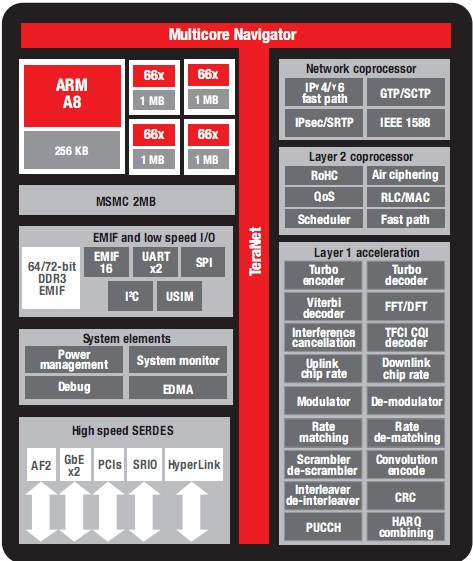

TCI6612與TCI6614SoC建立在德州儀器(TI)可擴展KeyStone多核架構基礎之上,可提供一系列處理元件,其中包括無線電加速器、網絡與安全協處理器、支持定點與浮點功能的數字信號處理器(DSP)核以及ARMRISC處理器等,從而可為實現全面高性能的小型蜂窩基站提供理想的處理元件。基于隊列數據包結構的MulticoreNavigator與TIOpenNavigator編程接口相結合,可幫助設計人員便捷地添加差異化增值特性。此外,TI還在其SoC中集成了數字無線電,不僅可顯著降低成本,而且還可簡化小型蜂窩基站的集成與設計。

TCI6612與TCI6614憑借每個DSP核的定點及浮點處理性能,可幫助基站設計人員充分發揮高速算法原型設計以及快速軟件重新設計的優勢,從而可降低成本、縮短開發時間。由于C66x核具有如此強大的功能,因此只需極少量的內核就可實現比前幾代DSP高出4倍的處理功能。隨著內核數量的減少以及性能的提高,設計人員將享受簡化的編程體驗。

ARMRISC核的集成可顯著降低系統成本。與此同時,ARMCortex-A8核能夠幫助開發人員設計出低功耗高性能解決方案,不僅可在以數據為中心的應用上支持更多用戶,而且還可為基站開發人員帶來前所未有的高電源效率與高集成度。Cortex-A8與整合數據包及安全處理器相結合,無需外部網絡處理器。

主要特性

-

同步雙模式無線基站片上系統(SoC)可為小型蜂窩基站實現無以倫比的高性能;

目前市場最高性能的多核小型蜂窩基站片上系統(SoC),可為同步多標準無線基站實現無可匹敵的高吞吐量以及最低的時延;

位協處理器可提升SoC系統性能并支持高級接收器算法,與常規解碼技術相比,可提高40%的頻譜效率;

TI最新C66xDSP核將定點與浮點性能高度整合在同一芯片上,首次以定點速度支持浮點性能;

支持完整ARM®Cortex-A8處理器的KeyStoneSoC可進行控制層處理;

協處理器的唯一解決方案支持各種標準,包括WCDMA芯片速率,無需FPGA/ASIC;

網絡協處理器與MulticoreNavigator相結合,可為所有無線基站標準實現層2及傳輸加速;

基于TI最新KeyStone架構,不但支持從宏蜂窩到小型蜂窩的擴展與移植,而且還可降低產品開發的成本;

MulticoreNavigator可為多核SoC帶來單核簡易性;

最佳功耗/性能比結合獨特的節電休眠模式,可為基站實現最低功耗;

充分利用高性能40納米工藝技術。

TCI6614方框圖

該TCI6612/14與之前推出的TCI6616和TCI6618無線基站SoC軟件兼容,設計人員可輕松設計出支持所有2G、3G以及4G標準的多模式基站。這種高靈活性不僅可幫助OEM廠商簡化升級到4G的工作,同時還可幫助基站OEM廠商以比同類競爭解決方案更低的成本在更短的時間內開發出更豐富的解決方案。TCI6612與TCI6614引腳兼容,可幫助制造商在單個硬件設計的基礎上,提供多種量身定制的解決方案。

專為小型蜂窩基站精心設計的TCI6612/TCI6614高性能解決方案

TCI6612和TCI6614SoC專為小型蜂窩無線基礎設施基帶應用而精心設計,堪稱小型蜂窩基站的理想解決方案。此外,這兩款SoC還可實現支持GSM、CDMA、WCDMA、TD-SCDMA、WiMAX、FDD-LTE以及TDD-LTE等應用的基帶解決方案。TCI6612和TCI6614代碼向后兼容,不但支持軟件重復使用,還可維護增值設計與IP,從而可簡化從C6000TMDSP的升級。此外,TITCI6612與TCI6614還充分利用KeyStone架構進行擴展,能夠滿足從單區段小型蜂窩到多區段宏蜂窩等所有基站的需要。憑借可驅動各種基站產品的單軟件庫,開發人員將實現最高的研發效率以及最低的產品成本。

TCI6612和TCI6614采用40納米工藝技術,可實現達4.8GHz的原始DSP處理能力以及每秒高達153.6個16位GMAC的性能,因此這兩款器件均是高性能DSP編程難題的低成本解決方案。TCI6612和TCI6614均具有強大的浮點處理能力,可提供每秒高達768億次的浮點運算(GFLOP)性能,是業界功能最強大的浮點和定點SoC。TCI6612和TCI6614在同一內核上整合了定點與浮點兩種處理功能,可實現比獨立定點實施方案快5倍的速度。此外,復雜算法的開發及調試時間可從數月銳減到數天。TCI6612集成2個C66xDSP核,而TCI6614則具有4個C66xDSP核,適用于較大的小型蜂窩基站設計。

TCI6612和TCI6614集成了按2層存儲器系統排列的大型片上存儲器,其可最大限度地減少時延,提升系統性能。兩款器件中每個內核的層1(L1)程序與器件上的數據存儲器容量均為32KB。層2(L2)存儲器可在程序與總容量為4,096KB(每個內核為1,024KB)的數據空間之間共享。它們包含2,048KB的多核共享存儲器(MSM),可用作共享的L2SRAM或共享的L3SRAM。專用多核共享存儲器控制器(MSMC)不但可防止內核間出現存儲器爭用,而且還可在核內與其它IP模塊之間判斷對共享存儲器的訪問。

TCI6612與TCI6614具有高性能外設集,可為開發各種不同覆蓋范圍與容量的高健碩基站提供所需的一切。包括:

-

I²C、SPI以及UART;

可為支持GEN1與GEN2提供2個通道的PCIExpress端口;

12個64位通用定時器(也可配置為16個32位定時器);

具有可編程中斷/事件生成模式的32位通用輸入/輸出(GPIO)端口;

針對硬件加速分派的MulticoreNavigator;

符合RapidIO2.1規范的4通道串行RapidIO®(SRIO),支持每通道達5Gbps的工作速率;

64位DDR3SDRAM接口;

16位外部存儲器接口(EMIF),可連接閃存(NAND和NOR)及異步SRAM;

基于SERDES的第二代天線接口(AIF2),具有6個高速串行鏈路,每個鏈路支持高達6.144Gbps的工作速率,符合OBSAIRP3與CPRI標準。

為實現器件與網絡之間的高效率通信,TCI6612和TCI6614包含了由以下組件構成的網絡協處理器:

-

2個10/100/1000以太網媒體接入控制器(EMAC),可在DSP核處理器與核心網絡之間提供一個高效率接口;

管理數據輸入/輸出(MDIO)模塊(也是EMAC的組成部分),用于不斷輪詢所有32個MDIO地址,以列舉系統中所有的PHY設備;

用于實現L2至L4功能分類的數據包協處理器,處理速率高達1.5Gbps;

安全加速器模塊,能夠通過IPSec、SRTP以及3GPP無線接口安全協議對1Gbps以太網流量進行連線速度處理;

允許多個設備通過SGMII連接的嵌入式以太網交換機,無需板級以太網交換機。

TCI6612和TCI6614高性能嵌入式處理器可執行無線基站應用常見的密集型信號處理功能,可提升整體系統性能,而且頻譜效率也較常規解碼技術高出40%。

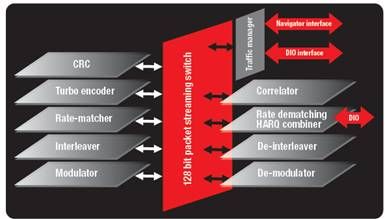

位速率協處理器提升頻譜效率

位速率協處理器(BCP)是一個多標準加速引擎,一旦啟用BCP,便可接管無線信號鏈中所有的位速率處理工作,無需DSP核參與。BCP內含調制器、解調器、交錯器/解交錯器、渦輪及卷積編碼、速率匹配器/速率解匹配器、分組碼解碼相關器以及CRC引擎。BCP不但可為MIMO均衡消除干擾,而且還支持高性能PUCCH格式2解碼。它可接管大約15GHz的CPUMIPS。這些技術與TI新一代DSPC66x內核強大的MIMO處理功能相結合,可為運營商與用戶等提供可兌現4G承諾的SoC。

更快的協處理器可優化基站設計

自2001年以來,TI已經提供了多種由可配置硬件加速器組成的無線電協處理功能,用于接管處理需求,提升整體系統性能。此外,TI協處理器還可降低基站電源需求與消耗,以及電路板復雜性,從而可簡化新產品的設計、構建和部署。

隨著無線標準的演進和相關實施的標準化,TI無線SoC的每一次演進都讓協處理功能更加豐富,這可幫助我們的客戶在實現更高性能基站解決方案的同時降低功耗與成本。TI將DSP與ARM核同協處理器一起集成的SoC策略是實現無線基站SoC設計的最高效最經濟的方法,其將繼續保持市場領先解決方案的地位。TI各種協處理器無需外部FPGA與ASIC,便可實現3G與4G基站的高性能。

TCI6612與TCI6614具有多個專用高性能嵌入式協處理器,可執行無線基站應用常見的密集型信號處理功能。這些協處理器具體包括:4個增強型維特比解碼器協處理器(VCP2_A、VCP2_B、VCP2_C以及VCP2_D)、3個第三代渦輪解碼器協處理器(TCP3d_A、TCP3d_B以及TCP3d_C)、渦輪編碼器協處理器(TCP3e)、3個高速傅里葉變換協處理器(FFTC_A、FFTC_B和FFTC_C)以及1個位速率協處理器。將其結合在一起,可顯著加速通道編碼/解碼運算。SoC中另外還包含有4個緊密耦合的耙式/搜索加速器(RSA),可用來實現協助芯片速率處理的碼分多訪問(CDMA)。

提供完整的多核優勢

TCI6612和TCI6614SoC建立在TIKeyStone多核架構基礎上。KeyStone是第一款可實現完整多核優勢的架構,可對所有處理內核、外設、協處理器以及I/O實現順暢訪問。并可實現完整多核優勢的創新技術,其包括MulticoreNavigator、TeraNet、多內核共享存儲器控制器(MSMC)以及HyperLink等。

BCP架構

MulticoreNavigator—TIMulticoreNavigator是一款基于數據包的創新型管理器,可對SoC上各個子系統間的連接進行控制與抽象。MulticoreNavigator提供支持通信、數據傳輸以及任務管理的統一接口,可實現支持更少中斷與更簡單軟件的更高系統性能,堪稱“放棄即忘”的典范。MulticoreNavigator的優勢包括:

-

動態資源/負載共享;

可取消與子系統間通信有關的CPU開銷/延遲;

基于硬件的任務優先排序;

動態負載平衡;

對所有IP模塊(軟件、I/O以及加速器)采用統一的通信方法。

TeraNet—是一種分層交換結構,結合在一起可在SoC內部為數據傳輸提供大于2兆兆位的帶寬。這樣事實上可以保證內核或協處理器不會缺乏數據,可實現應有的處理性能。由于該交換結構是分層的,并非扁平結構,因此閑置狀態下的整體功耗非常低,可以支持最小化系統時延。而且低時延正是新一代基站的重要要求。

多核共享存儲器控制器(MSMC)—TITCI6612和TCI6614采用獨特的存儲器架構,可提高性能。TI多核共享存儲器控制器(MSMC)可讓內核直接訪問共享存儲器,無需占用任何TeraNet帶寬。MSMC可在內核與其它IP模塊之間判斷對共享存儲器的訪問,可消除存儲器爭用。代碼共享存儲器訪問可為代碼及數據提供高效率的預讀取機制,其時延非常接近本地L2訪問的時延水平。

TITCI6612/TCI6614的DDR3外部存儲接口(EMIF)是一個支持8GB可尋址存儲空間的1,600MHz64位總線。該DDR3EMIF直接與MSMC連接,不但可降低與外部存儲器存取有關的時延,而且還可為運算大量數據的更大型應用提供更快的速度與支持,從而可滿足高級3G和4G基站的應用需求。

HyperLink—HyperLink具有4個通道,每通道速率達12.5Gbaud,是一種專用的高速互聯技術,其可通過低級協議與其它KeyStone設備實現高速通信與連接,能夠為OEM廠商提供支持可擴展解決方案的無縫路徑。TCI6612和TCI6614的HyperLink與MulticoreNavigator配合,可透明地向多個設備派發任務,讓其執行猶如在本地資源上運行一樣。

TCI6612/TCI6614可作為2層2和傳輸處理引擎

TCI6612和TCI6614將無可匹敵的PHY處理功能與專用協處理器進行完美整合,支持層2及傳輸層處理。這使設計人員無需單獨網絡處理器,便可創建基站,從而可在保證性能的同時降低電路板復雜性。

該網絡協處理器能夠在傳輸網絡層以及更深的無線電網絡的2層實現快速通道處理。在SoC的網絡協處理器中,數據包加速器與安全加速器可執行全面加速的自動包對包處理。它們可充分利用MulticoreNavigator,使用零復制方法優化各層的數據處理。該網絡協處理器可全面支持分類與排序、多核可訪問存儲、存儲器管理、分段與裝配以及在多個內核與器件中進行交付等多項功能。

由于采用了快速通道與零復制處理技術,因此層2數據層及傳輸層的開銷可降低10至15倍。

最低功耗,卓越性能

TI在為市場提供最低功耗的無線基站SoC方面擁有豐富的經驗。它在每一個無線基站半導體器件中整合了其工藝技術、SmartReflexTM技術,并前瞻性地使用了電源管理技術(例如自適應電壓調節),可將工作電源降至最低,從而可實現其極限低功耗。TITCI6612和TCI6614的最新技術為小型蜂窩基站帶來了業界最低水平的SoC功耗,每Mbps數據傳輸僅為26mW。

完善的工具,全面的支持

TI可提供一整套與TCI6612和TCI6614配套的、基于Eclipse的業界最佳開發及調試工具,其中包括新型C語言編譯器、簡化編程與調度的匯編優化器、用于查看源代碼執行情況的Windows調試器界面等。TI編譯器可生成高效率代碼,能夠一次性執行通過,很少需要優化。TI調試工具可幫助開發人員實現問題的可視化,并快速解決這些問題,因此開發人員可在節約開發資源的同時更快地將產品投入應用。此外,TI還將提供評估板(EVM)幫助客戶快速進行原型設計。所有這些工具還集成ARMRSIC處理器,可幫助設計人員迅速高效地為SoC的所有子系統開發代碼。

更多詳情

如需了解有關TCI6612和TCI6614SoC的更多詳情,敬請訪問www.ti.com.cn/c66multicore,了解TCI6612和TCI6614如何為您的新一代小型蜂窩基站設計提高性能。