近年來,軟件無線電已經成為通信領域一個新的發展方向,數字下變頻技術(Digital Down Converter-DDC)是軟件無線電的核心技術之一,也是計算量最大的部分。基于FPGA的DDC設計一般采用CIC、HB、FIR級聯的形式組成。同時,由于CIC濾波器的通帶性能實在太差,所以中間還要加上一級PFIR濾波器以平滑濾波器的通帶性能。而眾所周知用FPGA從事算法的開發是一件難度比較大的工作,而Xilinx公司開發的System Generator工具為算法的快速開發及仿真帶來了巨大的方便。本文首先對CIC、HB、FIR濾波器的原理及設計作了簡單的說明,最后用Matlab結合System generator對本文所設計的DDC濾波器作了一個仿真。

1 總體結構設計

數字下變頻技術作為數字信號處理中的一個關鍵技術,它通常由以下兒部分組成。首先,CIC濾波器,它實現簡單而且能實現較大的下抽率。其次,由于CIC濾波器帶內平坦性能太差,因此在CIC濾波器之后一般要加上PFIR來平滑帶內平坦度。最后,由于CIC濾波器的抽取因子小宜取得過大,岡此還要用HB濾波器的級聯來進一步增加抽取率。下面本文以如何設計一個原信號采樣率為72 MHz的、有效信號帶寬為2.05 MHz的、下抽率為14的、主旁瓣衰減80 dB以上的、通帶平坦度小于0.2 dB的下抽濾波器為例說明下抽濾波器的設計。

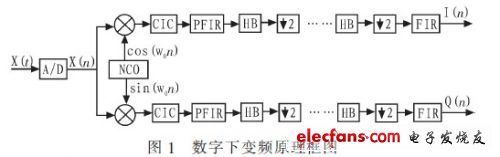

實際中常用的DDC的實現框圖如圖1所示。

2 CIC濾波器設計

CIC濾波器是近年來在下變頻中用得最多的一種技術,CIC濾波器在多速率信號處理中具有特別重要的位置,它可以充當內插濾波器,也可以充當抽取濾波器,主要取決于積分器和梳狀濾波器的連接順序。由于CIC(級聯積分梳狀)濾波器不需要乘法運算和存儲系數,因此實現非常簡單,在采樣率變換過程中經常使用CIC濾波器進行數字濾波。

考慮到CIC濾波器的除數及抽取因子不宜取得過大,所以實際巾的下抽濾波器一般都是采用CI協同HB來完成下抽的任務。比如這里我們要下抽14,一般的做法是先用CIC下抽7然后用HB下抽2 如果這時一級HB仍然不滿足要求的話,我們可以通過適當增加HB的級聯數目來完成下抽。例如,如果要下抽28,那么可以先下抽7,然后通過兩級HB來完成下抽4,進而達到下抽28的目的。

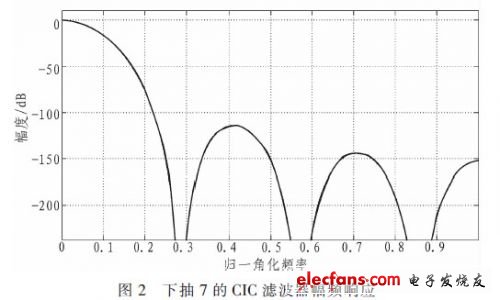

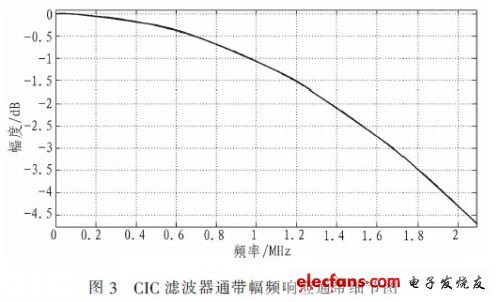

在MATLAB中通過設置下抽因子,需要的通帶截止頻率等參數可以方便的設計出想要的CIC濾波器。下圖為本次設計中設計出的CIC濾波器的幅頻響應。

通過將其通帶細節圖放大,可以發現在2.05 MHz處通帶的衰減為4.508 dB。

3 PFIR濾波器設計

PFIR濾波器的設計目標是在滿足通帶波紋和過渡帶寬盡可能窄的同時使得阻帶衰減盡可能大,PFIR的階數越高,PFIR濾波器的通帶波紋,過渡帶寬,阻帶衰減等特性就越好。

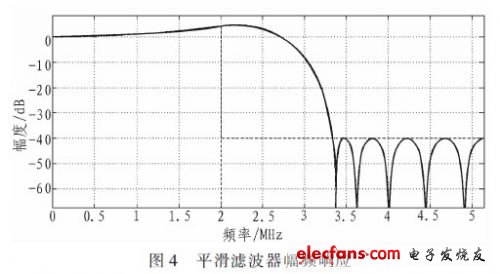

PFIR存在的意義是它能夠改善CIC濾波器帶內平坦度較差的問題,因此,其帶內的幅頻響應的走勢和CIC正好相反,從而在一定程度上平滑CIC濾波器通帶內衰減的趨勢。在設計好了上一級CIC濾波器的基礎上,通過輸入已經完成的上級濾波器參數在MATLAB中可以自動生成與其互補的PFIR濾波器,它的幅頻響應如圖4所示。

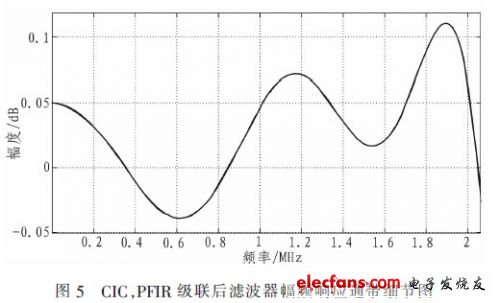

通過將這里設計的PFIR濾波器與上節設計的CIC濾波器進行級聯,級聯后的濾波器的幅頻響應較之于之前設計的CIC濾波器其通帶性能有了很大的提高,級聯前的CIC濾波器的通帶波紋為4.508 dB,而級聯后僅為0.11 dB將其通帶細節圖如圖5所示。

4 HB濾波器設計

半帶濾波器是一種特殊的FIR濾波器,在多速率信號處理中有著至關重要的作用。在常見的下抽濾波器設計中第二級一般采用HB濾波器要用到第二級的原因是綜合考慮到帶內平坦度和阻帶衰減度等因素使得第一級CIC抽取濾波器的級數和抽取因子不宜過大,HB濾波器的帶內平坦度好,計算效率高,在高速率信號處理中發揮著重要的作用,在抽取因子為2的冪次方的場合更是如魚得水。

HB濾波器的通帶和阻帶具有對稱的關系,因此其通帶波紋和阻帶波紋相等。但是使其成為數字信號處理中非常常用的一種濾波器的主要原因卻是因為其系數有一半均為0。如此,在低速率數字信號處理中或許還不是很重要,但是在那些對實時性要求非常高的系統中,這種將計算量減半的性能就使得其得到了廣泛的應用。

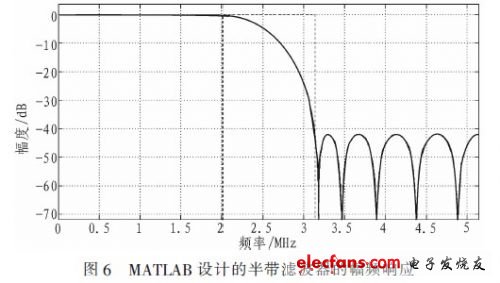

綜合考慮前方中提出的設計的要求,文中設計的HB濾波器的幅頻響應如圖6所示。

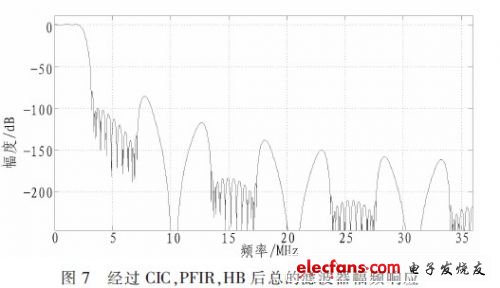

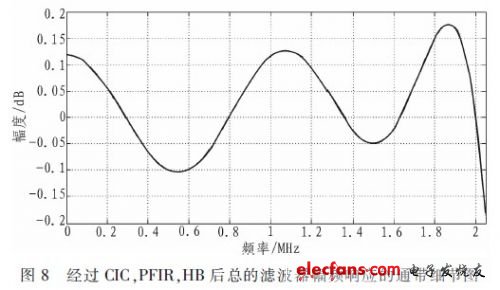

將文中設計的CIC,PFIR,HB級聯之后得到的總的濾波器的幅頻響應如圖7所示,可以發現較之于CIC濾波器的通帶性能,此時級聯濾波器的通帶性能已經有了較大的提高。其通帶細節圖如圖8所示。

5 system generator仿真

system generator for dsp是業內領先的高級系統級FPGA開發工具。本次設計是在基于Xilinx(賽林思)的system generator的基礎上完成的。賽林思是全球領先的可編程邏輯完整解決方案的供應商,它研發、制造并銷售范圍廣泛的高級集成電路、軟件設計工具以及作為預定義系統級功能的IP(InteIlectual Property)核,客戶使用Xilinx及其合作伙伴的自動化軟件工具和IP核對器件進行編程。System generator是Xilinx公司進行數字信號處理開發的一種設計工具,它通過將Xilinx開發的一些模塊嵌入到MATLAB的Simulink庫中,可以在Simulink中進行定點的仿真,可以設置定點信號的類型,這樣就可以比較定點仿真與浮點仿真的區別。并且它還可以生成HDL文件,或者網表直接供ISE調用。較之于直接用MATLAB進行算法的仿真其主要優勢作于它是基于定點的,同時,它是由各個供應廠商直接提供的庫,因此它能夠充分認識FPGA內部的資源等,其仿真也更精確可靠。

雖然,system generator能直接生成供底層FPGA調用的代碼以及網表,但是,通常并不這樣做。相對于人工編寫的代碼,system genera tor生成的代碼相對冗余度高,資源利用也不及人工編寫的代碼合理。但是,在某些需要快速進行算法開發的項目中,這種方式無疑為用FPGA從事快速的算法開發提供了一個捷徑。

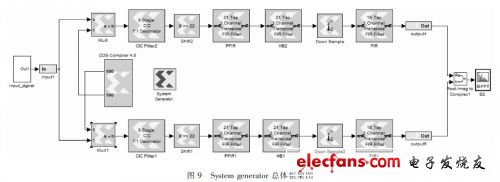

將MATLAB與system generator集成后,由圖1所示的原理框圖,搭建了用于仿真的system generator模塊,如圖9所示。

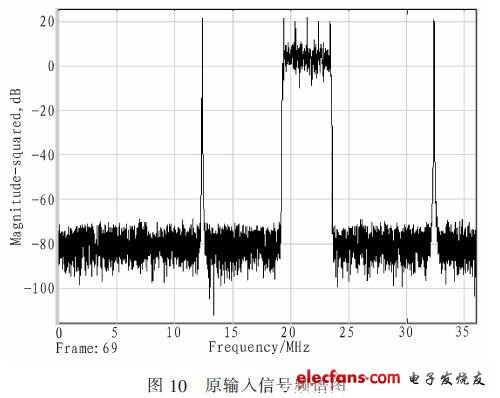

在輸入端輸入幅頻響如下圖所示的信號,其有用信號范圍173~25.5 MHz。另外為了方便仿真結果的觀察,又加入了2個大的噪聲信號分別位于32.4MHz,12.4 MHz。

將上圖所示的信號送入DDC網絡后,信號變成I/Q兩路信號,將這兩路信號組合成復數信號后得到的復數信號的頻譜圖如圖11(a)所示。

圖11(a)為原輸入信號的有用信號附近的細節圖,而圖11(b)為經過DDC網絡后得到的復數信號的幅頻響應圖。由于simulink的頻譜繪制工具顯示刷新的問題它們看起來有了一點點的誤籌,但是,也可以發現經下變頻后的信號有效的恢復了原信號的頻譜信息。它將原輸入信號的負邊頻線性搬移到了以0頻為中心的帶寬為4.1MHz的頻譜上來。

6 結束語

實際項目中接觸到的信號處理任務大多為帶通信號,如果直接采用傳統的奈奎斯特采樣定理對模擬信號進行采樣,然后進行數字信號處理任務,這樣對后端的DSP器件的實時性要求太高。因此,通常我們都要先用一個FPGA來完成數字信號的下變頻操作,之后再由后端的DSP器件來完成信號處理任務。因此,如何合理的設計DDC下變頻就顯得特別重要。本文針對如何設計DDC濾波器以及基于FPGA的System Generator的仿真都作了簡單的介紹。