User-customisable ARM-based SoCs

■ Altera公司嵌入式產品高級經理 Todd Koelling

面對當今競爭激勵的市場,嵌入式系統設計人員不得不重新審視其設計和開發過程。系統越來越復雜,性能、功耗和空間限制也越來越大,傳統的方法已經達到了極限。同時,不斷變化的標準、新出現的市場和發展趨勢都要求設計過程非常靈活,能夠積極應對這些變化。設計人員不僅需要開發更復雜的系統,而且還要能夠迅速實現新的或者衍生設計。

設計團隊有如此多的需求,因此,增加開發時間和資源以適應這些需求是合乎邏輯的,但實際上相反。越來越窄的市場窗口要求他們在更短的時間里推出更高級、更靈活的系統。更麻煩的是,經濟因素的限制也迫使很多設計團隊縮減規模,而不是增加人員。他們今后要獲得成功,關鍵是采用更高效的手段來迅速實現功能豐富的高性能自適應產品。

出現了新的解決方案

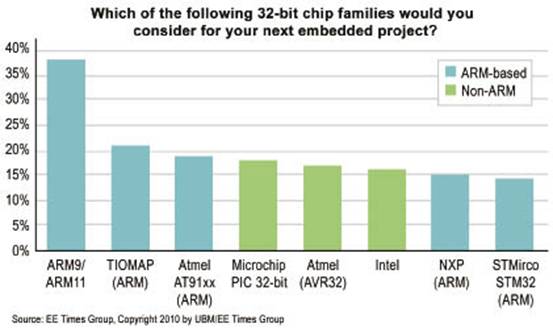

在市場開發中有利于設計人員的一面是嵌入式系統的主要平臺采用了ARM處理器。僅僅幾年前,處理器市場還是四分五裂,PowerPC、RISC、MIPS和SPARC都在競爭實現更廣泛的應用。市場現在已經非常成熟,在嵌入式應用中,很多用戶采用了ARM處理器作為實際的標準(圖1)。結果,越來越多的出現了基于ARM的解決方案,從標準產品到軟核ARM IP,直至在可編程邏輯和ASIC中實現的硬核IP等。

圖1

即使如此,通用嵌入式系統也很難滿足現代設計需求。多芯片解決方案實現起來相對容易一些,但是成本高,缺乏設計人員所要求的靈活性以及性能/功耗指標。采用了軟核處理器的單芯片解決方案實現起來也相對容易一些,但是性能有限。另一方面,ASIC SoC具有板上增強ARM內核,功耗和性能表現非常出色,但是對于大部分應用而言,由于開發時間長、不靈活,以及成本太高等問題,因此面市時間較長。

為提高競爭力,嵌入式系統開發人員需要一種能夠幫助他們開發獨具優勢產品的解決方案,非常靈活,效率也非常高。

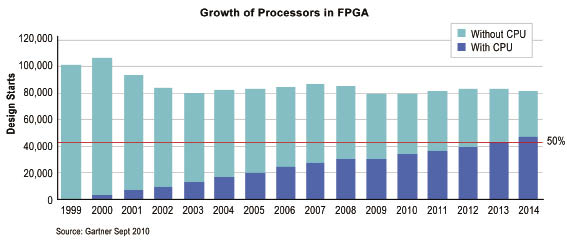

基于FPGA的單芯片實現方法具有低成本和快速面市等優點,是多芯片和ASIC SoC非常有吸引力的替代方案。實際上,在過去十年中,FPGA內置嵌入式處理器的應用在穩步增長(圖2)。但是,并不是所有基于FPGA的解決方案都能夠滿足目前苛刻的需求。傳統上,使用基于HDL的“軟核”ARM來實現基于FPGA的ARM系統。對于密度、功耗或者性能要求不高的系統,這一方法是可行的,但是不一定能滿足更復雜系統的要求。對于不斷發展的系統,在FPGA平臺上結合經過優化的硬核ARM是很好的解決方案。

圖2

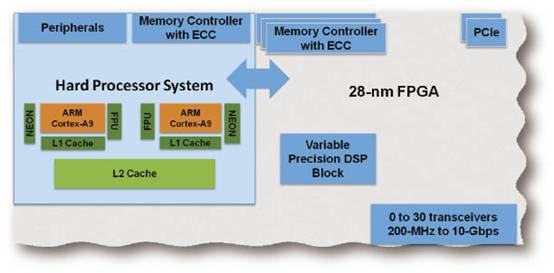

由于FPGA供應商在技術上的進步,市場上出現了新一類SoC器件,滿足了目前嵌入式系統應用的多種功能需求。基于ARM的SoC FPGA在一個SoC中結合了增強ARM處理器、存儲器控制器以及外設和可定制FPGA架構。

基于ARM的SoC FPGA (如圖3所示)在單片FPGA中緊密結合了經過優化的“硬核”處理器系統(HPS)模塊。HPS包括雙核ARM處理器、多端口存儲器控制器以及多個外設單元,處理器性能達到4,000 DMIPS (Dhrystones 2.1基準測試),功耗不到1.8 W。這些硬核IP模塊提高了性能同時降低了功耗和成本,減少了對邏輯資源的占用,突出了產品優勢。設計人員可以定制片內FPGA架構,開發專用邏輯。可編程功能支持靈活的通信標準和網絡協議。

圖3

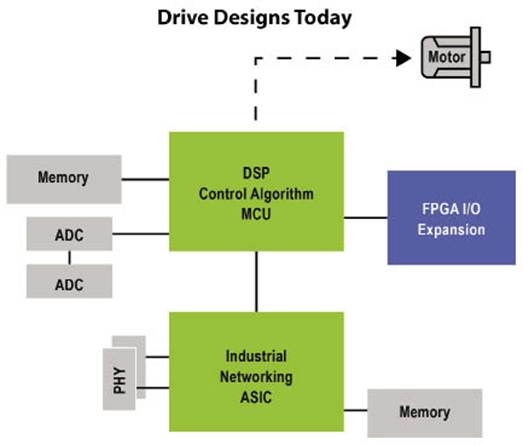

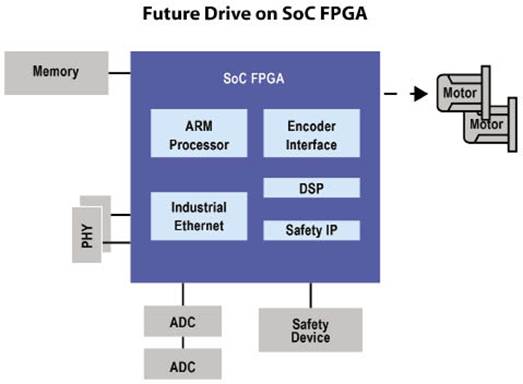

應用實例:下一代驅動

傳統的驅動設計(圖4a)會采用數字信號處理器(DSP)來實現中央控制功能,采用網絡ASIC實現網絡協議,以及FPGA用于實現其他功能(在這個例子中,是I/O擴展)。而在SoC FPGA方案中,所有這三部分單元都集成到一個芯片中(圖4b)。SoC FPGA實現方案還支持多個電機、多種網絡協議以及安全IP,擴展了現有的功能,保證了控制器能夠以安全的方式停止工作,滿足業界新出現的安全標準要求。

單芯片方法明顯增強了性能,降低了功耗。在驅動系統中,控制環速率是最關鍵的性能參數。SoC FPGA控制環速率是多芯片解決方案的20倍,從100µs減小到5µs。這意味著顯著提高了功效,對應驅動90%的總體運行成本。在這個例子中,SoC的功耗大約比三芯片方案低37%。

圖4a

圖4b

SoC FPGA增強了系統功能,通過集成降低了系統總成本。通過在一個芯片中結合三個甚至更多的驅動器,減少了系統所需的材料。在這一例子中,采用SoC也能夠將電路板面積減小57%。而且,能夠以更低的成本實現更多的功能。這一例子中的SoC支持兩個電機,而多芯片方案只支持一個。與針對每一電機來復制多芯片器件配置相比,在一個芯片上支持兩個電機能夠降低53%的成本。調整FPGA SoC來支持更多的電機和集成驅動系統以及多種協議也很容易。

關鍵點

采用FPGA SoC技術的設計團隊能夠顯著提高效能,增強競爭優勢。硬核IP單元實現了最佳性能、最低功耗和最高密度,而片內FPGA架構能夠在設計階段或者在現場迅速突出自身優勢,增強或者定制實現功能。現場可編程平臺結合了高度自動化而且提供良好支持的設計和軟件開發工具,因此,設計團隊能夠使用商用器件來開發定制SoC,開發時間要遠遠短于ASIC或者多芯片器件。最終的設計非常靈活,能夠進行更新,可以重新使用,團隊能夠迅速適應新市場和標準的變化以及快速發展的工藝節點,維持產品較長的生命周期。

目前的嵌入式系統應用與傳統的設計方法相比已經到達了一個關鍵點,基于FPGA的SoC將成為可行而且是很有優勢的解決方案。借助其強大的功能,設計人員不但能夠克服這些難以解決的問題,而且還獲得了明顯的產品及時面市、價格/性能、突出產品特點以及長壽命產品等優勢。