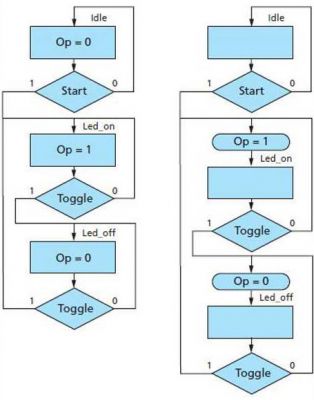

當需要定義一個狀態機時,首先要繪制一張狀態圖。狀態圖可用來顯示狀態、狀態間的轉換和狀態機的輸出。圖1 顯示了Moore 狀態機的狀態圖(左)和Mealy 狀態機的狀態圖(右)。

雖然有許多狀態機是使用圖1 所示的狀態圖方法進行設計的,但另外還有一種描述狀態機行為的方法,這就是算法狀態圖法。ASM 圖(圖2)在外觀上更加接近軟件工程流程圖。它由三個基本部分構成:

1. 狀態框。它與狀態名稱有關,并包含Moore 狀態輸出列表。

2. 決策框。如果檢驗某條件為真,則進行下一狀態的判斷。

3. 條件輸出框。讓狀態機根據當前狀態和輸入描述Mealy輸出。

實現Moore 狀態機還是Mealy 狀態機,取決于狀態機需要實現的功能,以及特定的反應次數要求。兩種狀態機之間的最大差別在于狀態機如何對輸入做出反應。在輸入和設置的適當輸出之間,Moore 狀態機一般有一個時鐘周期的延遲。這就意味著Moore 狀態機無法對輸入變化立即做出反應,這點在圖3中可以清楚地看到。而Mealy 狀態機則能夠立即對輸入做出反應,這通常意味著:實現相同的函數,Mealy 狀態機比Moore狀態機需要更少的狀態。Mealy 狀態機的不足之處就是在與另一個狀態機進行通信時,如果輸出出乎意料地嚴重依賴于其它事件的序列或時序,就可能會發生紊亂情況。

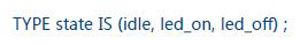

使用VHDL 這樣的高級語言,可以輕松地直接從狀態圖實現狀態機。VHDL 支持多種枚舉類型,方便您定義實際的狀態名稱。舉例如下:

• 可以避免組合過程中信號覆蓋不完全造成的閉鎖風險。

• 狀態機的輸出與時鐘保持同步。

• 通常比雙進程實現方案更容易調試。

狀態機編碼

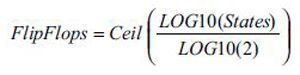

狀態變量存儲在觸發器中,使用下一時鐘邊緣上的下一狀態進行更新(即使沒有狀態變化也是如此)。如何使用觸發器來表示狀態值具體取決于狀態的數量和是否選擇用某種特定的方法來管理綜合工具。狀態編碼最常見的三種類型是:

• 順序碼——狀態編碼遵循傳統的狀態二進制序列。

• 格雷碼——除了狀態編碼使用格雷碼,且狀態編碼串之間只有一個位變化外,其它基本與順序編碼方法類似。

• 獨熱碼——這種方法在狀態機中為每一種狀態分配一個觸發器。只有一個觸發器當前設置為高位,其余均設置為低位。故稱為“獨熱”。

順序編碼和格雷編碼都需要一定數量的觸發器,可以通過下列等式來確定:

• 順序:少于5 種狀態。

• 獨熱:5-50 種狀態。

• 格雷:多于50 種狀態。

TYPE state IS(idle,led_on,led_off);

SIGNAL current_state:state:=idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state:

SIGNAL IS “sequential”;

其中“sequential”也可以是“gray”和“onehot”。您還可以通過結合使用“safe”屬性來確保在狀態機進入非法狀態時能夠恢復到有效狀態。

另外,您也可以使用syn_encoding 屬性直接定義狀態編碼的值。例如,假設您想要使用下列狀態編碼法來對三態狀態機進行編碼:Idle = “11,” led_on = “10,” led_off = “01(與較傳統的順序“00”、“01”和“10”不同)。

前面給出的等式可確定狀態機實現方案所需的觸發器數量。由于不是所有的狀態機都是2 的冪次方,因此某些狀態在設計中將不會用到。實現狀態機的工程師必須負責確保未使用的狀態在設計中得到妥善處理。可以采用幾種適用于多種設計的基本技巧來實現這一目標。對于高度可靠的安全關鍵型設計,則需要采用其它更高級的技巧。

不過對于大多數應用來說,只需要確保狀態機能夠妥善地處理未使用的狀態并在進入非法狀態時能夠正確地恢復。要做到這一點有兩種主要的方法。第一種方法是使用綜合工具實現一個安全的狀態機。綜合工具通常會插入額外的邏輯,用于檢測非法狀態并將狀態機返回到有效狀態。第二種方法是加強對實現邏輯的控制,聲明所有2 的冪次方狀態機的狀態,并使用另一屬性來確保即便是在沒有入口條件下,2 的冪次方狀態機的狀態也不會被優化掉。這意味著除非出錯(單粒子翻轉等),狀態機內部的任何條件都不會進入狀態。下面的代碼顯示了通過使用屬性以防止清除未使用的狀態。

SIGNAL IS “TURE”;

安全高效的狀態機設計對于任何使用FPGA的工程師而言都是一項重要技能。選擇Moore 狀態機、Mealy狀態機還是混合機取決于整個系統的需求。無論選擇哪種類型的狀態機,充分掌握實現方案所需的工具和技巧,將確保您實現最佳解決方案。