基于EP1C3T144C8的FPGA的開發(fā)板設(shè)計

電子技術(shù) 中國地質(zhì)大學(武漢) 劉輝

摘要: 現(xiàn)場可編程門陣列(FPGA,F(xiàn)ield Programmable Gate Array)的出現(xiàn)是超大規(guī)模集成電路(VISI)技術(shù)和計算機輔助設(shè)計(CAD)技術(shù)發(fā)展的結(jié)果。FPGA器件集成度高、體積小,具有通過用戶編程實現(xiàn)專門應(yīng)用的的功能。它允許電路設(shè)計者利用基于計算機的開發(fā)平臺,經(jīng)過設(shè)計輸入、仿真、測試和校驗,直到達到預期的效果。利用FPGA可以大大縮短系統(tǒng)的研制周期,減少資金投入。更吸引人的是采用FPGA器件可以將原來的電路板級產(chǎn)品集成為芯片級產(chǎn)品,從而降低了功耗,提高了可靠性,同時還可以很方便的對設(shè)計進行在線修改。FPGA器件成為研制開發(fā)的理想器件,特別適于產(chǎn)品的樣機開發(fā)和小批量生產(chǎn),因此人們也把FPGA稱為可編程的ASIC。

Abstract:

Key words :

現(xiàn)場可編程門陣列(FPGA,F(xiàn)ield Programmable Gate Array)的出現(xiàn)是超大規(guī)模集成電路(VLSI)技術(shù)和計算機輔助設(shè)計(CAD)技術(shù)發(fā)展的結(jié)果。FPGA器件集成度高、體積小,具有通過用戶編程實現(xiàn)專門應(yīng)用的的功能。它允許電路設(shè)計者利用基于計算機的開發(fā)平臺,經(jīng)過設(shè)計輸入、仿真、測試和校驗,直到達到預期的效果。利用FPGA可以大大縮短系統(tǒng)的研制周期,減少資金投入。更吸引人的是采用FPGA器件可以將原來的電路板級產(chǎn)品集成為芯片級產(chǎn)品,從而降低了功耗,提高了可靠性,同時還可以很方便的對設(shè)計進行在線修改。FPGA器件成為研制開發(fā)的理想器件,特別適于產(chǎn)品的樣機開發(fā)和小批量生產(chǎn),因此人們也把FPGA稱為可編程的ASIC。

可以斷定FPGA在結(jié)構(gòu)、密度、功能、速度和靈活性方面將得到進一步的發(fā)展。隨著工藝和結(jié)構(gòu)的改進,F(xiàn)PGA的集成度將進一步提高,性能將進一步完善,成本將逐漸下降,在現(xiàn)代電子系統(tǒng)設(shè)計中將起到越來越重要的作用。

1 硬件電路設(shè)計及原理

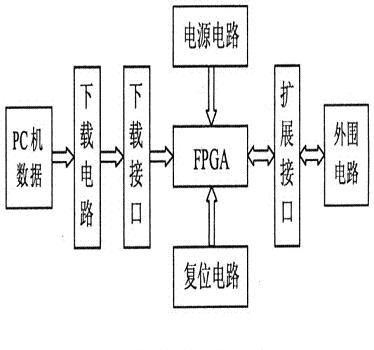

1.1 硬件電路整體結(jié)構(gòu)

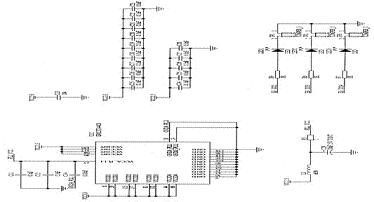

本設(shè)計的開發(fā)板電路包括6個部分:下載電路、下載接口、FPGA、電源電路、和擴展接口。其電路結(jié)構(gòu)框圖如下:

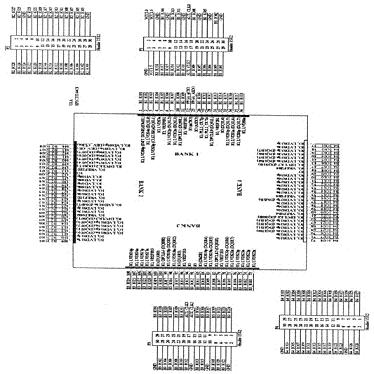

1.1.1主芯片EPlC3T144C8

Altera Cyclone系列FPGA是A1tera公司2003年9月份推出的,基于1.5v,0.13μm工藝,Cyclone是一個性價比很高的FPGA系列。其中EPlC3T144是Cyclone系列中的一員,共有2910邏輯單元,59904RAM bits,1個PLLs,最多有104個用戶I/O,可以說這款FPGA的資源非常豐富,足夠滿足大型設(shè)計的需要。

本設(shè)計選用Altera公司的Cyclone系列芯片,芯片型號為EPlC3T144C8,因為該芯片是Altera公司推出的低價格、高容量的FPGA,其以較低的價格、優(yōu)良的特性及豐富的片上資源在實際應(yīng)用中被廣泛的采用,這些都是其他同類產(chǎn)品無法相比的。

EPlC3T144C8芯片采用1.5V內(nèi)核電壓,0.33 μmSRAM工藝,與其他同類產(chǎn)品相比具有以下特點:

(1)邏輯資源豐富,邏輯單元(LE)數(shù)量為2910個。

(2)有104個可用I/O引腳,I/O輸出可以根據(jù)需要調(diào)整驅(qū)動能力,并具有壓擺率控制、三態(tài)緩沖、總線保持等功能:整個器件的I/0引腳分為四個區(qū),每個區(qū)可以獨立采用不同的輸入電壓,并可提供不同電壓等級的I/0輸出。

(3)多電壓接口,支持LVTTL,LVCMOS,LVDS等I/0標準。

(4)靈活的時鐘管理,片內(nèi)配有一個鎖相環(huán)(PLL)電路,可以提供輸入時鐘的1~32倍頻或分頻、156~417ps相移和可變占空比的時鐘輸出,輸出時鐘的特性可直接在開發(fā)軟件Quartos II里設(shè)定。經(jīng)鎖相環(huán)輸出的時鐘信號既可以作為內(nèi)部的全局時鐘,也可以輸出到片外供其它電路使用。

(5)內(nèi)有SignalTap嵌入式邏輯分析器,極大地方便了設(shè)計者對芯片內(nèi)部邏輯進行檢查,而不需要將內(nèi)部信號輸出到I/O管腳上。

1.2 設(shè)計電路模塊及原理

1.2.1 下載線電路

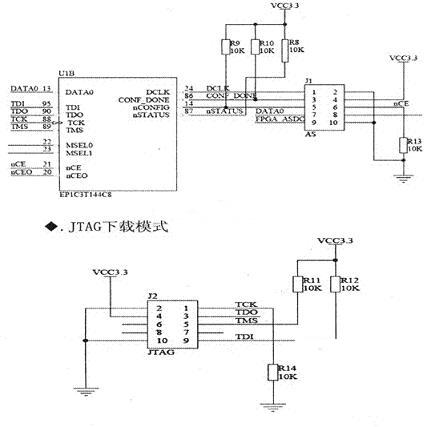

Altera器件的編程連接硬件包括:ByteBlaster并口下載電纜、ByteBlasterMV并口下載電纜、MasterBlaster串口/USB通信電纜、BitBlaster串口下載電纜。 本設(shè)計采用了ByteBlasterMV串口口下載電纜。

ByteBlasterMV串口下載電纜采用兩種下載模式:被動串行模式和JTAG仿真下載模式。

◆.被動串行模式(PS)

為了利用ByteBlasterMV并口下載電纜配置1.5VCyclone系列EPlC3T144,3.3V電源中應(yīng)該連接上拉電阻,電纜的VCC腳連接到3.3V電源,而器件的VCCINT引腳連到相應(yīng)的1.5V電源。對于PS配置,器件的VCCIO引腳必須連到2.5V或3.3V電源。對于JTAG在線配置和在線編程,電纜的VCC引腳必須連接3.3V電源。

ByteBlasterMV并口下載電纜與PC機相連的是25針插頭,與PCB電路板相連的是10針插座。數(shù)據(jù)從PC機并口通過ByteBlasterMV并口電纜下載到電路板。

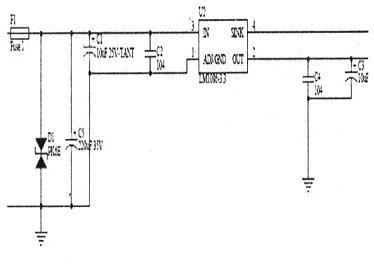

1.2.2 電源電路

采用LMl086系列芯片為電路提供穩(wěn)定的電源。LMl086是一系列工作在1.5A負載電流下,最大輸出電流為1.5A的低輸出電壓控制器。在本設(shè)計中用于為FPGA提供1.5V和3.3V電源電壓。該芯片的主要特點:

(1). 可以得到2.85V、3.3V、5.0V電壓并且有不同的版本。

(2).電流限制和熱保護。

(3).1.5A輸出電流。

該電路將5.0V的電源電壓從左端輸入轉(zhuǎn)化為3.3V從電路右端輸出,采用的芯片是LMl086IS一3.3,為電路中需要3.3V電源電壓的部分提供電壓。其中F1為保險絲,可以保護電路。D1是穩(wěn)壓管,使電源電壓更加穩(wěn)定。電路中電容均為濾波之用,C2、C4為高頻濾波電容,Cl、C3、C5為低頻濾波電容。

將3.3V的電源電壓從左端輸入轉(zhuǎn)化為1.5V從電路右端輸出,采用的芯片是LMl086IS—ADJ,該電路同上邊的電源部分原理基本相同該芯片輸出電壓可調(diào),為電路中需要1.5V電源電壓的部分提供電壓。該電路同上邊的屯源部分原理基本相同

電路的這兩部分采用了LMl086系列芯片,電路中接有濾波電容,使整個電路設(shè)計非常合理輸出非常穩(wěn)定,可以分別擔負起為電路提供穩(wěn)定的3.3V、1.5V電壓的的作用,保障了電路的正常工作。

1.2.3 電源監(jiān)控及復位電路

本設(shè)計的復位電路采用的芯片是IMP811。IMP811是低電壓電源監(jiān)控器,它的作用是用來監(jiān)控供給微處理器、微控制器和其他一些數(shù)字系統(tǒng)的3.0V、3.3V、5.OV電源電壓。在本電路中用于監(jiān)控FPGA的3.3V電源電壓,并且是復位電路的重要組成部分。它的主要特點有:

(1).6μA輸出電流。

(2).可監(jiān)視3.OV、3.3V、5.0V電源電壓。

(3).手工復位輸入。

(4).電壓低于1.1V復位有效。

根據(jù)對于該芯片的介紹可知電路的工作原理如下:

當輸入的電源電壓VCC3.3不穩(wěn)定即超出了IMP811允許的范圍時,芯片會自動由nReset輸出復位信號對電路進行保護,防止電路的元器件被燒壞另外,此電路還有手動復位鍵RESETl,可由IMP81l的nMR輸入,為電路提供手動復位信號,用于在電路不能正常工作時,將整個電路重新啟動。

1.2.4 其他電路設(shè)計

1. 本設(shè)計的各個電源都接有0.1μ退偶電容,這些電容在做板時必須擺在各個芯片周圍用來濾除電源中的高頻雜波,保證電路中各個芯片正常工作。

2. 本設(shè)計選用的晶振為50MHZ,它可以為整個電路提供時鐘信號。

3.本設(shè)計的FPGA中配有一個鎖相環(huán),由1.5V電源經(jīng)過濾波電路為其提供工作電壓。

2 結(jié)束語

本論文結(jié)合FPGA結(jié)構(gòu)原理和元件特性及EDA設(shè)計技術(shù),對開發(fā)板的設(shè)計進行了研究,完成的主要工作及成果如下:完成了基于FPGA的開發(fā)板方案設(shè)計;完成了開發(fā)板的硬件電路設(shè)計總體設(shè)計及功能模塊劃分。

本論文需要改進及進一步完善的工作主要有:

1.由電路的結(jié)構(gòu)原理可以看出,本設(shè)計只做了外圍電路的接口,沒有完成與之配套的外圍電路設(shè)計。為此,可以進一步設(shè)計更多的外圍擴展電路來實現(xiàn)不同的擴展功能。2.本論文主要針對的是開發(fā)板硬件的設(shè)計、原理,對軟件方面做的工作不多。這也是需要進一步的完善,可以通過更多的軟件設(shè)計來檢測和實現(xiàn)開發(fā)板的功能。鑒于作者時間和水平的有限,論文中必有諸多錯誤和不足,希望得到老師們的批評和指正。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。