文獻標識碼: A

文章編號: 0258-7998(2015)02-0051-04

0 引言

計算機處理圖形信息時,會遇到存儲的圖形較大,而屏幕只能顯示部分圖形的情況。比如把整幅地圖顯示在屏幕上,由于不能看到局部的細節,使用縮放技術便可以把地圖中的局部區域放大顯示[1]。在放大指定區域時,必須確定圖形中哪些部分落在范圍之內,哪些部分落在顯示范圍之外,以便顯示落在顯示范圍內的圖形。裁剪的目的正是判斷某個圖形元素是否落在窗口之內,如落在窗口之內則進一步求得位于窗口內的部分。

平面剪裁是OpenGL經典的圖形流水線的重要部件之一,也是最為復雜的部件之一。高性能的圖形處理必須通過高性能的硬件加速器來實現平面剪裁功能,本裁剪器最多支持6個裁剪面,客戶指定裁剪平面對世界空間中的物體進行裁剪,將圖元在給定平面外的部分裁剪掉,保留面內的部分,以實現特殊效果。比如,在三維視圖中標示可見面[2]、對部分圖形進行復制、移動或刪除操作防止圖形邊界混淆、從特定場景中抽取指定部分等。它在計算機圖形處理中具有重要的意義。

1 可編程裁剪器硬件設計

作為3D圖形加速器的重要組成部分,平面剪裁在計算機圖形處理中具有十分重要的意義。本剪裁器由命令解析(CMD Unit)模塊、控制電路(Ctrl Unit)模塊、裝配電路(Assemb Unit)模塊及微控制器(MCU)模塊構成,總體結構如圖1所示。可編程設計體現在用底層匯編在微控制器上運行,已完成平面裁剪功能,其余的3個模塊為外圍電路,對微控制器完成圖元裁剪起輔助加速作用,以便高效實時地完成裁剪功能。MCU采用自主研發的支持90位雙發射指令、4級流水線RSIC結構,含有4片獨立的32×256RAM數據存儲(BANK)單元,完成并行存儲的功能,即一個時鐘沿可對4塊存儲體進行讀或寫,尋址范圍是1k,應用于裁剪過程中所用數據的讀寫。本微控制器可直接在BANK中進行數據讀寫操作,避免了通過寄存器來對BANK讀寫,大大減少的讀寫數據周期,提高了運算效率。

各模塊功能如下:

(1)CMD Unit:接受GPU內部管線上一級傳來的GPU內部148位命令,如果是與平面裁剪無關的命令,則不做任何處理,將其透傳給下一級,如果與平面裁剪有關,則對命令進行解析,將矩陣和圖元信息、參數個數及屬性個數等信息存入微控制器中的數據BANK中。

(2)Ctrl Unit:利用數字電路設計常用的有限狀態機(Finite State Machine,FSM)原理控制命令解析、命令裝配模塊和微控制器間的通信,并采用雙軌握手協議完成GPU內部管線上下級間的信號交互,圖2為其狀態轉移圖。

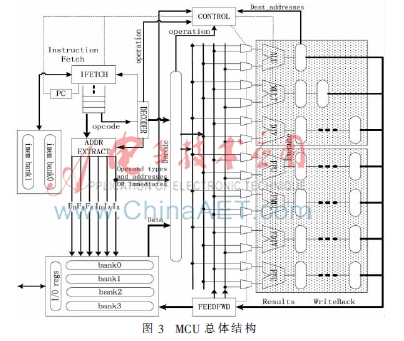

(3)MCU:本RISC處理器具有超長指令字(VLIW)結構,由指令讀取、指令解碼、執行和前饋4級流水線等組成。超長指令字的寬度為兩條RISC指令,即能夠同時解析兩條RISC指令,并將譯碼的結果發送到相應的兩條處理流水線中。將平面裁剪匯編指令固化到指令ROM,并通過數據存儲、取指單元、譯碼單元、地址流水線單元、整數和浮點數運算流水線等11個模塊實現可編程裁剪的功能。MCU結構如圖3。

(4)Assemb Unit:該模塊讀出在MCU完成平面裁剪后存儲在微控單元BANK中的圖元信息,并對裁剪后新的頂點重新裝配為148位GPU內部命令,發送到管線的下一級。

2可編程裁剪器算法和軟件設計

2.1 平面裁剪算法

與三維剪裁不同,平面裁剪通過圖元在給定的任意平面內外進行判別,對每個點只要它的視覺坐標(x,y,z,w)滿足(A,B,C,D)M-1(x,y,z,w)T≥0就于此平面內側,否則都將被裁剪掉。其中,(A,B,C,D)為平面系數,M是在調用裁剪平面時當前的模型視圖矩陣。

平面裁剪采用經典的Sutherland-Hodgman[3]多邊形裁剪算法,利用給定的平面與世界坐標系下的圖元間的位置關系,計算直線與平面的交點,并結合線性插值計算交點的屬性傳至流水線下一級,完成對圖元的剪裁。

當定義的一個裁剪面依次裁剪多邊形的每一條邊后,組成新的多邊形,再經下一個裁剪面處理,步驟相同。在所有裁剪面完成后,將保留的多邊形信息存儲在MCU的BANK中,最后重新裝配成圖元發送給管線的下一級。下面是一段基于SH裁剪算法的偽代碼。

If(the specified plane is enable) {

SutherlandHodgman(clipped primitive);

for(i=0;i<outlength;i++) {

InVertex[i] = outVertex[i];

outVertex[i].x = 0;

outVertex[i].y = 0;

outVertex[i].z = 0;

}

inlength = outlength;

}

2.2 平面裁剪軟件設計

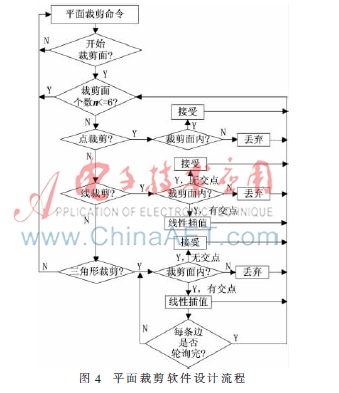

在計算機圖形學中,基本圖元只有點、線和三角形,其他任何復雜圖元均由這3種圖元構成,平面裁剪就是采用SH算法對這3種基本圖元進行裁剪,丟棄位于裁剪面之外的圖元信息,采用線性插值的算法,算出位于裁剪面內的圖元信息,并將其發給GPU管線下一級。平面裁剪軟件設計流程如圖4。

3 功能仿真驗證與原型開發

采用SystemVerilog編寫頂層測試文件,搭建相應的平面裁剪軟硬件協同驗證平臺[4],仿真使用Mentor公司的QuestaSim 6.5(Linux環境)工具,綜合使用Xilinx公司的ISE14.2工具,并選用Dini Group最新的DNV6_F2PCIE開發板進行原型開發。

3.1 功能仿真驗證

該平臺采用軟件自動比較的方法進行自動化驗證[5]。每一個測試點同時在Visual Studio 2008環境、SystemVerilog模型和HDL描述的硬件系統中運行,比較繪制結果,將模型和硬件系統作模塊級輸出比較,以確保所有功能的仿真是正確的。

根據測試點編寫的點、線和三角形的激勵,產生待測數據。將預先得到的參考結果存入FIFO中用于驗證模型的正確性。經過待測模型(DUV)進行相應的處理后生成輸出響應,與參考結果中的值進行比較,如果兩者的值相同,表示功能正確;否則標識錯誤位置,及時修改錯誤點,加速了硬件開發。圖5所示為該平臺的架構。

經過自動對比,硬件結果與仿真模型的誤差在可控范圍之內,基本完成功能驗證。

3.2 原型開發

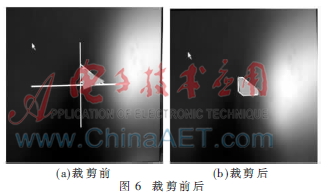

基于上述設計方案,根據電路規模和性能要求,選擇Xilinx公司的XC6VLX550T進行原型開發。選用Xilinx公司提供的綜合工具[6]ISE14.2,單獨綜合平面裁剪模塊頻率為232.504 MHz,所占Slice為14%。采用DNV6_F2PCIE FPGA開發板進行功能驗證,啟動6個裁剪面對世界空間中的物體進行裁剪前后如圖6所示。

由圖6可以看出,本裁剪器能完成基于OpenGL 1.3標準的裁剪功能,能夠高效、實時地將圖元在給定平面外的部分裁剪掉,保留面內的部分,以實現特殊效果。

4 結論

本文對可編程裁剪器的設計與實現進行深入分析,完成可編程平面裁剪器的設計與實現。通過采用SystemVerilog搭建相應的軟硬件協同仿真驗證平臺,完成了模型和HDL描述的硬件自動化驗證,加速了軟硬件開發過程,并最終在FPGA上完成原型開發與功能驗證。從中得出了以下結論:

(1)計算機和信息技術的快速發展使人們對微處理器的性能要求越來越高。可編程處理器具有高度的靈活性和成熟性,而性能也可能接近ASIC。本文所設計的裁剪器充分利用了處理器的靈活性,并采用底層匯編實現了裁剪功能,完成了實時高效裁剪圖形的目的。

(2)為提高處理數據效率,處理器還采用前饋機制,將執行后的數據和地址返回給解碼控制端。除執行本地指令流外,流水線還可執行MIMD數據流。MIMD被普遍引用于當前CPU中,本裁剪器的核心模塊微控制器就采用了MIMD的方式,提升了數據吞吐量。

(3)為了加速裁剪過程,給處理器配套外圍電路,完成命令解析,狀態控制和命令裝配。

(4)使用匯編語言描實現可編程剪裁器的圖元裁剪部分,同樣可以用匯編程序代替前后端接收(譯碼)和發送(裝配)電路,完成基于該處理器的通用剪裁器的設計工作,使其靈活性大大增強。

參考文獻

[1] 王浩鵬.二維圖形的裁剪算法研究與改進[D].西安:西安電子科技大學,2011.

[2] 孫楊.計算機輔助隱形牙齒正畸功能實現[D].杭州:浙江大學,2010.

[3] SULAND I E,HODGMAN G W.Reentrant polygon clipping[J].Communication of ACM,1974,17(1):32-42.

[4] 山蕊.基于System Verilog的可重用驗證平臺[J].電子技術應用,2013(5):38-40.

[5] 陳永光.RTL層次之系統互連線及系統電路的軟件自動化驗證方法研究[D].成都:電子科技大學,2012.

[6] 田耕,許文波.Xilinx ISE design suite 10.x FPGA 開發指南[M].北京:人民郵電出版社,2008.