文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2015.11.033

中文引用格式: 周朝陽,馮全源. 一種低功耗同步BUCK芯片的過零檢測電路設計[J].電子技術應用,2015,41(11):118-120,131.

英文引用格式: Zhou Chaoyang,Feng Quanyuan. Design of a zero-crossing detection circuit for low-power synchronous BUCK converter[J].Application of Electronic Technique,2015,41(11):118-120,131.

0 引言

近年來,同步BUCK型開關電源因高效率、低功耗的優勢被廣泛用作各種電子設備的電源,其采用同步整流MOSFET代替傳統的續流二極管,是目前比較常用的一類開關電源拓撲。同步BUCK變換器在滿負載情況時工作于連續電流模式(CCM);但在輕負載情況下,當負載電流降低至低于電感電流時,會出現電感電流倒灌現象,此時變換器需要工作在非連續電流模式(DCM)下以降低損耗。通常,同步變換器實現DCM模式是比較困難的,尤其是在高頻應用中,這時往往需要一個高速、高精度的電感電流過零檢測電路[1-3],在輕載時能及時關斷同步續流管,降低變換器輕載模式下功耗。

本文提出了一種低功耗同步BUCK芯片的過零檢測電路,采用雙電壓門限技術及門限溫度補償電路,有效限制了電感電流的倒灌。詳細介紹了同步BUCK變換器DCM工作模式及過零檢測機制,通過仿真驗證了該過零檢測電路工作性能良好。

1 同步BUCK變換器DCM工作模式及過零檢測機制

1.1 同步BUCK變換器DCM工作模式

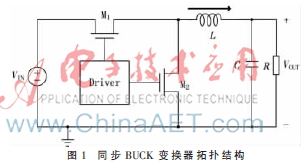

同步BUCK型變換器的拓撲結構如圖1所示,其采用同步整流MOSFET代替傳統異步變換器的續流二極管,從而極大提高電源轉換效率。其中,M1為高端開關管,M2為同步整流MOSFET,Driver信號是帶有死區時間控制的脈寬調制方波,驅動M1及M2的導通和關斷。L為儲能電感,R為負載電阻,C為輸出端電容。當Driver驅動信號為高電平時開關管M1導通,輸入電壓對電感L充電;當Driver信號為低電平時續流管M2導通,電感放電到負載R。

假設圖1中的開關管M1、續流管M2的導通阻抗分別為RON1、RON2,則在開關管M1導通時SW端的電壓VSW1可表示為:

VSW1=VIN-IL·RON1(1)

同步續流管M2導通時SW端的電壓:

VSW2=0-IL·RON2(2)

假設RON1、RON2為定值,根據式(1)、式(2)可知,SW端的電壓變化量與電感電流的變化量成線性比例關系,因此可以利用SW端電壓作為電感電流的采樣信號[4,5]。

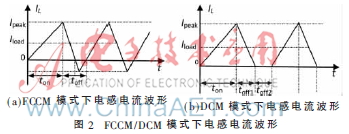

輕載情況下,同步BUCK變換器通常工作于兩種模式:強迫連續導通模式(FCCM)或非連續導通模式(DCM),圖2(a)、圖2(b)所示分別為FCCM和DCM模式下的電感電流波形。可以看出,FCCM模式中每個周期電感電流都回到零并有反向電流流通時間,而DCM模式下電流回到零后沒有反向電流流過,保持零電流至周期結束。

1.2 同步BUCK變換器過零檢測機制

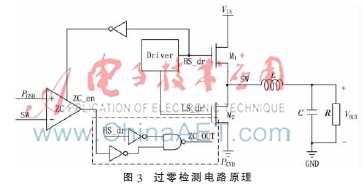

圖3所示為本文提出的同步BUCK變換器過零檢測電路原理圖。文中的過零檢測電路包括三部分:過零檢測使能電路、邊沿隱匿電路和負閾值電壓比較器。過零檢測電路使能信號如圖3中ZC_en信號所示,當變換器高端開關管驅動信號HS_dr為高電平,通過使能電路反相作用,使能信號ZC_en為低電平,整個過零檢測電路關斷;當HS_dr為低電平,ZC_en拉高,從而使能過零檢測電路開始工作。通過該使能電路,只有在高端管關閉,低端續流管開啟階段,電感電流可能會出現倒灌現象時,過零檢測電路才啟動工作,從而極大降低了系統的功耗[6]。邊沿隱匿電路如圖3中虛線框中所示,能有效屏蔽低端續流管導通瞬間SW端電位擾動對過零檢測電路造成的誤觸發。負閾值電壓比較器如圖3中ZC比較器所示,由1.1中分析可知,電感電流降低到零時,VSW也降為零,但由于變換器內部的邏輯延遲、線延遲和一些寄生參數的影響,致使VSW=0時,控制電路不能及時關斷同步續流管,仍會導致電感電流的倒灌。因此實際應用中,通常選取略低于0 V的SW電壓作為過零比較器的翻轉門限。負電壓閾值比較器檢測SW端電壓,一旦SW電位達到負電壓閾值,比較器輸出保護信號,系統將關斷低端續流管,防止電感電流倒灌[7]。

2 過零檢測電路的設計

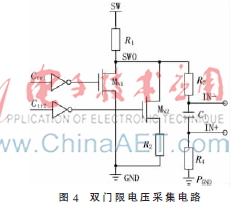

過零檢測電路主要包含兩部分:雙門限電壓采集電路和負閾值電壓比較器電路,分別如圖4、圖5所示。雙門限電壓采集電路實現對VSW和PGND的電壓采樣,采樣結果提供負閾值電壓比較器進行比較;負閾值電壓比較器比較IN+與IN-,比較結果VOUT通過Driver模塊控制低端整流管的導通或關斷。

2.1 雙門限電壓采集電路

圖4所示為雙門限電壓采集電路,當Ctr1電平為高、Ctr2為低時,MN1導通,MN2截止,VSW0≈VSW;當Ctr1電平為低、Ctr2為高時,MN1截止,MN2導通,VSW0≈R2/(R1+R2)×VSW,從而實現對VSW雙門限采集。

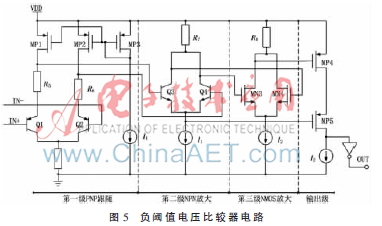

2.2 負閾值電壓比較器電路

圖5所示為負閾值電壓比較器實際電路,比較器采用兩級放大電路,分別為第二級NPN放大電路和第三級NMOS放大電路,其中第二級為電阻負載的NPN放大電路,以保證寬帶寬和低延時;第三級為CMOS放大電路,以提高增益,同時對波形進行整形;最后一級為輸出級,將比較輸出電壓轉化成全擺幅信號。第一級采用PNP跟隨電路,將兩個輸入信號抬高以達到第二級NPN放大電路的共模輸入電平下限值。

BJT放大電路與CMOS電路相比轉換速度更快,也具有更好的帶寬,因此第二級采用NPN放大電路。但BJT在集電極電流相對穩定時受溫度變化影響較大,故需要正溫度系數電流,以穩定NPN差分對的增益[8]。前兩級電流源I1為帶隙基準源提供的正溫度系數電流,后兩級電流源I2為負溫度系數電流,以降低增益和延時的溫度特性。

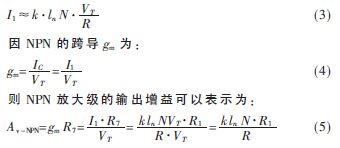

圖5中電流源I1可以表示為(其中K、N、R均為常值):

由式(5)可以看出,NPN放大級的增益和溫度無關,但第三級和輸出級是CMOS電路,受溫度影響較小。

3 仿真結果及分析

將上述過零檢測電路應用于一款同步BUCK電源芯片中,基于0.25 ?滋m BCD工藝設計,利用HSPICE進行仿真。輸入電壓4.5 V~18 V,開關頻率700 kHz,儲能電感1.5 ?滋H,輸出電容44 ?滋F,RON1=100 m,RON2=70 m。

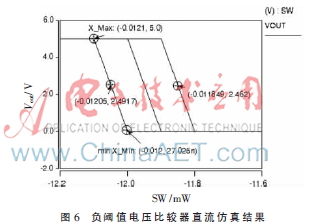

圖6所示為負閾值電壓比較器直流仿真結果。當PGND設置為0時,比較器的負閾值門限約為-12 mV,其閾值門限失調容差約為0.1 mV。當溫度從-40 ℃變化到120 ℃時,其負閾值門限容差約為0.2 mV,閾值電壓容差極小。溫度仿真結果顯示,當圖5中所示I1、I2分別為正溫度系數和負溫度系數電流源時,MP4的柵極電壓Vg1溫度系數接近于零,MP5的柵極電壓Vg2變化容差約為54 mV,比較器性能穩定。

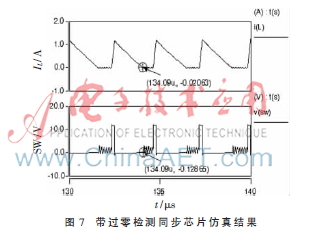

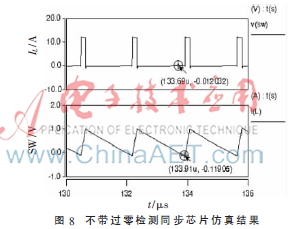

圖7和圖8所示分別為一款同步BUCK電源芯片加載和去除論文中過零檢測電路后輕載時仿真結果。可以看出:當系統中加載了過零檢測電路時,電感電流每個開關周期都要回到零,且保持零直到周期結束,開始另一個充放電周期,沒有反向電流出現,故系統工作于DCM模式;當系統中沒有過零檢測電路時,電感電流每個開關周期都有一段反向電流,故系統工作于FCCM模式。論文提出的過零檢測電路能在系統輕載時及時關斷低端續流管,極大降低了功耗,達到設計要求。

4 結論

本文設計了一種低功耗同步BUCK芯片的過零檢測電路,該電路采用兩個不同電壓門限采集技術,并對門限進行溫度補償,有效限制了電感電流的倒灌;同時設計了邊沿隱匿電路,避免電路切換時引起的誤觸發。該過零檢測電路已應用于一款同步BUCK電源芯片中,基于0.25 ?滋m BCD工藝進行設計及仿真驗證,當系統溫度在-40~120 ℃變化時,負閾值電壓門限容差為0.2 mV,實現高精度的過零檢測,且靜態功耗極低。

參考文獻

[1] LEE H,RYU S R.An efficiency-enhanced DCM buck reg-ulator with improved switching timing of power transistors[J].Circuits & Systems II Express Briefs IEEE Transactions on,2010,57(3):238-242.

[2] GAO Y,WANG S,LI H,et al.A novel zero-current-detector for DCM operation in synchronous converter[C].Industrial Electronics(ISIE),2012 IEEE International Symposium on.IEEE,2012:99-104.

[3] 嚴爾梅,韋遠武,虢韜,等.一種適用于同步整流開關電源的過零檢測電路[J].電子技術應用,2013(8):47-49,53.

[4] 王輝,王松林,來新泉,等.同步整流降壓型DC-DC過零檢測電路的設計[J].固體電子學研究與進展,2010(2):276-280.

[5] 孫毛毛,馮全源.同步整流器電流控制比較器的研究與設計[J].微計算機信息,2007(26):295-296,65.

[6] DO X D,HAN S K,LEE S G.Low power consumption for detecting current zero of synchronous DC-DC buck con-verter[J].Isocc Conference,2012:487-490.

[7] 鄒雪城,王瀟,劉三清,等.一款新穎的適用于Buck型芯片的反轉保護電路[J].計算機與數字工程,2007(10):163-165,192.

[8] 畢查德·拉扎維.模擬CMOS集成電路設計[M].西安:西安交通大學出版社,2003:15-16.