摘 要: 針對我國現階段星載計算機通用性較差和無法“即插即用”的問題,以及對數據傳輸速率的高要求,設計了新型即插即用星載計算機千兆以太網數據傳輸系統,重點研究了星載計算機的總體結構設計和千兆以太網的實現。該系統以國產BM3803為處理器,采用緊湊型外圍組件互聯cPCI總線為內總線與系統各功能模塊互連,實現即插即用和通用化功能。千兆以太網平臺采用MAC+PHY方式,MAC采用FPGA內嵌的IP核實現,PHY采用Marvell公司的88E1111芯片實現。對比國產星載計算機在以太網方面的現狀,分析表明,該系統通用性更好,數據處理性能更高,數據傳輸速率最高可達1 Gb/s。以FPGA方式實現千兆以太網設計,有效提高了系統的可靠性和集成度,能夠滿足未來較長時間國內星載計算機系統在千兆以太網方面的實際應用需求。

關鍵詞: BM3803處理器;Virtex-4 FPGA;星載計算機;千兆以太網;cPCI總線

0 引言

隨著信息技術的飛速發展,嵌入式以太網設備的應用越來越廣泛。千兆以太網作為一種高速局域網標準,具有傳輸速度快、距離遠、穩定可靠等優點,將其用在星載計算機數據傳輸系統中,不僅可以向系統提供高速數據傳輸通道,還可向其提供網絡化接口,實現與載荷網及遠端處理平臺高速通信。

同時,通過對國外衛星發射的大量成功案列調研可知,衛星從組裝建造到發射的時間已從傳統模式的數月縮短至以小時為單位,并且隨著空間技術的提高和應用需求的擴展,對衛星進行在軌維修、硬件更換、功能升級等在軌服務的需求越來越急迫[1]。而上述星載計算機在軌服務的關鍵是實現設備模塊的通用化和產品化,而模塊化設計的核心體現在接口設計上[2]。我國星載計算機的各模塊接口都是進行專門設計,導致適應性差,難以持續維護。內外接口標準不一,無法重復利用,造成開發效率低、周期長、資源浪費等問題。

針對上述兩方面的應用需求,結合現場可編程門陣列(Field Programmable Gate Array,FPGA)和千兆以太網的優點,本文設計了一種新型即插即用星載計算機千兆以太網數據傳輸系統。該系統以國產處理器BM3803作為中央處理單元(Central Processing Unit,CPU),采用CPU+FPGA的數據處理體系結構,各設備模塊均遵循標準緊湊型外圍組件互聯(compact Peripheral Component Interconnect,cPCI)內部總線實現即插即用和通用化,千兆以太網平臺采用媒體訪問控制器(MAC)+物理接口收發器(PHY)方式。MAC采用FPGA內嵌的以太網知識產權(IP)核實現,PHY采用Marvell公司的88E1111芯片實現,兩者均支持吉比特介質無關接口(GMII),部分上層協議在FPGA內部使用硬件描述語言Verilog實現。

1 BM3803簡介

BM3803是基于可擴展處理器體系結構(Scalable Processor Architecture,SPARC)即V8體系結構的32位精簡指令集計算機(Reduced Instruction Set Computer,RISC)嵌入式處理器,可用于板上嵌入式實時計算機系統,能夠滿足各種航天應用的功能以及性能指標要求,只要加上存儲器和與應用相關的外圍電路,就可以構成完整的單板計算機系統。

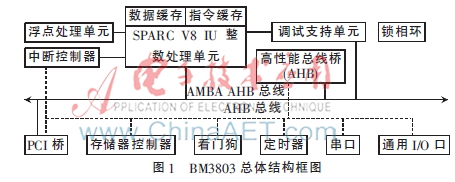

BM3803處理器總體結構框圖如圖1所示,其內部包含整數處理單元,浮點處理單元,獨立的指令和數據緩存Cache,硬件乘法器和除法器,中斷控制器,帶有跟蹤緩沖器的硬件調試單元(DSU),兩個24位定時器,通用I/O接口,看門狗;能夠支持可編程的只讀存儲器(PROM)、靜態存儲器(SRAM)、動態存儲器(SDRAM)和I/O映射空間訪問的存儲器控制器;具有軟件可以控制的省電工作模式;具有可實現PCI主機橋和從屬橋功能的PCI控制器;符合PCI2.3規范的33 MHz PCI接口;采用三模冗余、錯誤檢錯與糾錯(EDAC)和奇偶校驗的容錯設計[3]。

2 系統總體設計

星載計算機作為航天器綜合電子系統的數據管理及控制中心,承擔著衛星姿態與軌道控制、星務管理、有效載荷數據管理與處理等任務[4]。根據任務和功能需求,同時兼顧系統標準通用化,本文將星載計算機數傳系統劃分為電源管理模塊、大容量存儲模塊、CPU控制模塊、千兆以太網模塊、模擬量采集模塊以及總線通信模塊等。根據BM3803處理器手冊和PCI規范,一級PCI總線上最多可支持7個PCI設備模塊。CPU控制模塊為PCI總線的主控模塊,其他模塊為從屬模塊,每個模塊上含有一個PCI橋芯片以支持PCI協議規范。各功能模塊在電氣和邏輯上通過標準6U cPCI底板總線實現互連。星載計算機系統硬件結構框圖如2所示。

以下對每個模塊的功能和組成進行說明。

(1)CPU控制模塊

該模塊是星載計算機數據傳輸系統的核心模塊,包括BM3803處理器、SDRAM數據存儲器和外圍電路。其PCI接口配置為主機橋模式,結合軟件可以訪問和配置cPCI總線上的其余設備模塊,同時為這些設備提供總線仲裁。

(2)大容量存儲模塊

該模塊主要對內總線上高速數據進行存儲和備份,主要由cPCI接口電路、DDR2和E2PROM緩存電路、存儲控制電路組成。

BM3803主控板提供25 MHz的有源晶振,FPGA上電復位及啟動配置后,FPGA與CPU通過cPCI內總線進行數據和地址互連,CPU發送讀寫指令,由FPGA實現對指令的譯碼。根據譯出的指令,發送片選讀寫信號,實現對外擴大容量存儲模塊的控制。

(3)總線通信模塊

該模塊包括多個1553B總線芯片,以1553B總線控制器或遠程終端的方式進行通信連接。總線通信模塊的PCI接口配置為從機橋模式。考慮到該系統CPU中的PCI中斷源數量有限,當有多個總線芯片工作時,采用分立元件對多路1553B總線中斷源進行判別與合并,同時可分別清除每個中斷源狀態信息[5]。

(4)模擬量采集模塊

該模塊是將采集到的模擬信號、雙電平信號和溫度信號,轉換成數字信號并通過內總線cPCI送至CPU主控模塊處理。主要由差分放大器、多路選擇器、電平比較器和模數轉換器組成。利用多路選擇器將多路模擬信號進行分時選通,經信號放大及模數轉換實現高速數據采集[6]。

(5)電源管理模塊

由于系統自帶的開關電源(DC/DC)模塊可變換為 +5 V的二次電源,進入到各設備模塊,會產生其余各檔二次電源,如3.3 V,2.5 V,1.8 V,1.2 V,1 V,以此來滿足各電路芯片要求的電源電壓。電源管理模塊就是將+5 V電源,借助三端穩壓器轉換成各模塊所需的電源電壓。

(6)千兆以太網模塊

根據計算機網絡基本模型,實現以太網數據傳輸的關鍵在于實現數據鏈路層協議和物理層協議,即MAC控制器和以太網接口,本文采用FPGA方式實現。

千兆以太網通信接口功能,通過調用IP核在FPGA上搭建三態以太網MAC,在片外配置三態以太網物理層芯片PHY,配合對傳輸控制協議/因特網互聯協議棧(TCP/IP)移植以及基于用戶數據報(UDP)協議編程,實現以太網應用。

3 千兆以太網設計

3.1 物理層芯片

本文中物理層PHY芯片選用Marvell公司生產的88E1111千兆網絡物理層設備,該芯片具有以下功能[7]:

(1)能夠支持1000BASE-T、100BASE-TX和10BASE-T的應用;

(2)支持MAC通信的吉比特介質無關(GMII)、RGMII、串行GMII等接口;

(3)支持10 Mb/s,100 Mb/s,1 000 Mb/s的以太網傳輸;

(4)提供IEEE 802.3u標準下的自動協商機制,能夠實現兩個網絡接口間對通信速度的自動協商;

(5)提供標準的TWSI和MDC/MDIO接口,控制和查看網絡芯片的狀態;

(6)采用了先進的混合信號進程實現均衡執行、消除回聲和傳音、數據恢復和錯誤校正;

(7)采用0.13 m CMOS工藝,支持2.5 V、1.2 V低電壓供電,最大功耗為0.75 W,且支持自動降功耗功能。

3.2 硬件設計

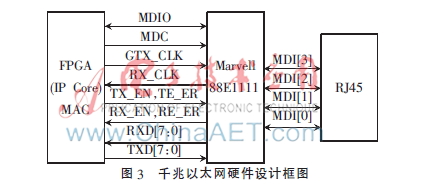

通過調用FPGA內部IP核實現MAC功能,由88E1111芯片內部的時鐘電路產生125 MHz時鐘提供給GMII接口,其與PHY連接后,轉接到RJ45物理接口實現網絡數據傳輸。千兆以太網硬件設計框圖如圖3所示。

PHY芯片88E1111提供了GMII接口,MDIO控制PHY芯片的接口形式,MDC控制MDIO方向,GTX_CLK向88E1111提供125 MHz的外部輸入時鐘。發送端GTX_CLK是MAC的發送時鐘,供TXEN、TXER和TXD[7:0]使用。TXEN為發送使能信號,TXER為發送錯誤標志,TXD[7:0]為發送的數據。

接收端RX_CLK是MAC的接收時鐘信號,供RXEN、RXER和RXD[7:0]使用。RXEN為接收使能信號,RXER為接收錯誤標志,RXD[7:0]為接收的數據。

3.3 軟件設計

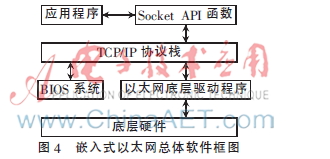

嵌入式以太網通信接口的總體軟件結構,主要包括應用程序、Socket API函數、TCP/IP協議棧、底層驅動、嵌入式操作系統、底層硬件等部分,框圖如圖4所示。

以太網的底層驅動程序是實現TCP/IP協議棧的必要前提條件,以太網驅動程序封裝了底層硬件的細節,使得TCP/IP協議不用直接與硬件交互,通過調用以太網驅動程序即可實現數據的收發。

TCP/IP協議棧是整個軟件設計的核心,而Socket API函數是TCP/IP協議棧與應用程序的接口,應用程序調用這些函數即可實現TCP/IP功能。嵌入式操作系統BIOS主要負責軟件的任務調度、存儲管理等。

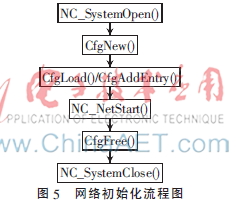

在一個網絡程序執行之前,TCP/IP協議棧必須正確配置并初始化。網絡控制模塊(netctrl.lib)是協議棧的配置、初始化和事件調度的核心。幾乎所有網絡控制活動都發生在netctrl任務線程(也稱為“調度線程”)中。該線程通過BIOS配置工具或者通過BIOS API函數來創建。該線程是程序的入口,并最后演變成“調度線程”直到程序結束該線程才返回。網絡初始化過程所用函數及順序如圖5所示。

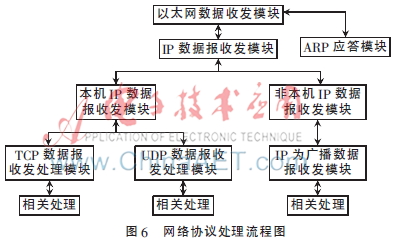

網絡配置完成之后,需要創建網絡任務進行網絡的傳輸,本文網絡發送以及接收采用面向連接的套接字(Socket)編程。網絡協議處理軟件主要實現接收和發送千兆網絡數據功能;對接收的以太網數據進行TCP/IP網絡解析,并緩存和轉發有效載荷;接收來自外圍接口數據,進行TCP/IP網絡組幀,完成千兆網絡的發送。網絡協議處理流程圖如圖6所示。

本文硬件設計中,FPGA芯片的MAC通過MDC/MDIO接口控制88E1111,再經MDI[3:0]±管腳與RJ45連接器相連實現高速網絡數據傳輸。同時在兩者之間添加濾波電路,防止直流串擾、噪聲和靜電干擾,從而提升網絡通信質量。該以太網數據傳輸系統實行單路收發,全雙工通信。在單板測試時,系統數據傳輸穩定可靠,物理速率理論最高可達1 Gb/s,實際有效速率可達800 Mb/s。

4 總結

本文創新性地結合星載計算機功能模塊間的即插即用性和千兆以太網兩方面的應用需求,設計了新型即插即用星載計算機千兆以太網數據傳輸系統。其各功能模塊遵循標準cPCI內總線,實現計算機硬件模塊化、標準化。千兆以太網以MAC+PHY為核心,通過軟硬件設計完成網絡協議棧移植和網絡傳輸數據處理,最終實現實測有效數據傳輸速率約為800 Mb/s。利用千兆以太網數據傳輸系統將處理的高速信號從網口發送給遠端處理計算平臺,可節省功率放大器和高頻電纜等物理設備,減少資本投入,加強系統的集成性和可靠性。該星載計算機系統接口更具通用性和可擴展性,在未來較長時間內都將滿足星載計算機等航天設備在千兆以太網方面的應用需求。

參考文獻

[1] SHOEMAKER J, WRIGHT M. Orbital express space operations architecture program[C]. International Society for Optical Engineering E, Orlando: The International Commission for Optics, 2003:1-9.

[2] 楊希祥,張為華.衛星公用艙模塊化及其即插即用技術研究[C].2008年全國博士生學術論壇.北京:國務院學位辦公室,2008.

[3] 北京微電子技術研究所.BM3803MG32位空間處理器用戶手冊,Ver2.4.2[Z].北京:北京微電子技術研究所,2010.

[4] 郭碧洲.基于軟件表決的三模冗余星載計算機體系結構研究與設計[D].上海:上海交通大學,2011.

[5] 詹盼盼,郭廷源,高建軍,等.基于BM3803處理器的即插即用星載計算機系統設計[J].航天器工程,2013,22(6):92-96.

[6] 李偉,劉麗紅,牟文秀,等.基于BM3803的星載計算機標準化設計與實現[J].航天器工程,2012,21(2):68-72.

[7] Marvell Corporation. 88E1111 datasheet integrated 10/100/1000 ultra gigabit Ethernet transceiver[R]. US: Marvell Corporation, 2004.