隨著數據帶寬需求的持續增長,數據傳輸從并行變成串行,收發器的速率越來越高,無論在單板內或者通過光纖和背板傳輸,都會帶來一系列信號完整性問題。信號完整性,是指系統電路在信號傳輸過程中保持信號時域和頻域特性的能力。如果信號經過信號線傳輸后依舊能保持其正確的功能特性,即信號在電路中能以正確的時序、幅度、相位等做出相應的動作,就表明該電路有較好的信號完整性。反之,就是信號完整性是有一定的問題的。信號完整性問題如何解決,如何保證誤碼率滿足協議要求,從芯片選型、電路設計,再到PCB Layout的全過程都需要考慮。

一、高速Serdes信號完整性的問題和影響

1、高速Serdes信號完整性的問題

通常電信號在PCB上傳輸的時候主要涉及兩個方面反射和插入損耗設計要求考量。

a、反射

反射是指在電信號傳輸時,每一時刻都會遇到一個傳輸線的瞬時阻抗,當該瞬時阻抗發生變化時,一部分信號將會反射,另一部分將會繼續向前傳輸;或者說反射就是回波,信號功率的一部分傳輸到線上并達到負載端,但是有一部分反射會回到源端。

反射主要是由阻抗不匹配和stub引起的。例如線寬不一樣,就會引起阻抗不匹配,信號傳輸中經過的耦合電容、過孔等位置都是會引起阻抗不匹配。

b、插入損耗

插入損耗是由介質損耗、導體損耗、導體表面粗糙度等原因引起來的損耗。不同的介質具備不同的插入損耗。背板設計的時候通常采用M4/M6板材取代FR4板材,雖然M4/M6板材成本也比較高也會比較貴,但是對應插入損耗遠遠優于FR4板材。

2、高速Serdes信號完整性的問題影響

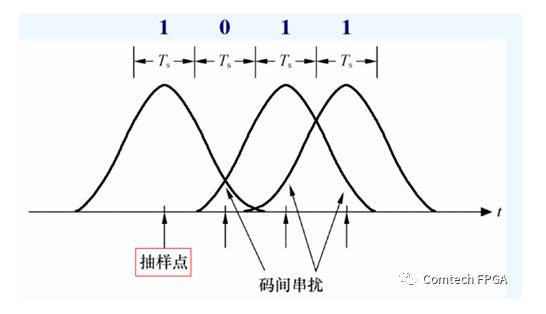

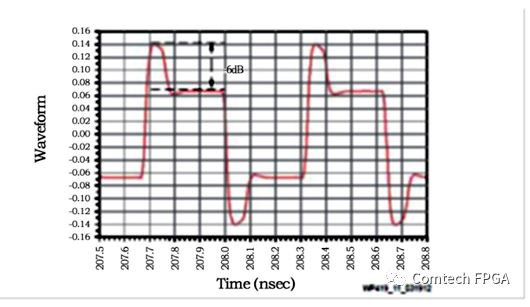

我們發送的數據有高中低等多種頻率,其中信號頻率越高,插入損耗就越大。信號經過線路的傳輸,高頻成分被衰減得更多,會導致碼間干擾的產生。 碼間干擾,又稱ISI(Intersymbol interference),顧名思義是不同信號(碼元)之間的干擾。碼間干擾造成的后果是前一個bit的波形延伸到了后一個bit位置。在發送側我們發送的bit是0-1-1-0,經過傳輸后最后一個1的波形延伸到后面一個0的位置,會造成0的電壓變高,判決時候可能判決成1,這樣本來發送的0-1-1-0,在接收端判決成0-1-1-1。這就是碼間干擾。碼間干擾的主要原因就是高頻成分損耗大,低頻成分損耗小。

圖一 碼間干擾

二、AMD-XilinxFPGA解決傳輸中的信號完整性方案

AMD-Xilinx FPGA在發送端使用了輸出擺幅、預加重、去加重等技術,其中輸出擺幅通常是用來增加信號的幅度;在接收端使用了均衡技術。

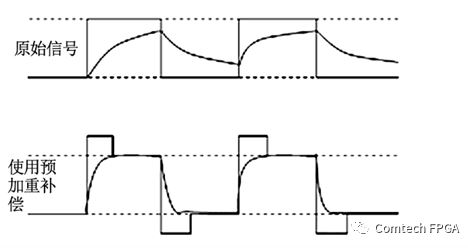

1、預加重后加重技術

為便于信號的傳輸,而對某些頻譜分量的幅值相對于其他分量的幅值預先有意予以增強的措施。 預加重是在電平轉換開始前有意過量驅動。信號傳輸線表現出來的是低通濾波器特性,傳輸過程中信號的高頻成分衰減大,低頻部分衰減小,預加重技術的思想就是在傳輸新的始端增強信號的高頻成分,以補償高頻分量在傳輸過程中的過大衰減。信號的高頻分量主要出現在信號的上升沿和下降沿處,預加重技術就是增強信號上升沿和下降沿的幅度。

圖二 預加重信號變化

我們從時域上看去加重對波形的影響,看上去波形更奇怪一些,所以去加重有些像無線通訊中的一個術語“預失真”。

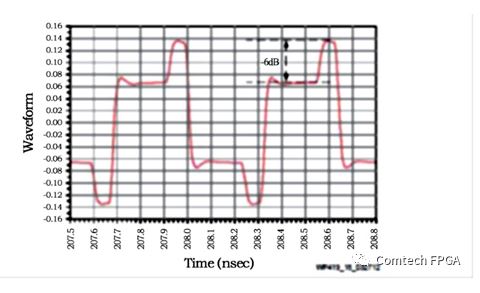

圖三 預加重時域波形

圖四 后加重時域波形

我們可以看到pre-cursor和post-cursor處理的位置不同。預加重是在信號變化前處理,后加重是在信號變化后處理。

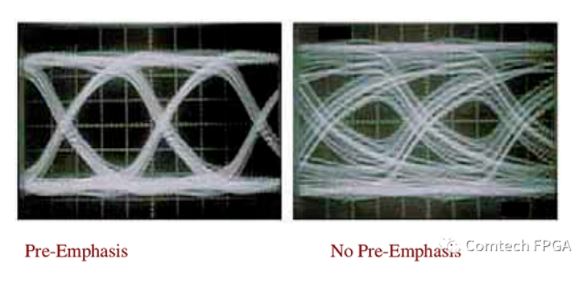

圖五 使用預加重前后眼圖對比

從圖中我們可以看到,左邊是經過去加重的接收眼圖,右邊是沒有經過去加重的接收眼圖。我們可以看到眼圖的“眼睛”變得更大了。

2、 接收均衡技術

對于GTX/GTH收發器,基于系統級的功耗和性能的權衡,有兩種類型的自適應濾波可用:

·功耗優化和低通道損耗的低功耗模式LPM

·均衡更低損耗通道的判決反饋均衡模式DFE

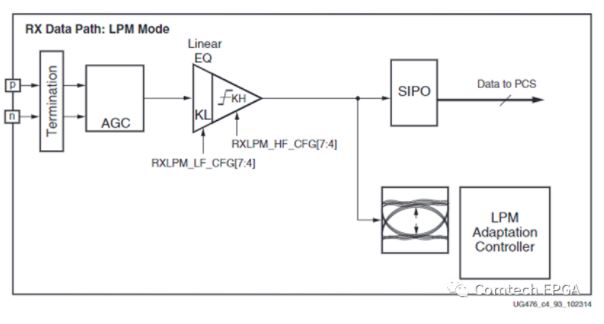

a、LPM

LPM模式下應用接收的線性濾波器,可衰減低頻信號分量,放大奈奎斯特頻率附近的分量,并衰減更高頻率,這樣就抵消了通道的低通特性。

圖六 Serdes LPM Mode

可以調整連續時間線性均衡增益以優化低頻衰減與高頻放大的比率。缺點則是放大高頻分量的同時噪聲和串擾也被放大。

在GT Wizard中選擇LPM 模式參數已經是自動調整模式,不需要我們去設置。

LPM模式的功耗比DFE模式小10%-15%,在通道損耗小于12db時候建議使用LPM模式。板內互聯情況下通道衰減基本上都小于12db,使用LPM模式是一個比較好的的選擇。

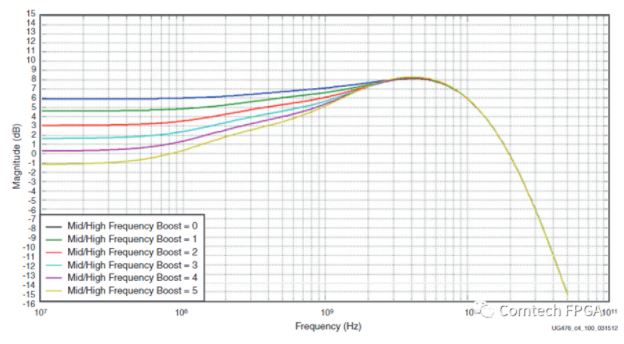

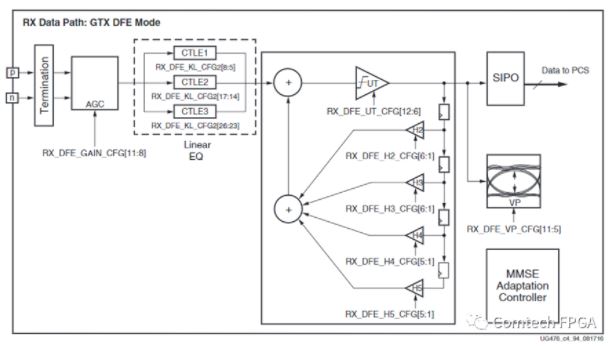

圖七 AMD-Xilinx FPGA 線性均衡響應曲線 b、DFE DFE模式通過提供更接近的調整濾波器參數,提供更好的傳輸通道補償。但是,DFE模式不能移除發送bit的預加重,只能補償post-cursor。線性均衡GTX/GTH RX DFE模式是一個離散時間自適應高通濾波器,該濾波器系數TAP由自適應算法設置。

圖八 AMD-Xilinx FPGA Serdes DFE Mode

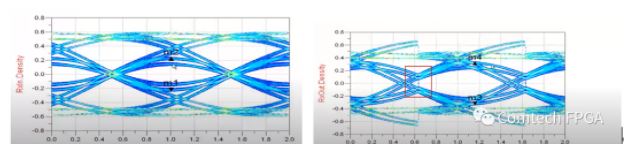

圖九 使用DFE前后對比

左圖不使用DFE均衡,右圖是使用DFE均衡后,眼圖張開的比左圖要大,紅圈位置是數據的變化沿,DFE延遲0.5個UI,因此在下一個數據的跳變沿就開始減去前一個bit帶來的影響,而不是只在數據的采樣位置才作用,這樣眼圖都變大了,所以DFE的眼圖看起來有不連續性。

c、LPM和DFE模式的選擇

DFE模式推薦用于中長距離應用,在奈奎斯特頻率下的信道損耗為8dB或者以上。DFE和CTLE相比不會放大噪聲和串擾,數據經過衰減很大的通道后接收的數據信號幅度已經很小了,這個時候高頻的噪聲和串擾對信號影響就會很大。 目前DFE的參數在FPGA中都是算法自動調整,不需要我們去設置。在使用8B10B編碼的協議而且數據沒有加擾的情況下,如果線路上長時間發送固定碼型會使得DFE自動調整算法漂移,引起負面效果。因此在8B/10B編碼而且數據沒有加擾的協議里面是不建議使用DFE的。而更高速的協議都是64B/66B、128B/130B編碼, DFE一般用在這種場合。

另外,在高速收發器通過背板連接的應用中,因為過孔和連接器阻抗不匹配引起反射,通道的衰減就像圖中淺綠的線,在某些頻率點衰減很大。在這種情況下CTLE的效果就比較差,DFE的效果就會比較好。

更多信息可以來這里獲取==>>電子技術應用-AET<<