半導體行業的發展離不開行業的共識,而行業的共識往往體現在行業所公認的路線圖里面。在上世紀末,美國的半導體工業協會SIA聯合歐洲和亞洲的半導體行業,開始發布大名鼎鼎的國際半導體技術路線圖(ITRS)。ITRS主要的貢獻是通過協調全球的半導體行業,發布了在21世紀初十多年中的芯片技術路線圖,包括特征尺寸,功率密度,邏輯門密度等等。到了2015年,隨著傳統基于2D CMOS特征尺寸縮小的摩爾定律的發展到了尾聲,ITRS也不再更新,因此2015年版本就是ITRS的最后一個版本。在當時,作為ITRS的牽頭方之一,SIA發表聲明將會在未來合適的時候發布新的半導體路線圖。而在上周,SIA和SRC聯合發布了微電子和高級封裝路線圖,作為ITRS的后繼者。

MAPT路線圖主要針對未來十年左右(2023-2035)的時間范圍,首先分析了時間范圍內對于芯片行業的應用需求,包括主要驅動應用、能效比需求以及安全需求,并且根據這些需求,分別分析了半導體各細分行業(數字處理、高級封裝和異構繼承、模擬和混合信號半導體、硅光技術和MEMS、半導體工藝、設計建模和測試標準、半導體材料以及供應鏈)需要所對應的技術進步來滿足這些需求。

首先,MAPT路線圖分析了未來十年內預期對于半導體行業最重要的驅動應用,其中最重要的包括:

數據中心和高性能計算

汽車電子

物聯網和邊緣計算

移動通信

生物計算

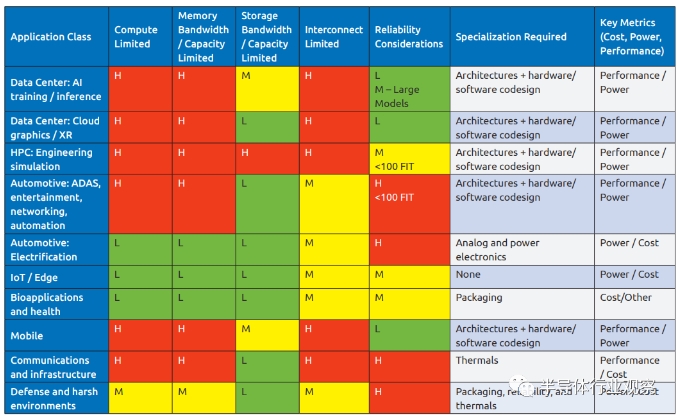

在MAPT路線圖中,分別列出了不同的驅動應用主要的瓶頸、需要的專門技術以及最關鍵的指標。從分析中,我們可以看到,計算和存儲瓶頸將會成為未來驅動應用中最關鍵的瓶頸,另外互聯帶寬也在幾個重要的驅動應用中成為瓶頸;而在核心指標方面,最關鍵的指標基本都指向了性能和功耗。因此,從驅動應用的角度,未來十多年間半導體芯片行業進步的方向也就很明確了:通過進一步提升計算、內存和數據互聯性能以滿足幾大重要驅動應用的需求,同時通過優化設計來實現對于功耗的要求。由于性能和功耗同時都很重要,能效比這一指標可望會成為未來十年間半導體芯片領域最關鍵的指標——事實上,在MAPT路線圖中,“能效比”這個詞就被重復了接近120次,可見其重要程度。

數字芯片:邏輯密度增速減慢,架構創新驅動技術進步

數字芯片向來是半導體芯片中最核心的品類,其出貨量大,對于半導體芯片工藝的依賴度高,往往是驅動整個半導體行業發展的核心芯片品類;因此在在MAPT路線圖中,對于數字芯片相關的路線圖分析也是最詳實的。

在關于數字芯片的路線圖中,我們首先看到了和以往摩爾定律所預測的截然不同的數字。MAPT路線圖預計,未來十年,晶體管密度將從目前的200億每平方厘米增加到800億每平方厘米,即10年增加4倍。在過去,摩爾定律預測每18個月晶體管密度翻倍,因此10年間晶體管密度應該增加64倍以上,這樣來看根據MAPT的路線圖預測,未來晶體管密度的增長速度會遠遠低于之前摩爾定律的速度——未來十年的晶體管密度上升速度,僅僅相當于過去三年的水平。

而如果我們仔細看最近幾年的半導體工藝演進的話,我們可以發現事實上晶體管性能(即門延遲)的改善甚至更落后于之前摩爾定律所預測的每18個月提升40% - 目前來看每代工藝演進在集成度翻倍的同時,晶體管性能僅僅提升10-20%之間,而在未來這個數字甚至會更小。因此,從MAPT路線圖中,我們可以大概估算出,未來十年中,隨著晶體管集成度翻四倍,晶體管的性能提升大約在20-30%左右。換句話說,數字芯片性能提升基本不能依靠晶體管性能提升,而是要依靠其他的方法。

在MAPT中,數字邏輯未來的進步主要靠架構上的進步。MAPT提出主要的進步方向包括:

進一步提升集成度:由于半導體工藝進步在未來十年中對于邏輯密度的提升貢獻有限,為了進一步提升集成度,主要需要依靠高級封裝技術。高級封裝技術可以用不同的堆疊方式(2.5D以及3D)把不同的芯片粒(chiplet)集成在同一個封裝里并且可以解決先進工藝的良率問題,因此可望在未來中高端芯片中得到更廣泛的應用。

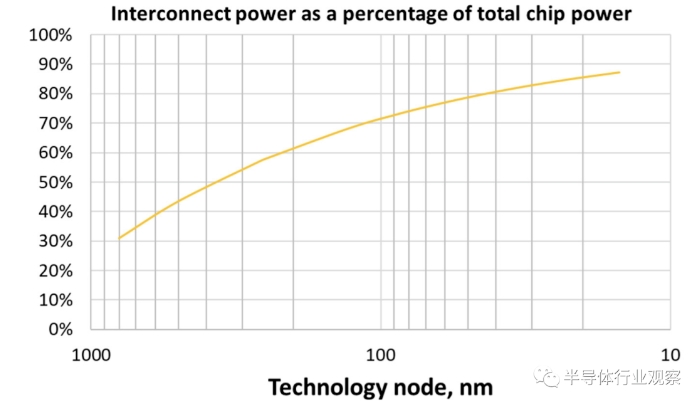

降低數據移動開銷:隨著未來芯片集成度越來愈高(即邏輯越來越復雜),數據互聯的開銷將會成為芯片性能和能效比的主要瓶頸;例如,根據之前的研究,在10nm節點,高復雜度的SoC中數據互聯的功耗開銷已經占到整個芯片功耗的90%左右,而未來隨著復雜度和集成度進一步提升,數據互聯將會越來越成為瓶頸。為了解決這個問題,一方面需要使用高級封裝技術——例如,通過3D堆疊,互聯的物理距離會大大降低(因為可以垂直走線),從而降低功耗;另一個重點則是通過新的架構,例如近內存計算和存內計算,來降低開銷;最后,模擬和混合信號電路的創新也能降低數據移動的開銷。

使用更多的專用設計架構(domain-specific design)來取代通用設計——例如使用AI加速器來進行人工智能相關的計算(而不是使用通用架構例如CPU和常規GPU),這樣做可以大大改善能效比。當使用專用設計的架構時,軟硬件協同設計就將成為一個核心概念,因為在設計專用架構時,需要考慮軟件和應用層的實際需求(例如對于AI加速器來說,就是專用數制和特定算符的支持),從而實現高效率。另外,使用專用架構時,可以使用芯片粒技術,把不同的架構使用多個芯片粒實現,并且使用高級封裝技術集成在一起。

從以上分析可以看出,MAPT對于數字邏輯電路的進一步演進是以高級封裝技術為主線,使用基于高級封裝技術進一步提升集成度、降低數據移動開銷并且實現專用架構設計的集成,從而讓芯片性能和能效比在未來十年中繼續摩爾定律時代的指數級提升。

高級封裝技術:技術快速演進成為行業支柱

正如MAPT在數字邏輯章節的分析,高級封裝將成為未來半導體的主旋律。

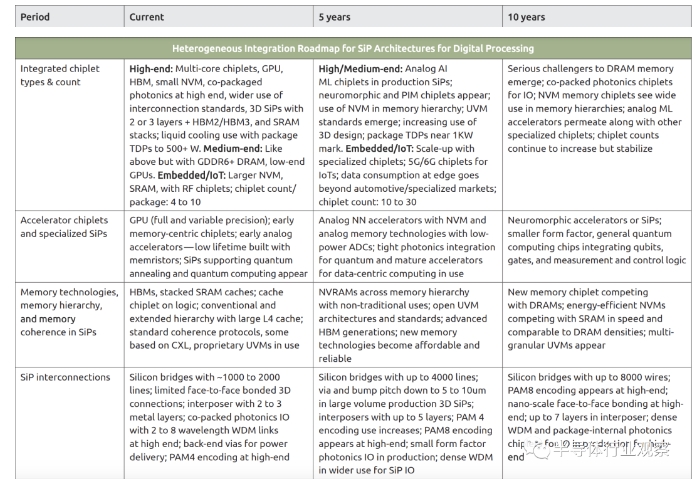

例如,在未來五年中,一個系統中芯片粒的數量將從今天的4-10提升到10-30(提升3倍),預計在十年的時間內芯片粒數量會提升更多;在內存角度,芯片粒將會實現新的內存架構,從而改善內存墻問題,到時候希望內存的容量、速度和功耗將不再成為整個系統的瓶頸;在互聯方面,未來10年高級封裝的互聯線數量將從今天的1000-2000上升到8000,另外使用新的IO接口技術(例如PAM8,以及高密度WDM光學互聯)來進一步提升數據帶寬并降低數據移動開銷。

這些需求具體對應到高級封裝的技術演進,MAPT在高級封裝章節提出了未來十年的技術演進方向。

我們認為,在高級封裝未來十年中,最關鍵的技術演進包括:

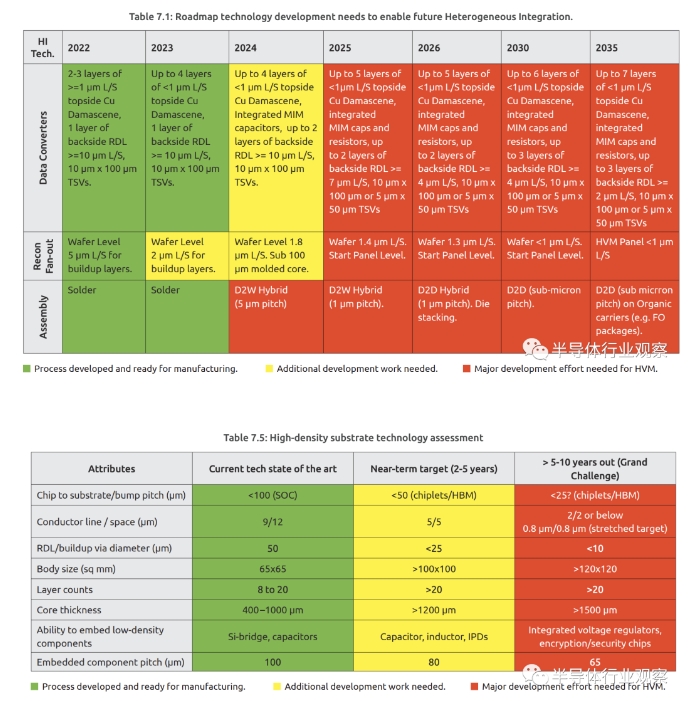

進一步提升IO密度:將芯片粒之間的bump(焊球)間距從100微米降低到25微米,從而將IO密度提升16倍。

進一步提升IO互聯線密度:這里的互聯線密度包括在晶圓正面將今天的2-3層線間距大于1微米的頂層銅互聯發展到7層線間距小于1微米的銅互聯,晶圓背面的RDL層互聯從一層上升到三層互聯并且將線間距從10微米降低到2微米;以及在晶圓間的互聯線間距從5微米降低到1微米,即互聯線密度提升25倍。

革新集成鍵合技術:從目前基于焊接(solder)的鍵合集成技術逐漸改進到die-to-wafer以及die-to-die的鍵合。新的集成鍵合技術將是實現高密度IO的核心技術。

從高級封裝技術的演進路線圖,我們可以看到摩爾定律的指數規律正在高級封裝領域繼續發生。在未來十年中,高級封裝的IO密度將預計會提升16倍,IO互聯密度提升25倍,這大約是每2.2-2.5年翻倍的規律,這和之前摩爾定律預計每1.5年芯片晶體管密度翻倍的規律相近,只是翻倍時間從1.5年變成了2.5年。

模擬和混合信號:無線通信和功率電子的核心

模擬和混合信號電路在未來十年的半導體路線圖中也扮演了重要角色,因為模擬和混合信號電路仍將是重要應用的賦能技術。

模擬和混合信號電路的第一個核心應用是無線通信。預計在未來10年,無線通信對于數據率的需求仍將持續上升,而為了支持更高的數據率,需要在更高的載波頻率使用更高的帶寬,同時需要電路的性能(線性度、噪聲系數等)持續演進。

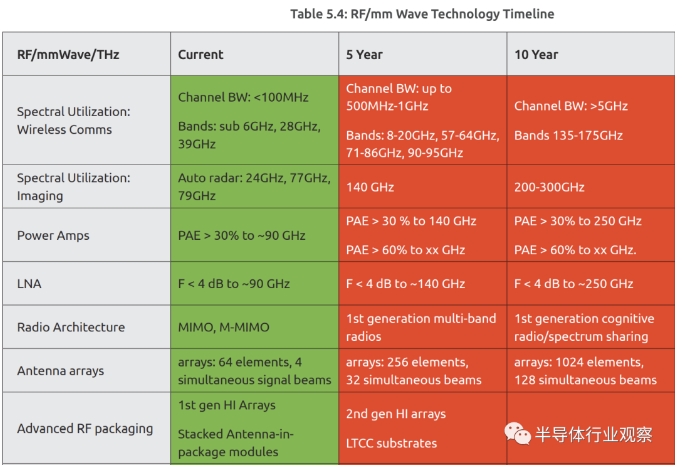

具體到無線通信模擬混合信號電路路線圖中,我們可以看到一些核心的指標演進:

載波頻率從今天的低于40GHz演進到175GHz,同時帶寬從今天的100MHz上升到5GHz

低噪聲放大器系數保持在4 dB附近,但是工作頻率從最高支持90GHz上升到250 GHz

功率放大器的效率保持30%,但是支持的頻率從90GHz上升到250GHz

天線陣列的復雜度大大提升,從目前的64單元提升到1024單元

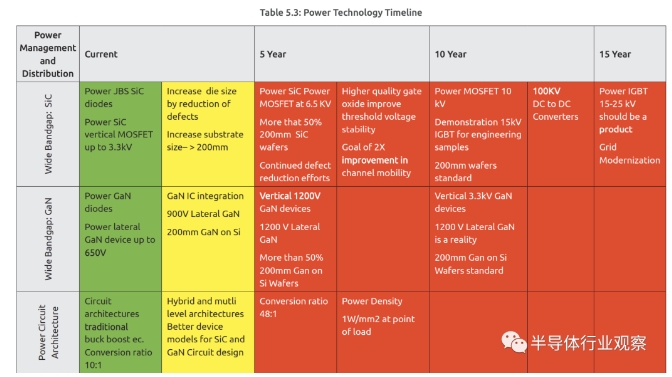

除了無線通信之外,另一個模擬和混合信號的賦能領域是功率電子。未來十年,功率電子應用預計越來越多:人工智能的進一步普及需要更多數據中心,而數據中心需要高效率供電模塊以確保總體能效比;新能源汽車更進一步得到使用,需要更高效率的功率芯片;太陽能等新能源變得越來越主流,也需要功率電子的配合。

在路線圖中,我們可以看到GaN和SiC功率電子芯片都會得到長足的發展。對于SiC來說,預計未來10-15年,支持的電壓將從今天的3.3kV拓展到15-25kV,從而為新能源應用提供支持,同時也進一步增加器件載流子移動速率以提升器件的性能(支持更高的開關頻率);而GaN也在提供高器件性能和開關頻率的同時增加對于高電壓的支持,從今天的650V提升到3.3kV,而除此之外另一個重要的演進方向是進一步提升GaN對于硅基底(GaN on Silicon)的支持,在10年后預計200mm GaN-on-silicon晶圓將成為標準配置,從而進一步降低GaN的成本并且有機會支持更方便的高級封裝集成。