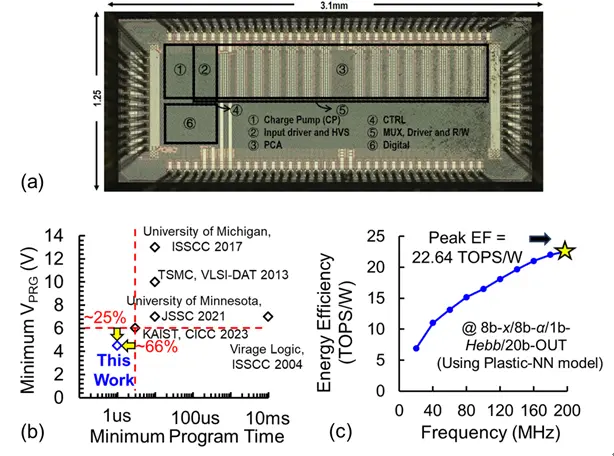

中國科學院微電子研究所發文稱,該所劉明院士團隊設計了一款基于非易失 / 易失存儲融合型的片上學習存算一體宏芯片,并且在 14nm FinFET 工藝上驗證了具有多值存儲能力的 5 晶體管型邏輯閃存單元,編程電壓(-25%)與編程時間(-66%)較同類型器件均獲得有效降低,相關研究成果已在 ISSCC 2024 國際會議上發表。

在此基礎上,該團隊進一步提出了邏輯閃存單元與 SRAM 融合的新型陣列,不僅可以利用非易失與易失性存儲單元的特點滿足片上學習過程中長期與短期信息的存儲,還能通過對矩陣-向量乘與矩陣元素乘的高效處理加速片上學習過程中所需的關鍵算子。

此外,團隊還提出了一種與存儲陣列深度融合的低硬件開銷差分型模數轉換電路,采用采樣電容復用的方法節省面積,通過多元素稀疏感知的方案節省功耗。

據介紹,該芯片可以有效支持具有突觸可塑性的神經網絡,基于前饋過程動態更新短期信息,從而實現動態的片上學習。

該存算一體宏芯片基于 14nm FinFET 工藝流片,可實現小樣本學習等片上學習任務,官方標稱 8bit 矩陣-矩陣-向量計算能效達 22.64TOP / W。

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。