7 月 16 日消息,《韓國經濟新聞》(hankyung) 昨日報道稱,三星電子已決定在下代 HBM 內存 —— HBM4 中采用自家 4nm 工藝打造邏輯芯片。

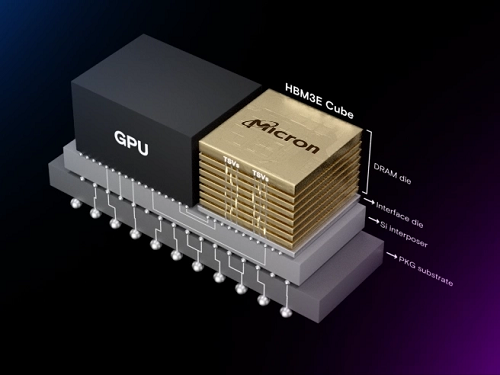

注:此處邏輯芯片指 Logic Die,SK 海力士稱基礎裸片 Base Die,美光稱接口芯片 Interface Die。結構參見美光下圖:

層層堆疊的 DRAM Die 內存芯片為 HBM 內存提供容量;而 Logic Die 則是 DRAM 堆棧的控制單元,還負責通過互連層與處理器上的內存接口通信,也是 HBM 內存的重要組成部分。

傳統上,存儲廠商通常自行采用存儲半導體工藝生產 HBM 內存的 Logic Die,流程更為簡便。但來到 HBM4 世代后,Logic Die 需要支持更多的信號引腳、更大的數據帶寬,甚至還要承載部分客戶定制功能。

因此存儲廠商轉而選擇與邏輯晶圓廠合作,用邏輯半導體工藝生產 HBM4 用 Logic Die。

此前就有消息傳出,臺積電將采用 7nm 工藝為 SK 海力士代工 HBM4 的基礎裸片。

▲ 三星電子目前最先進的 HBM3E 12H 內存

三星電子存儲部門此番采用自家 4nm 工藝打造邏輯芯片,一方面可提高 HBM4 內存綜合能效,提升產品競爭力;另一方面,更為精細的 4nm 工藝也為各種定制功能的導入留出了更多空間。

不僅如此,此舉也可為兄弟單位 LSI 部門提供一份規模不小的訂單。

對于三星電子存儲部門來說,在產品中導入 LSI 部門的先進工藝并非沒有先例:其面向 OEM 端的消費級固態硬盤 PM9C1a 也配備了 LSI 部門代工的 5nm 主控。

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。