4 月 24 日消息,臺積電 2025 年北美技術論壇不僅公布了最先進的 A14 邏輯制程,在先進封裝領域也有多項重要信息公布。

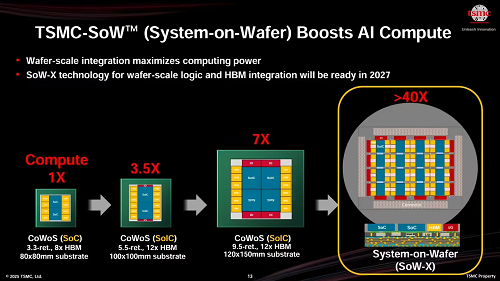

臺積電表示該企業計劃在 2027 年量產 9.5 倍光罩尺寸的 CoWoS,從而能夠以臺積電先進邏輯技術將 12 個或更多的 HBM 堆疊整合到一個封裝中,這意味著單封裝可容納的芯片面積將相較此前進一步提升。

而在更大的晶圓尺寸封裝系統方面,臺積電則帶來了 SoW 系統級晶圓技術的新版本 SoW-X。該技術采用不同于 SoW-P 的 Chip-Last 流程(IT之家注:先在晶圓上構建中介層再添加芯片),計劃于 2027 年量產。

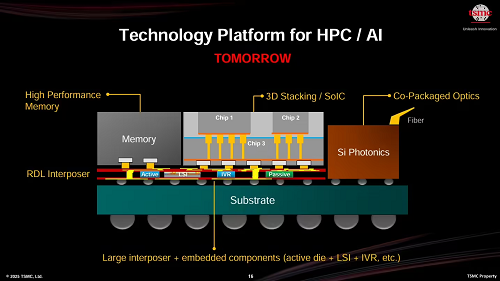

臺積還介紹了其它一系列高性能集成解決方案,包括用于 HBM4 的 N12 和 N3 制程邏輯基礎裸晶(Base Die)、運用 COUPE 緊湊型通用光子引擎技術的 SiPh 硅光子整合。

▲ 未來的 HPC / AI 芯片需要復雜的整合集成

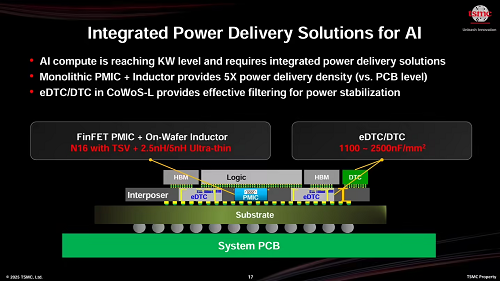

此外臺積電也公布了用于 AI 的新型集成型電壓調節器 / 穩壓器 IVR。與電路板上的獨立電源管理芯片 PMIC 相比,IVR 具備 5 倍的垂直功率密度傳輸。

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。