微電子技術的持續發展使得FPGA具有更高的系統集成度和工作頻率。系統性能較大程度上決定于系統的時鐘延遲和偏斜。由于FPGA具有豐富的可編程邏輯資源及時鐘網絡,隨之而來的時鐘延遲問題使得用戶設計的性能大打折扣。FPGA中的DLL模塊可提供零傳播延時,消除時鐘偏斜,從而進一步提高了FPGA的性能和設計的靈活性。

PLL是常用的時鐘管理電路,主要是基于模擬電路設計實現的,而DLL主要是基于數字電路設計實現的。雖然在時鐘綜合能力上比PLL差,但由于具有設計仿真周期短,抗干擾性強,以及工藝可移植等特點,DLL非常適合在數字系統架構中使用,這也是FPGA采用DLL作為時鐘管理的原因。文中將介紹傳統FPGA片內延時鎖相環設計,并在此基礎上提出具有更快鎖定速度的新延時鎖相環架構OSDLL。

1 FPGA片內DLL結構及工作原理

1.1 DLL架構設計

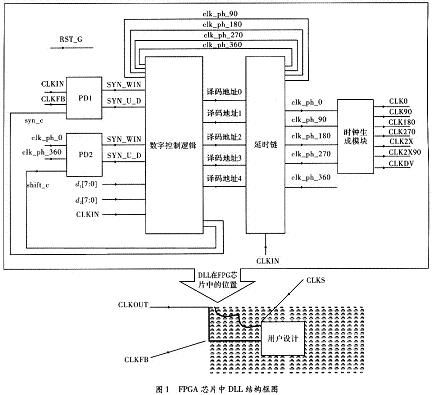

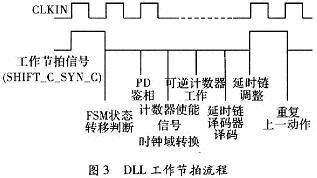

圖1為FPGA片內DLL結構框圖。圖1中FPGA片內用戶設計的時序邏輯部分在布局布線后,位于芯片中部,相應的時鐘走線較長。為緩解時鐘緩沖、重負載時鐘線的大電容、線路的傳播延時等因素造成的時鐘偏斜,可以選擇使用DLL模塊進行時鐘優化管理。

圖1中,DLL主要由鑒相器(PD)、可調延時鏈、數字控制邏輯以及時鐘生成模塊組成。CLKOUT為DLL輸出時鐘,即時鐘生成模塊的輸出時鐘;CLKS為經過時鐘線后到達時序電路的偏斜時鐘;CLKFB即為CIKS,反饋時鐘CLKFB反饋回DLL。DLL的功能為通過在時域中調節CLKOUT的相位使得CLKFB與CLKIN同步,即消除時鐘偏斜。

1.2 DLL工作原理

DLL的工作過程依賴于控制邏輯的設計。DLL的控制邏輯主要包括SHIFT控制邏輯和SYN控制邏輯兩部分,如圖2所示。DLL的工作過程首先進行SHIFT階段,之后進行SYN階段。

從圖2可見,可調延時鏈共5條,即一條主可調延時鏈(延時鏈0,256個延時單元),4條子可調延時鏈(延時鏈1~4,各128個延時單元)。如圖2所示,4條子延時鏈,SHIFT邏輯和一個鑒相器(PD2)構成相移器。SHIFT階段,相移器工作。相移器采集第一級子延時鏈的輸入時鐘clk_ph_0和最后一級延時鏈的輸出時鐘clk_ph_360,根據鑒相結果同步調整4條子可調延時鏈的延時,直至clk_ph_O和clk_ph_360同步。經過相移器的時鐘延時是一個周期,從而使得時鐘經過相移器中的每個子延時鏈的輸出時鐘相移90°,對應圖2中分別為clk_ph_O,clk_ph_90,clk_ph_180,clk_ph_270,clk_ph_360。這些相移的時鐘可以根據實際的需要由時鐘生成模塊產生所需要分頻(CLKDV),倍頻(CIK2X)或移相時鐘作為輸出時鐘,關于分頻和倍頻電路,如文獻。SYN邏輯用于控制將反饋時鐘和輸入時鐘調整至同步。

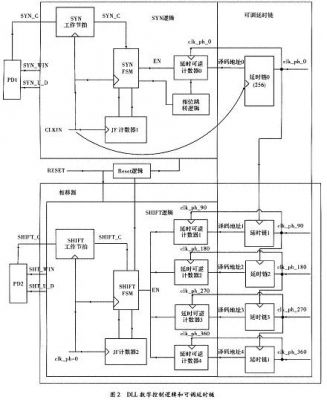

整個SHIFT階段和SYN階段都是在各自的控制邏輯模塊控制下工作的,以一定的工作節拍實施調整,如圖3所示。

圖2中工作節拍模塊生成工作節拍信號(SHIFT_C,SYN_C)。在工作節拍下,狀態機處于某一狀態,則根據狀態的調整要求依次進行如下操作:鑒相,判斷出輸入時鐘和反饋時鐘的相位關系為超前或滯后(SHT_U_D)或SYN_U_D),同時還可以指示兩時鐘是否進入鎖定窗(SHT_WIN,SYN_WIN),如圖l所示。鑒相器將這些信息送入控制邏輯模塊,在SHIFT階段,4條延時鏈對應各自的可逆計數器,負責控制延時鏈加減延時單元,各計數器工作在自己的時鐘域中,如圖2所示。根據鑒相的結果和所處的狀態機狀態,計數器進行計數,計數結果作為延時鏈的譯碼地址,最后延時鏈經過地址譯碼增加/減少一個延時單元,完成一次工作節拍調節,繼而繼續進行下一次調整,直到狀態機進入鎖定狀態為止。SYN階段工作方式類似,但只對主延時鏈進行調整。實現DLL鎖定,同步建立需滿足公式,如式(1)所示。

DSYN+SKEW=mult(P) (1)

式中,DSYN為主延時鏈可以提供的延時;SKEW為時鐘偏斜;muh(P)為整數個輸入時鐘周期。

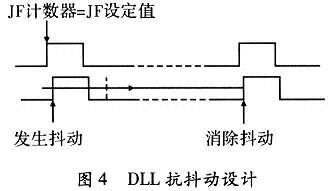

1.3 抗抖動設計

如圖2所示,控制邏輯中JF counter1和JF counter2功能模塊。用戶可以設置抗抖動數值d1,d2,如圖1所示,從而對這兩個模塊中的計數器設定一個計數周期。在DLL鎖定之后這兩個模塊開始工作,按照計數設定值的周期性對鎖定后的時鐘進行檢測。即在計數器達到設定值時,對鎖定后的反饋時鐘和輸入時鐘進行鑒相,判斷相位關系,控制可逆計數器對鎖定后的時鐘進行周期性微調干預。如圖4所示,在系統內存在干擾時,會產生時鐘抖動,若抗抖動模塊工作檢測到反饋時鐘超前于輸入時鐘,則進行一次微調,消除抖動的影響。抗抖動設計有助于減少抖動的影響。同時由于計數周期可設,使得用戶可以在不同系統工作環境下,采用不同的抗抖動設定值,以達到最優的防抖效果。