前言

伴隨著工藝技術水平的提高,當前ASIC設計規模和設計復雜度也不斷的提高。合理的選擇驗證工具在ASIC設計過程中起了關鍵作用。下面就結合實際的項目開發,對比驗證工具的特點,幫助大家更好的認識驗證工具。

SystemC 介紹

SystemC是一個開發硬件的面向對象的新型建模方法,建立在C++基礎上,是為了方便系統級設計和IP交換。System C是一個開放的標準,由13家EDA和電子行業的公司共同控制。

包括

ARM Ltd.;Cadence Design Systems, Inc.;CoWare;Fujitsu;Mentor Graphics;Motorola;NECSynopsys

System C的源碼可以從http://www.systemc.org/網站上免費下載。SystemC是由一些C++的類庫

組成。用System C開發的硬件模型可以用標準的C++編譯器來編譯:

Unix/Solaris: bcc,gcc

Windows: MSVC

經編譯后形成一個可執行的應用程序,設計人員可以通過console來觀察系統的行為,驗證系統功能和結構.

Specman E介紹

Specman Elite是Cadence公司的驗證技術工具,它能提供可配置、可再使用和可擴展的驗證組件。能夠產生足夠多的測試激勵訊號,并能對設計行為與預期結果進行檢查確認。

1. EOS 系統的驗證

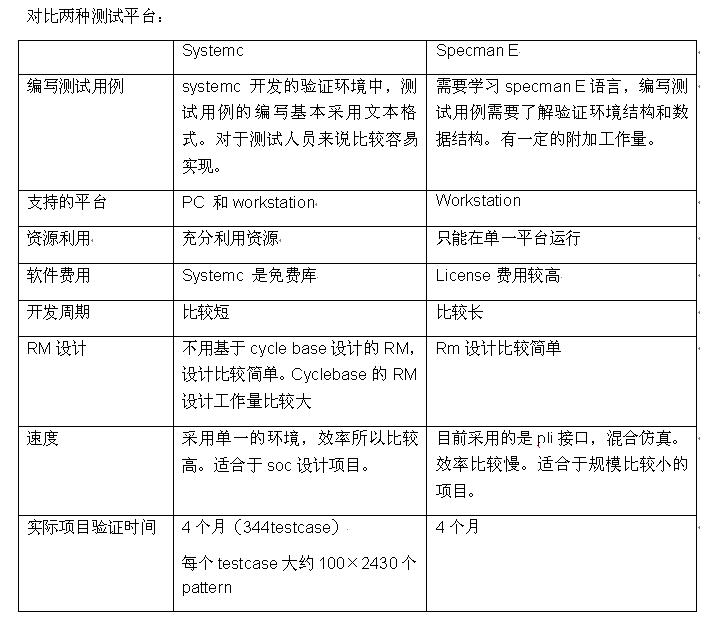

測試EOS 系統采用SystemC,比較以往的以verilog,specman E,vera語言要有以下特點, 不用付高額的eda tool 費用;可以充分的利用個人電腦系統資源;實際的開發周期大大縮短。

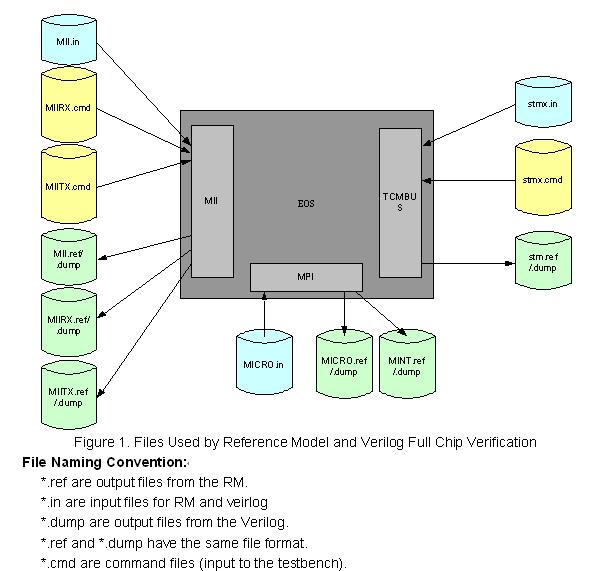

下面是EOS驗證系統的設計框圖。

mii: Mii Interface

MPI: Microprocessor Interface

TCM: TCMBUS Interface

RM設計和測試用例設計基于pc的c++環境開發,所有的測試用例產生的輸入輸出結果存為文件。Verilog代碼根據輸入文件產生激勵,根據端口的輸出產生輸出文件(*.dump)。結果的檢查是通過比較所有的RM輸出的文件(*.REF)和verilog輸出的文件(*.DUMP)。

RM設計思路,基于數據流設計,大大減少了具體硬件實現上的細節,提高了RM設計效率。

這個基于RM(reference model)設計的方法,在項目前期驗證設計系統結構設計是否合理;后面驗證可以繼承項目前期系統結構設計階段的成果。同時基于硬件資源環境4 workstations 和13 PC。由于PC資源充足,把測試用例的設計和RM測試在PC上進行設計。由于verilog的開發在workstation環境下,并且資源緊張,是項目開發進度的瓶頸,所以選擇verilog速度最優的驗證途經。

基于specmanE實現測試SDH系統軟件

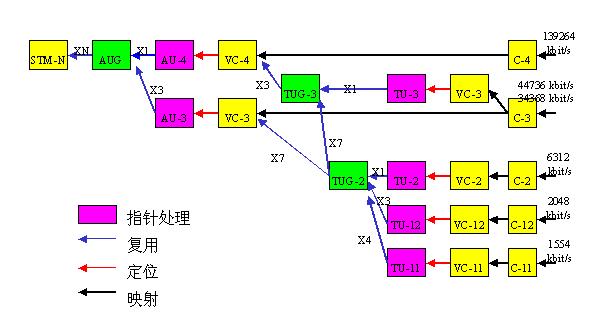

CPXXX支持的SDH業務基本復用結構如下:

根據數據結構特點和E語言特點,創建了STM4、STM1、AUG1、AU4、AU3、VC4、TUG3、TUG2、TU3、TU2、TU12、TU11、VC3、VC2、VC12、VC11、C4、C3、C2、C12和C11基本數據結構。實際的測試數據是通過擴展基本數據結構的方法配置SDH數據生成幀。可以配置數據結構包括STM4、STM1、AUG1、AU4、AU3、VC4、TUG3、TUG2、TU3、TU2、TU12、TU11、VC3、VC2、VC12、VC11、C4、C3、C2、C12、C11。配置方法的實質是對各種數據結構生成的初始化函數進行個性化擴展。

這種基于E語言的驗證設計環境,可以和verilog聯合仿真。但是仿真速度比較慢,單一的verilog仿真速度的1/4~1/3,在驗證工作量比較大的項目中,這是個瓶頸。所以在實際的驗證中,我們的策略是盡可能的把復雜的模塊進行詳細的模塊級驗證。因為每個模塊功能特性不一樣,這樣就需要維護的驗證環境比較多。

結論

1. 對于驗證工具的選擇,要結合資源(包括機器,人力和費用)和實際項目的特點,選擇合理的有效的驗證工具搭建驗證環境。

2. 對于驗證設計工具,不要有排斥或者崇拜的情緒,要結合實際的應用,搭建能發揮各自特點的環境是一個項目管理的要求。

參考:

1.《Writing Testbench:Functional Verification of HDL models》,Janick Bergeron, Qualis design corporation.

2.《E Reference》 Verisity Design, Inc.

作者簡介: 陳思軍,project manager , Chiphomer Technology Limited.