1 RS編碼原理

RS編碼是一種線性的塊編碼,其表示形式為RS(N,K)。當編碼器接收到一個數據信息序列,該數據信息序列被分割成若干長度為K的信息塊,并通過運算將每個數據信息塊編碼成長度為N的編碼數據塊。在RS碼中的碼元符號不是二進制而是多進制符號,其中2m進制使用更為廣泛。能糾正t個錯的RS碼具有,如表1參數所示。上述參數,t表明最多可以糾正t個隨機錯誤符號。

由于RS碼是對多進制符號糾錯,RS碼可用于糾正突發錯誤,比如能糾兩個八進制符號錯誤的RS(7,3)碼,每個符號可用3 bit二進制符號表示。八進制的RS(7,3)碼相當于二進制的(21,9)碼,因此糾兩個符號就相當于糾連續6 bit二進制符號的突發錯誤,然而二進制的(2l,9)碼卻沒有糾6 bit突發錯誤的能力,它能糾任何2個隨機錯誤以及長度≤4的突發錯誤。

通用的RS編碼的運算步驟:

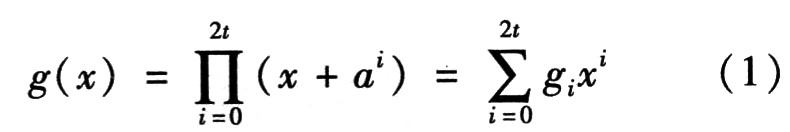

(1)確定RS編碼器的生成多項式g(x),這里選用了最為常用的生成多項式,如式(1)所示。

式中a定義為m階初等多項式p(x)的根它可生成全部GF域的元素。(有關GF域的內容可參閱相關書籍)。

以RS(15,9)為例,RS(15,9)的生成多項式,如式(2)

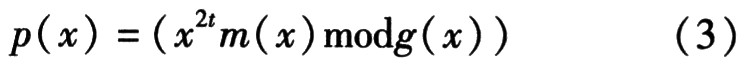

(2)通過對取模運算產生校驗信息多項式p(x)如式(3)

式中m(x)表示RS編碼碼字中的數據信息,它是K一1階的線性多項式。

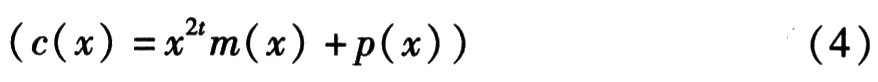

(3)通過加法運算生成最終的編碼后的多項式c(x)如式(4)

RS碼的編碼主要是圍繞碼的生成多項式g(x)進行的,一旦生成多項式確定了,則碼就完全確定了。

2 RS編碼的設計實現

在一些特定應用域中,RS碼的設計與實現是比較困難的。RS碼是在有限域上進行的代數運算,不同于常用的二進制系統,實現相對復雜一些,其復雜度主要決定于有限域的大小、碼字的長度、采用的編碼算法等,編碼器的實現方式主要有以下幾種:

(1)微處理器實現的RS編碼。

通用的微處理器采用查表(Table—lookup)方法可以實現RS編碼,首先需要產生有限域運算中的系數,存于內存中,就可以通過查表的方法實現編碼了。

(2)利用DSP實現的RS編碼。

DSP早已成為傳統微處理器的一種替代品,現在的DSP芯片已能對一些特定的應用提供并行的處理結構,可以在DSP芯片中完成RS編碼,不過DSP不是專為實現糾錯中需要的特定功能設計的,同樣也可以采用查表的方法在DSP中實現快速有限域運算。

(3)ASIC實現的RS編碼。

ASIC是專用集成電路,由LSI—Logic Corpera—tion設計的ASIC芯片,有3 kB的RAM和4 kB的ROM,是實現高速編碼器的最佳選擇。

(4)FPGA實現的RS編碼。

FPGA能夠快速和經濟地將電路描述轉化為硬件實現,而且對設計的修訂也比較方便。而通常的ASIC需要的設計時間較長,制作費用也較高,也不便于調整。所以本設計是基于FPGA的RS編碼設計。

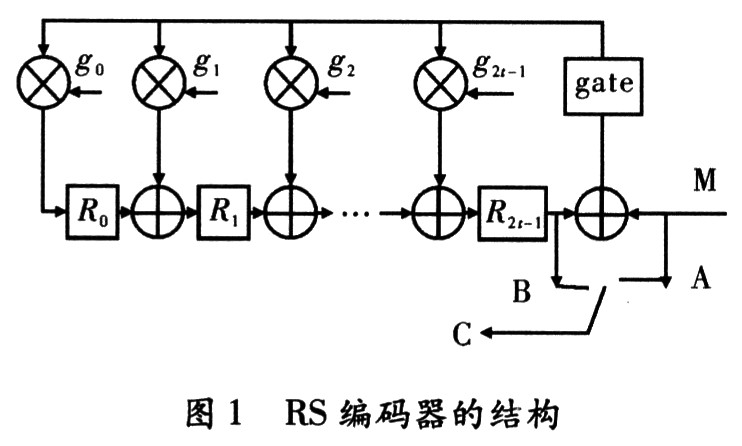

如圖1所示為本設計所采用的編碼器的結構。

其工作原理如下:

(1)寄存器R0~R2t-1全部清零。開關接通A點,然后信息位分為兩路送電路中,一路直接送入C(x),一路送入除法電路并進行移位。每一個時鐘移一個字節;

(2)在k個時鐘結束的時候,信息位全部輸入,完成除法功能。此時移位寄存器里保留了余式r(x)的系數,這就是RS碼的校驗位;

(3)在k+1個時鐘到來的時候,開關接通B點。寄存器中的數據依次移出,送入信道。在經過2t個時鐘后數據全部移出,得到2t個校驗位。這2t個校驗位跟在原先的尼個信息位的后面,組成(n,k)碼輸出。這樣就完成了RS碼的編碼;

(4)寄存器R0~R2t-1全部清零,重復步驟(1)、(2)、(3),完成對下一組RS碼的編碼。

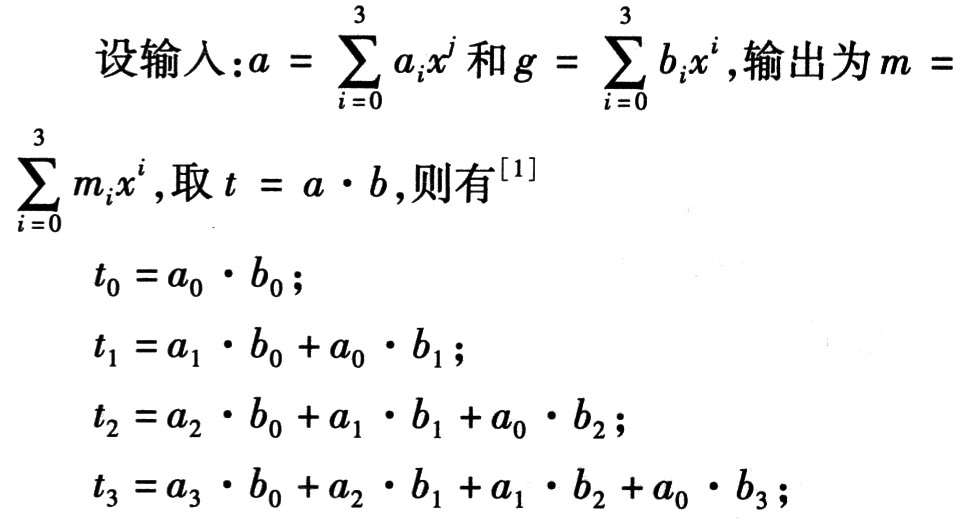

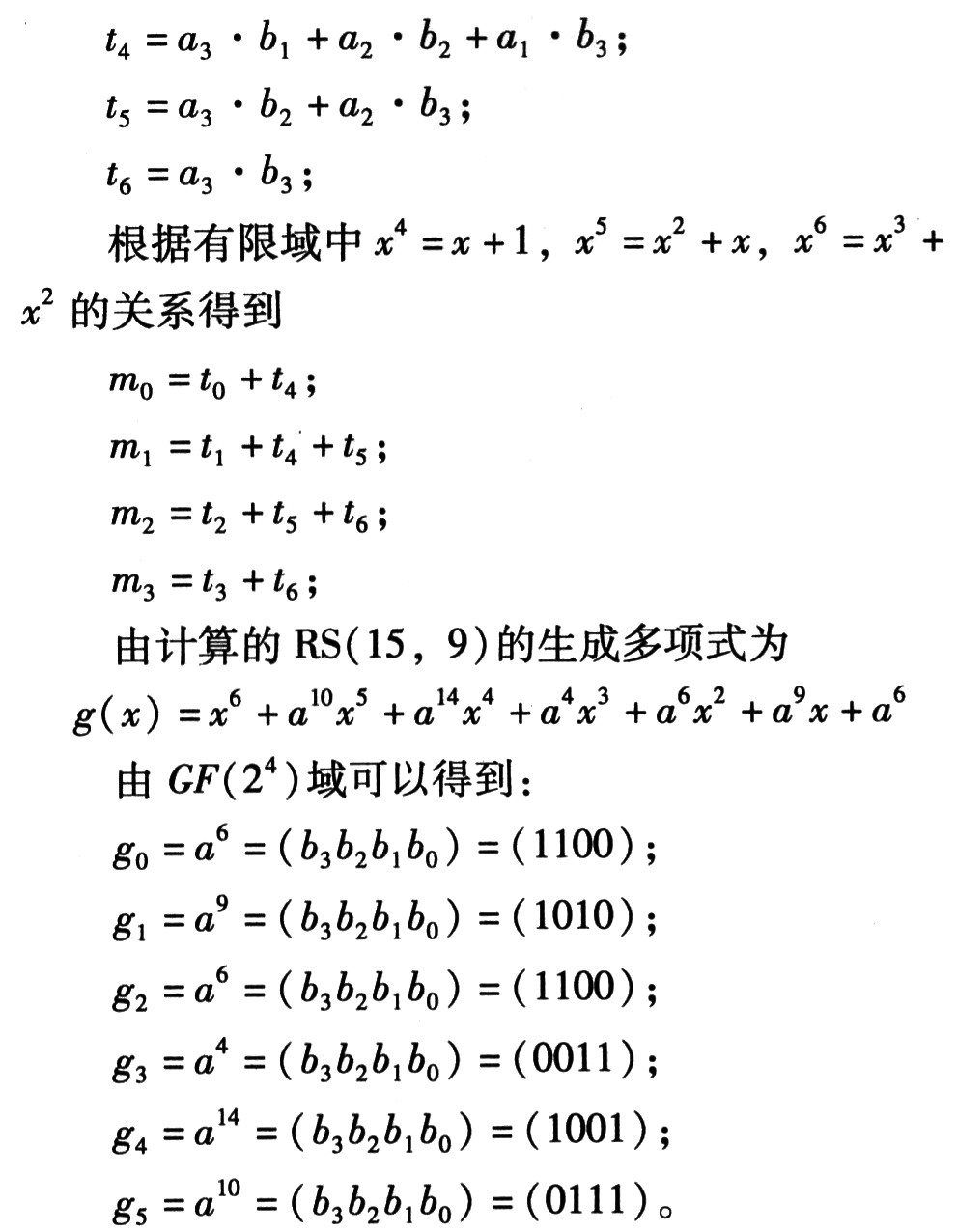

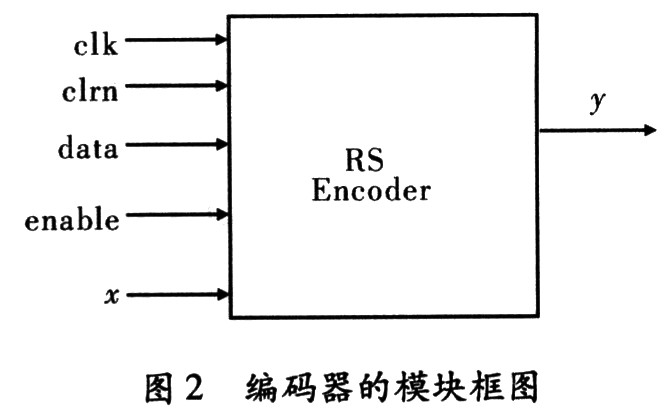

下面以RS(15,9)為例描述有限域的乘法實現思路如下:

根據上面的式子可以寫出RS(15,9)的6個乘法器。如:與g0相乘的結果

其余乘法器的描述方法與此類似。完成對乘法域的語言描述,剩下的工作就是對加法器的描述了,由于加法實現比較簡單,這里就不做介紹了。接下來就是控制輸出信息位還是校驗位的開關都是比較好設計的。

4 RS編碼器的仿真

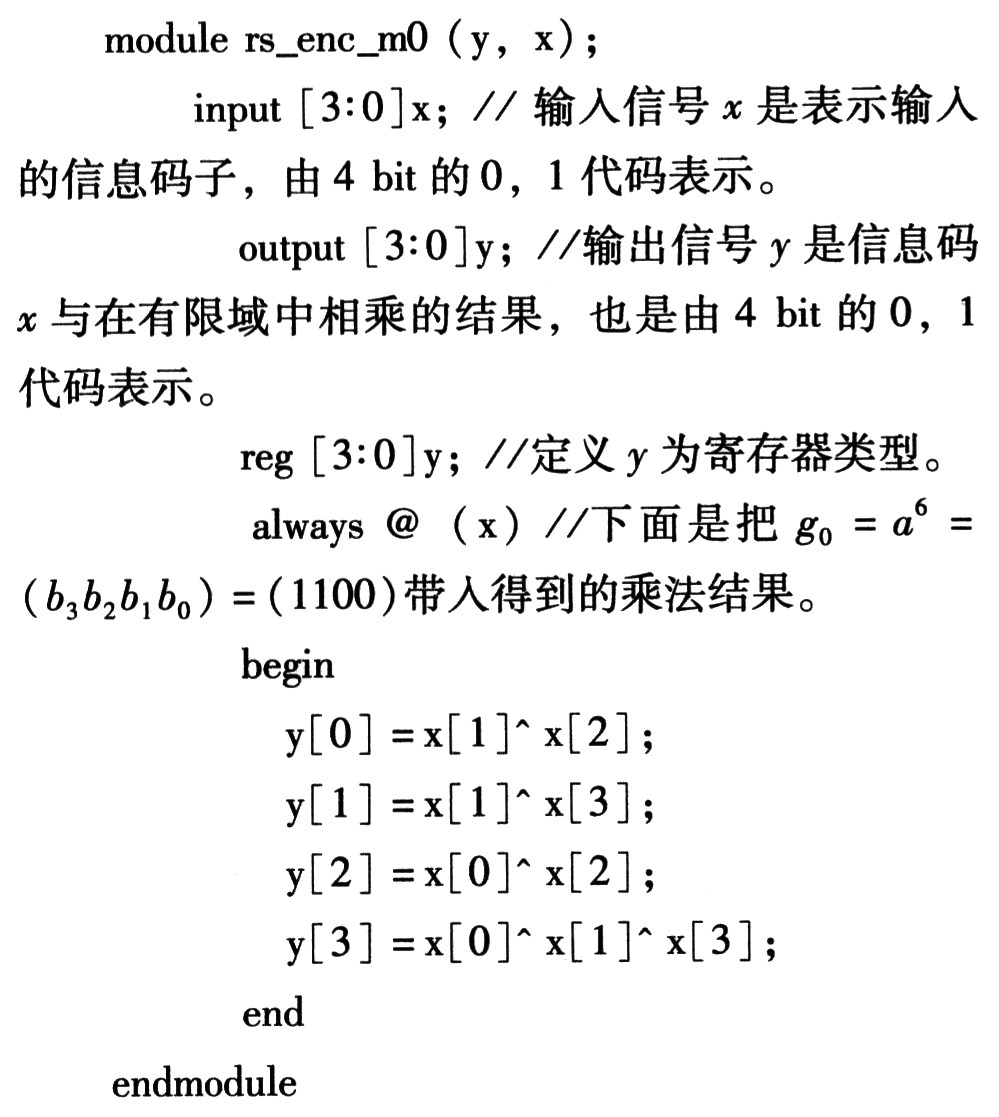

本設計是實現了RS(15,9)的編碼,本設計編碼器的模塊框圖,如圖2所示。

各信號說明如下:

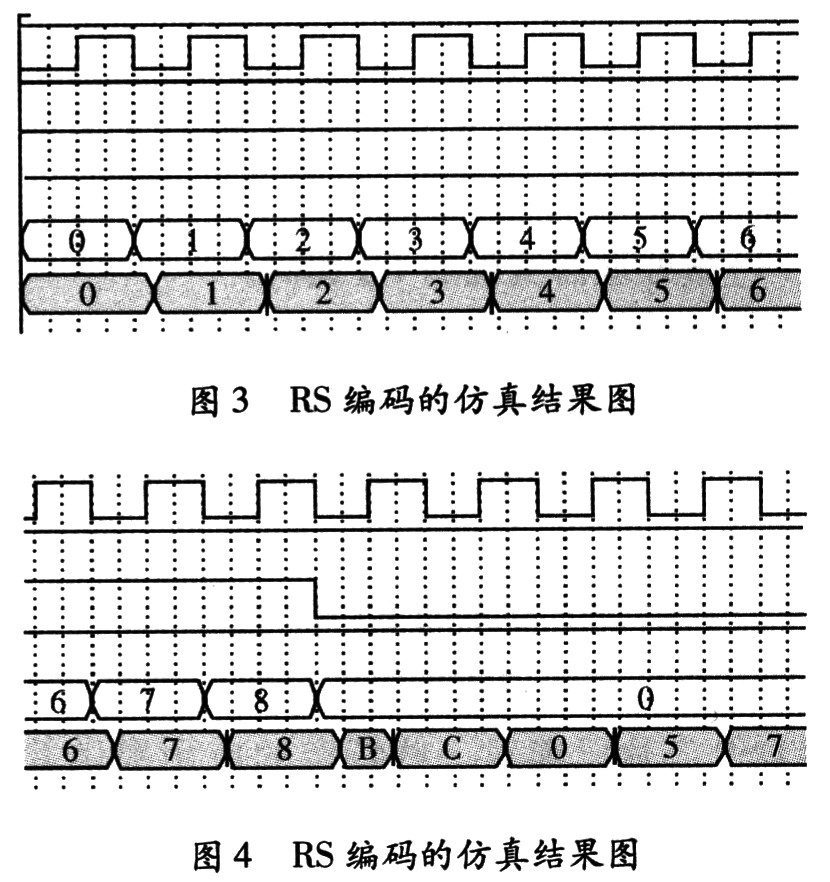

本設計信號時鐘clk周期是40 ns,clrn是復位號,data表示信息輸入有效,enable表示啟動編碼器,開始編碼,x是4 bit信息符號,y是編碼生成的4 bit碼字。由下圖編碼圖形可知,一次編碼周期需要590.0 ns,最大編碼速率為l700 MHz。因此,一次編碼需要15個時鐘周期。在25 MHz的時鐘下,RS編碼器仿真時序圖,如圖3和圖4所示,并由仿真圖可看出,本算法的編碼速度高時延間隔不到半個周期。

RS編碼測試數據如下:

輸入信息:0,1,2,3,4,5,6,7,8;

編碼器輸出:0,1,2,3,4,5,6,7,8,B,C,0,5,7。

5 結束語

RS編碼的所有運算都是建立在有限域的基礎上的,其中乘法器的設計是其編碼技術的關鍵。本設計實現了RS(15,9)的編碼設計和仿真,仿真輸出結果與理論分析一致,基于相同的原理,可以實現任意數據塊長度的RS編碼器設計。