摘要:系統利用直接數字頻率合成技術(DDS)完成任意波形發生器設計,以FPGA作為核心控制器件,用FLASH和RAM作為波形數據存儲模塊,在上位機軟件的控制下,利用高精度D/A轉換器,實現正弦波、方波、三角波、鋸齒波、高斯白噪聲等任意波形輸出。系統可廣泛用于通訊、遙控遙測、震動激勵和儀器儀表等領域。

隨著數字信號處理技術的飛速發展,高精度大動態范圍D/A轉換器的出現和廣泛應用,基于取樣技術和計算技術,通過數字方法生成頻率和相位相對固定且可調的合成技術,即直接數字頻率合成(DDS)技術日益成熟,它采用全數字化結構,具有頻率分辨率高、相對帶寬寬、頻率轉換速度快、相位噪聲低、信號純度高等優點。因此,本系統采用DDS技術來完成任意波形發生器設計。

1 DDS工作原理

直接數字頻率合成(DDS)技術是一種以采樣定理為基礎的全數字化波形產生方法。DDS頻率合成器主要由相位累加器、波形數據存儲器、D/A轉換器和低通濾波器組成,其原理框圖如圖1所示。在一個系統時鐘周期內,相位累加器將前一次的累加值與頻率控制字相加,得到新的累加值,將新的累加值作為地址,從波形數據存儲器中讀取信號的幅度值,送入D/A轉換器將數字信號轉換為模擬信號,最后再經低通濾波器生成需要波形。其中波形數據存儲器中存儲了周期信號單個周期的幅度值,相位累加器每溢出1次,可從波形數據存儲器中讀取1個周期的信號幅度值。因此,若假設頻率控制字為K,相位累加器為N位,則經過 個系統時鐘周期,可產生1個周期的輸出信號,再設系統時鐘頻率為fsclk,則輸出信號頻率

個系統時鐘周期,可產生1個周期的輸出信號,再設系統時鐘頻率為fsclk,則輸出信號頻率 。

。

2 系統總體框圖

系統總體框圖如圖2所示。其中,上位機軟件由LabWindows軟件編寫,用于控制信號的產生,下位機以FPGA作為核心控制器件,主要用于接收上位機發送的控制命令和信號參數,并控制下位機系統產生對應波形。下位機系統主要分為FPGA控制單元、波形存儲單元、波形產生單元。波形存儲單元主要包括FLASH和SRAM,FLASH用于存儲各種波形數據,波形產生時,FPGA先將要產生的波形數據從FLASH讀入SRAM,再利用相位累加器的累加值從SRAM中讀取波形數據。波形產生單元主要完成波形數據的產生,首先將SRAM讀出的波形幅度數據送入D/A轉換器,產生信號的階梯序列波,再通過低通濾波器和功率放大電路產生輸出信號。

3 系統硬件設計

3.1 FLASH連接電路圖

FLASH采用美國飛索半導體公司的S29AL032D,其容量為32 MB,它用于存儲各種波形的幅度信息,其存儲形式如圖4所示。

由圖4可知,地址區間0x000000~0x01FFFF存儲正弦波幅度值,地址區間0x020000~0x03FFFF存儲三角波數據,地址區間0x040000~0x05FFFF存儲鋸齒波數據,地址區間0x060000~0x07FFFF存儲白噪聲數據,地址區間0x080000~0x0FFFFF為4個用戶自定義區,存儲4種用戶需產生的周期波形數據。

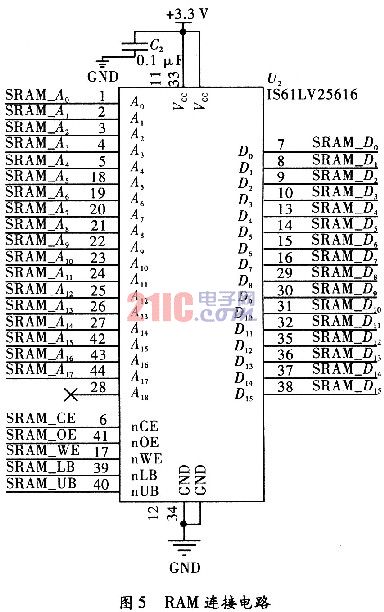

3.2 RAM連接電路圖

RAM采用美國芯成半導體公司的IS61LV25616AL-10T,其容量為256×103×16 bit,主要用于存儲上位機發送的控制命令及波形產生時信號的幅度值,其存儲形式如圖6所示。

地址區間Ox00000~0x1FFFF存儲上位機發送給下位機的控制命令和數據參數,地址區間Ox20000~Ox2FFFF存儲系統要產生信號的波形幅度值。

3.3 信號產生電路連接圖

圖7為任意信號產生的電路連接圖,產生信號頻率范圍為50 Hz~200 kHz。其中,AD768為16位高精度D/A轉換器,其最大更新速率可達40Msps,滿足設計要求。

4 系統軟件設計

4.1 上位機軟件設計

上位機部分由Labwindows軟件編寫,主要負責對下位機系統的控制,包括對信號頻率、幅度、相位(占空比)的設置,信號波形的選擇,用戶自定義波形數據的輸入等,其控制面板如圖8所示。

4.2 FPGA軟件設計

FPGA為系統的核心控制單元,負責與上位機軟件通信及控制下位機系統產生任意波形。

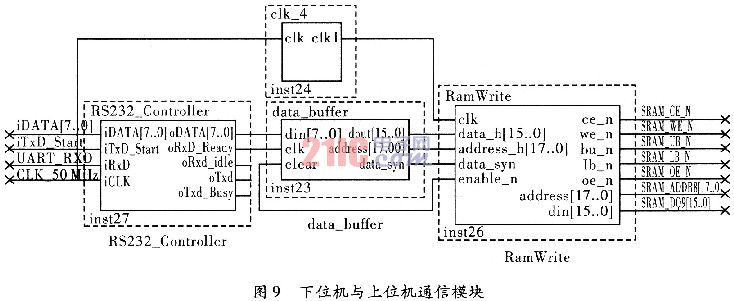

4.2.1 與上位機通信模塊設計

上位機與下位機的通信是通過RS232來實現的,FPGA主要用于接收RS232發送過來的數據并將其存入外部RAM中,通信模塊如圖9所示。

RS232_Controller模塊用于接收上位機發送過來的數據,RS232的速率為115.200 kB/s,8位數據位,1位停止位,無校驗位。data_bu-ffer將RS232_Controller接收的數據緩存,并按接收先后順序組合成16位數據后送入RamWrite。RamWrite再將這些16位數據從地址0x00000開始存入外部RAM中。

4.2.2 接收數據處理模塊

本模塊主要用于分析和處理接收到的上位機數據,從中提取出信號的數據信息、各項參數及控制命令,如圖10所示。

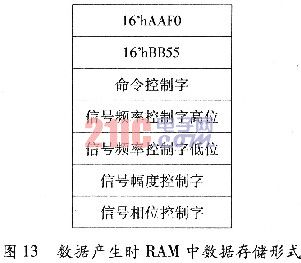

當RS232發送數據完成時,接收數據處理模塊立即從地址0x00000開始讀取RAM中的數據。當第1個數據和第2個數據分別為16'hAAF0和16' hBB55時,則第3個數據的高8位為命令控制字,否則接收數據處理模塊停止讀取RAM中的數據。8位命令控制字各位所代表含義如下

用A代表命令控制字,A[n]代表命令控制字的第n位數據,則:

當A[15]為1時表示存儲用戶自定義波形數據,為0時表示任意波形的產生。當為波形存儲時,A[14:8]為0表示將波形數據存入用戶自定義1區,為1表示存入2區,為3表示存入3區,為4表示存入4區。從讀取的第4個數據開始即為用戶自定義波形數據,共65 536個,再以16'h65 80和16'h0856作為結尾,其存儲形式如圖12所示。

當為任意波形產生時,A[14:11]為0表示產生正弦波;為2表示產生方波;為3表示產生三角波;為4表示產生鋸齒波;為5表示產生高斯白噪聲;為6表示產生用戶自定義1區波形;為7表示產生用戶自定義2區波形;為8表示產生用戶自定義3區波形;為9表示產生用戶自定義4區波形。從RAM中讀取的4個16位數據分別代表要產生波形的頻率(32位)、幅度、相位(方波時為占空比)控制字。其數據存儲形式如圖13所示。

4.3 FLASH數據存取模塊設計

此模塊用于波形數據的存儲和讀取。在信號產生模式時,它根據Sig_Type[3:0]輸入的數據判斷需產生的波形,再從FLASH中讀取對應波形的數據信息并存入RAM中。當Sig_Type[3:0]為1時表示產生正弦波;為2時表示產生方波;為3時表示產生三角波;為4時表示產生鋸齒波;為5時表示產生高斯白噪聲;為6時表示產生用戶自定義l區波形;為7時表示產生用戶自定義2區波形;為8時表示產生用戶自定義3區波形;為9時表示產生用戶自定義4區波形。

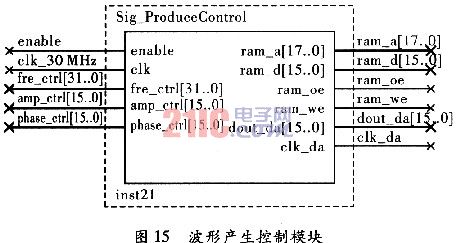

4.4 波形產生控制模塊

模塊利用DDS技術控制AD768產生任意波形信號,如圖15所示。

fre_ctrl,amp_ctrl,phase_ctrl分別為波形的頻率控制字、幅度控制字和相位控制字。clk為此模塊的控制時鐘,它的6分頻時鐘為32位相位累加器時鐘。在一個相位累加器時鐘周期內,模塊以累加器的高16位累加值、相位控制字及18'h20000之和作為RAM地址,從RAM中讀取波形信號的數據,設此數據為data,則D/A輸出的數據為,然后再在clk_da的上升沿將此數據送入AD768,依次循環,則AD768的輸出將產生階梯狀的信號波形,再經過低通濾波器和功率放大器即可得要產生的波形,圖16為系統產生的5V、200kHz正弦信號。

5 結束語

完成了任意波形發生器的設計,完成了系統硬件路的設計及軟件編程,經測試,系統可產生50Hz~200kHz頻帶內的正弦波、方波、鋸齒波、三角波、高斯白噪聲等常用信號,該信號發生器具有頻率分辨率高,頻率轉換速度快、信號純度高、產生信號種類多等優點。可廣泛應用于通信系統、自動控制系統、儀器儀表、電子對抗及遙控遙測等領域。