引言

現階段,主流的高性能光纖通道通用產品基本上被Qloglc、Morethan、DDC等少數幾家國外大公司壟斷,其昂貴的價格,加上一些發達國家對相關產品技術的封鎖,使得國內的光纖通道技術發展受到了一定程度的影響。因此,對自主知識產權的專用光纖通道芯片的研究就顯得尤為重要。

目前,大多嵌入式系統開發都采用ARM處理器或軟核處理器,而對于處理能力更強大的PowerPC處理器卻沒有更深入的研究和廣泛的應用,對于 Xilinx公司的嵌入式處理器PowerPC440" title="PowerPC440">PowerPC440的應用性研究也非常少見。本文基于PowerPC440硬核,對嵌入式技術在光纖通道網絡中的應用進行了一些探索。

1 設計方案

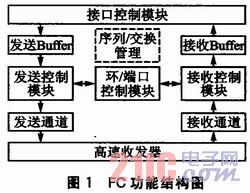

光纖通道協議(以下簡稱FC協議)支持多種拓撲結構,但由于交換機價格昂貴,在實際應用中還未普及。相對而言,簡單的點對點拓撲和性價比較高的仲裁環拓撲在現階段更為適用。本文即針對這兩種拓撲結構,在深入分析FC協議的基礎上采用模塊化的思想對功能作了劃分,

如圖1所示。其中由虛線框標識的序列/交換管理模塊由軟件實現。

接收數據:

①接收通道從光接收機接收其輸出的串行信號,經過串并轉換、8位/10位解碼、8:32解復用后,將沒有錯誤的字傳給接收控制模塊。

②接收控制模塊對接收通道接收的信息進行分流,將原語序列交給相應的狀態機,將數據放入接收緩存后通知序列/交換管理模塊。

③交換管理邏輯將根據幀頭內容和交換管理塊的內容進行進一步的高層次的差錯檢驗和交換/序列管理,并且等序列接收完成后通知上層取數據。

發送數據:

①當上層需要發送數據時,首先給光纖通道接口控制模塊發送命令。接口控制模塊根據命令的內容取出數據,并結合命令參數將數據打包成幀后通知發送控制模塊。

②發送控制模塊根據一定的規則控制不同的數據源分時使用發送通道,數據源包括發送緩沖區的幀、狀態機發出的原語序列和原語信號。

③發送通道將從

接收控制模塊接收到的字進行分解,再對并行的字節信息經過8位/10位編碼、并串轉換發送給光發射機。

其中環/端口控制模塊實現環初始化狀態機、環/端口狀態機、原有端口狀態機功能。根據原語信號和原語序列的不同,系統或進入原有端口狀態機進行點對點傳輸過程,或進入環端口狀態機進行仲裁環傳輸過程。

從總體上看,硬件應該負責幀級別的管理,軟件應該負責序列和交換級別的管理。軟硬件接口采用共享存儲器與寄存器的設計思想。系統硬件部分與軟件部分通過讀寫共享的幀緩存及接口寄存器實現信息交互。

2 基于PowerPC的SOPC系統搭建

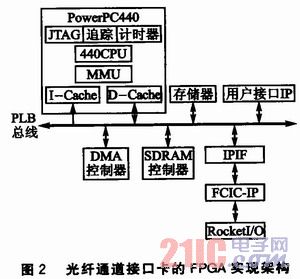

本設計采用Xilinx公司的Virtex-5 FXT系列開發板為開發平臺。此開發板集成了兩個嵌入式PowerPC440RISC核,同時具有靈活的存儲器管理單元(MMU),3個相互獨立的128位PLB總線接口,獨立的32 KB數據存儲器和32 KB的指令存儲器,4個直接存儲器存儲(DMA)控制單元,以及設備控制寄存器(DCR)等。其中PowerPCA40處理器具有高達500 MHz的速度,采用IP嵌入架構的形式整合到FPGA器件中,增強型BOOK-E體系結構,內部包括一個具有7級流水線的微內核,每周期最多可執行兩條命令,從而提高了整體的吞吐量。PLB總線采用36位地址路徑,可提供64 GB的內存尋址能力。

Xilinx公司提供的EDK開發工具是一種專門針對FPGA內部嵌入式處理器的集成開發工具包,主要的軟件設計由EDK中的子工具包SDK完成。用戶可以通過集成在EDK中的XPS來調用各種工具完成嵌入式系統平臺的搭建工作。

EDK10.1版本較之9.1版本有很大的變化,其中軟核版本升級到7.1,IBM CoreConneet總線標準中的OPB總線被PLB總線代替,還提供了豐富的外圍IP可供選擇。光纖通道接口卡" title="光纖通道接口卡">光纖通道接口卡的FPGA實現架構如圖2所示。

(1)PowerPC處理器和高速存儲器通過PLB高速總線互聯在一起構成嵌入式操作系統和軟件系統的運行平臺。

(2)用戶接口IP提供一個方便的接口,供外部設備操控接口卡芯片,亦可對該芯片的工作狀態進行動態監控。

(3)采用FPGA芯片內部集成的可編程高速串行收發器RoeketI/O來負責數據的發送和接收。

(4)在數據發送端,硬件通過DMA方式讀取與序列和交換管理有關的隊列,然后根據隊列中的信息,確定每個幀頭的內容,再通過DMA方式讀取管理內存中的數據并組裝成幀發送出去;在數據接收端,硬件接收到幀后,通過DMA方式寫到內存中,軟件負責將幀重組為序列,再將序列重組成交換。

3 IPIF模塊

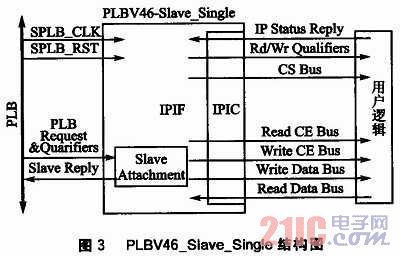

由于PLB總線接口協議非常復雜,為了讓用戶可以更便捷地實現總線與用戶IP的交互,Xilinx公司提供了在用戶IP核和PLB v4.6總線標準之間的一個雙向的PLBV46_Slave_Single接口協議模塊IPIF,如圖3所示。

其中的Slave Attachment結構提供了Slave運行的基礎功能,它在PLB總線和IPIC之間執行協議和時序的轉換。用戶IP的用戶邏輯接口需按照IPIC接口標準來設計,才能通過IPIF成功掛接到PLB總線上。

利用集成在EDK的XPS工具中Create/Import Peripheral Wizard(添加外設向導工具),以對話框的形式可以很便捷地配置IPIF模塊,以Master/Slave的方式將用戶自定制IP核掛接到PLB總線上,通過ISE1O.1環境綜合驗證模塊的正確性。然后再利用此工具,將經過驗證正確的IP核導入EDK環境下,這樣就成功建立了一個IP核的通用模板。最后再在相應的.VHD文件中添加用戶功能代碼,即可完成基于PLB總線接口的用戶自定制IP核的添加。

結語

本文設計的光纖通道接口卡芯片采用Xilinx公司推出的新一代嵌入式硬核PowerPCA40,利用EDK開發工具,在Virtex5系列FPGA開發平臺上實現了接口卡芯片的基本功能,支持點對點拓撲結構和仲裁環拓撲結構,為用戶自定制IP核的開發應用提供了一定的參考。