隨著EDA技術的發展,由于其在電子系統設計領域中的明顯優勢,FPGA已經在許多方面得到了廣泛應用,特別是在無線通信領域,FPGA以其極強的實時性,指令軟件編程的極大靈活性贏得了巨大的市場。本文采用FPGA來設計一款廣泛應用于計算機、Modem、數據終端以及許多其他數字設備之間的數據傳輸的專用異步并行通信接口芯片,實現了某一時鐘域(如66 MHz)的8位并行數據到另一低時鐘域(如40 MHz)16位并行數據的異步轉換,并且客戶可以根據自己的要求進行數據定義。完成數據在不同時鐘域間的正確傳遞的同時防止亞穩態的出現,保持系統的穩定,是電路設計的關鍵。

1 時鐘域轉換中亞穩態的產生

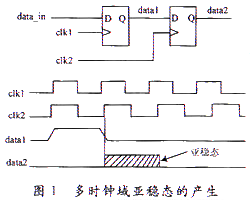

觸發器是數字電路設計中的一個重要元件,而觸發器工作過程中存在數據建立與保持時間的約束,如果這種約束得不到滿足,觸發器就會進入某個不確定狀態——亞穩態。亞穩態的存在可能導致連鎖反應,以致引起整個系統功能混亂。在單時鐘域電路設計中由于不存在時鐘之間的延遲和錯位,所以建立條件和保持條件的時間約束容易滿足。而在多時鐘域里由于各個模塊的非同步性,則必須考慮亞穩態的發生,如圖1所示。

2 多時鐘域數據傳遞方案

多時鐘域傳遞的信號有兩種,其一為控制信號,其二為數據流信號。針對這兩種不同的信號,分別采取不同方案遏制系統墮入亞穩態。對控制信號采用同步器裝置,即在2個不同的時鐘域之間插入同步器;而對于不同獨立時鐘域之間的數據流傳遞,為了避免異步時鐘域產生錯誤的采樣電平,采用FIFO存儲器作為其轉換接口,在輸入端口使用寫時鐘寫數據,在輸出端口使用讀時鐘讀數據,這樣就完成了異步時鐘域之間的數據交換。

芯片的總體邏輯框圖如圖2所示,圖中輸入輸出信號定義如表1所示。

從邏輯結構上將芯片劃分為3塊:寫時鐘域I/OBUFFER、讀時鐘域I/O BUFFER及FIFO存儲器。I/O BUFFER的主要作用是對外部信號進行預處理,消除外部信號的毛刺,保證信號可靠并使外部的信號與時鐘信號同步,消除不穩定的因素。根據信號的數目,BUFFER由相應數目的多個D觸發器構成。

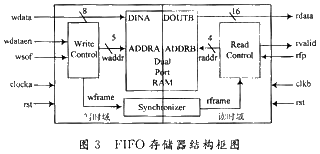

FIFO存儲器結構框圖如圖3所示,他由雙端口存儲器(Dual Port RAM)、寫控制單元(Writc Control)和讀控制單元(Read Control)構成。其中DUAL PORT RAM是由ISE6.0的一個編輯軟件CORE GENERATER自動生成,使用者只需設定RAM的端口數、內存大小和瀆寫控制便可以生成一個適合程序的子模塊。由于讀寫時鐘屬于不同的時鐘域,滿幀信號Frame從寫控制單元向讀控制單元傳遞時必須采取同步器(Synchronizer)同步。

2.1 寫控制單元設計

寫控制單元主要的功能是根據寫數據有效信號wdataen判斷輸入數據是否正確,在檢測到寫入數據幀的開始標志位wsof后開始計數控制寫指針waddr的移動,將正確的數據寫入DUAL PORT RAM中,并在一幀數據寫滿后向讀控制單元發出寫數據滿幀信號wframe。為防止亞穩態的出現,設計中采取了兩個措施:一是采用鎖存器將幀頭信號wsof拉長,確保其被穩定的采集;二是采用Gray編碼計數器替代普通二進制編碼計數器來控制寫指針waddr的移動,因為Gray碼相鄰兩個編碼之間有且只有1位發生變化從而抑制了競爭冒險的出現。

2.2 同步器設計

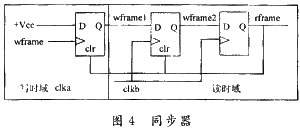

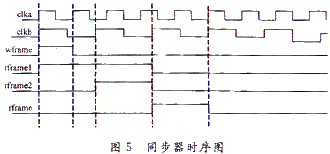

寫控制單元發出的寫數據滿幀信號wframe屬于控制信號,他從寫時域進入讀時域必須采用同步器實現信號同步,將寫時域的滿幀信號wframe變換為讀時域的滿幀信號rframe。由于信號是從高時鐘域(66 MHz)流向低時鐘域(40 MHz),因此采用如圖4所示的同步器。

同步器時序圖如圖5所示,可見在寫時域的滿幀信號wframe經過3個clka周期延后跨越到讀時鐘域。

2.3 讀控制單元設計

數據從寫時域傳遞到讀時域,時鐘發生了變化,而且讀控制單元的行為受到寫控制單元及Dual Port RAM中數據的存儲情況的雙重制約,因此他的設計是整個芯片設計成功的關鍵。

由于當Dual Port RAM中寫入一幀完整的正確數據后才能輸出,所以讀控制首先必須判斷Dual Port RAM一幀是否寫滿。榆測到滿幀信號rframe后,在等待輸出數據幀頭信號rfp到來后控制讀指針waddr移動讀出數據,并置位rvalid表征輸出數據的可靠性。

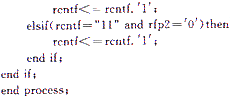

部分程序沒計如下:

3 多時鐘域數據傳遞的FPGA實現

設計方案完成后選用Xilinx Spartan-II FPGA實現電路,并在Xilinx ISE6.0集成環境下用Modelsim5.7進行了電路仿真。

圖6為寫使能信號dataen恒為有效值“1”的仿真結果截圖。

可見,在寫使能信號dataen恒為有效值“1”的情況下,在寫時鐘clka控制下當寫數據幀頭信號sof有效時,寫控制器開始寫入數據,接收到連續8個數據后,寫控制器發出一個幀滿信號wframe。wframe信號經過異步轉換后轉換成clkb時鐘域的信號。在讀控制器的控制下,當clkb時鐘處于上升沿,并且檢測到讀出數據幀頭fp時,開始從outdata向外發送數據,并將valid置為有效。

圖7為當寫使能信號dataen變化時的仿真結果截圖。

可見,將dataen置低后,系統不再接受寫入數據,所以也不再輸出數據,valid被置為低電平,輸出數據無效。寫控制的使能端控制達到要求。

4 結 語

針對異步并行通信接口芯片設計中涉及的多時鐘域的數據傳遞問題,本文采用FIFO存儲器來完成不同時鐘域之間數據流傳遞、同步器來完成控制信號傳遞的方案。仿真驗證結果表明,數據傳遞準確、穩定、可靠,沒有出現競爭冒險和亞穩態,完全達到了設計要求。