信號源廣泛應用于電子電路、自動控制和科學試驗等領域。它是一種為電子測量和計量工作提供符合嚴格技術要求的電信號設備。該設計可以模擬各種復雜信號,還可對頻率進行動態、及時的控制。作為激勵源,仿真各種測試信號,提供給被測電路,以滿足測量或各種實際需要,并能夠與其它模塊,組成自動測試系統。該系統的設計,完整的實現了一個物理信號的產生,同時也包括信號發生器硬件的設計和軟件的設計。

1 系統構成

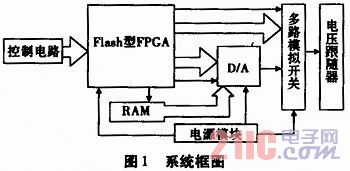

系統工作原理如圖1所示,通過JTAG接口把程序燒進芯片中后通過電源模塊給所有芯片供電使得它們可以正常工作。FPGA上電后自動復位,通過撥動撥碼開關選擇需要輸出的波形和波形的頻率,FPGA通過接收到的命令不斷的從RAM中讀出數據給D/A轉化器使其把數字信號轉化成模擬信號,同時FPGA也控制多路模擬開關在確定的四路中進行不斷的選通使得D/A轉換完的模擬信號在肉眼無法識別的情況下感覺是同時從四路輸出的信號,最后信號經過電壓跟隨器完整的輸出,我們用示波器在對應的插針上就能夠檢測到相應的信號。

2 硬件設計

FPGA采用的是ACTEL公司A3P125-VQ100,該芯片是一歙Flash型的芯片,有30k個系統門,多達81個用戶I/O口,350 MHz的系統性能。FPGA模塊是由晶振電路、復位電路和下載電路這幾部分組成。晶振為FPGA提供一個外接的CLK,復位電路是由一個電容和一個電阻組成,只要電源一給芯片上電就會自動復位,下載電路就是JTAG接口,通過該接口把下載的程序燒入到FPCA中。通過這幾個外接電路組成一個FPGA模塊。

控制電路模塊是由撥碼開關實現的,一部分用于信號選擇,另一部分用于頻率控制。該系統中一共有4種信號供選擇,撥碼開關只有0和1,所以只需用兩個開關就能控制選擇四種信號,在這里00表示直流,01表示正弦波,10表示三角波,11表示方波。那么撥碼開關的1到9位是用來控制頻率的,因為設計的要求是要控制1~500Hz頻率可調,而500用二進制表示為111110100共9位,所以頻率可調就是通過控制撥碼開關把需要的頻率用二進制表示出來,通過一定的運算法則使得輸出的波形頻率為所要的頻率。

D/A轉換器用的芯片是AD5424,該芯片為電流輸出型,8位的分辨率,17ns寫周期,DAC轉換時間是30ns。FPGA接收到控制模塊的命令后從RAM中給D/A不斷的發送8位的二進制數據,芯片通過自身內部一定的電路把前面發送的二進制數據轉換成相應的電流,發送數據的時間是通過該芯片的技術資料中的時序圖來控制的,每一個CS的寫周期是t3+t7=19ns,中間轉化是t7+t8=29ns。當再來一個有效信號時數據就被讀出,當寫信號有效時又開始寫入新的數據從而往復循環。

從AD5424輸出的電流通過下拉電阻轉換成電壓,經過第一個運放使電壓跟隨起到加強信號的作用,假設輸出的電壓是VLF353,通過第二個運放實現放大,第二個電路實際是一個負反饋的電路,通過公式![]() 可得把VLF353放大了兩倍,最后實現輸出,從而完成了從D/A到調理信號,再到輸出這一過程。

可得把VLF353放大了兩倍,最后實現輸出,從而完成了從D/A到調理信號,再到輸出這一過程。

轉化后的電壓需要4路同時輸出,一共有四種信號,所以采用ADG706這款芯片實現16路信號選擇。FPGA給ADG706發送命令控制什么時間選擇哪一路開關導通。每一個從模擬開關出來的電壓都需要通過濾波器模塊,這里用到的是OPA4340這款芯片,同時在每一個輸出后面加入一個電容以便保證電壓連續輸出。

在整個系統中每一個芯片都需要電源的供電,而每個芯片所需要的電壓也不一樣,根據需要電源模塊從外界引入一個5V的電壓通過TPS70358芯片轉換成3.3V和2.5V,通過SPX3819M5-L-1-5芯片把5V轉化成1.5V。

3 軟件設計

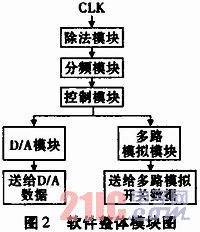

這個軟件的整體設計如圖2所示,主要分為五大模塊:除法模塊、分頻模塊、控制模塊、D/A模塊和多路模擬模塊這五部分。每一個模塊都有一定的功能,是一級一級實現的,軟件的整體功能是達到波形的多路輸出,頻率可調的功能。

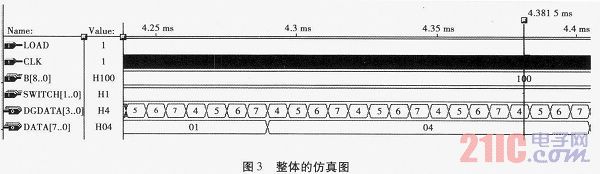

由于芯片的限制,在該芯片中寫入的程序時不能有除法運算,但是在這里為了選擇頻率必須用到除法,所以在寫入程序前先寫入一個除法程序模塊;由于要輸出的是多路信號,為了實現這一設計要求通過控制D/A和多路模擬開關兩個芯片的時鐘,使得他們在時鐘上不同步,D/A輸出的模擬信號在四個輸出口都可以輸出,由于肉眼識別的時間差異可以達到四路同時輸出這一效果。在圖3中LOAD是除法模塊中的使能端高電平有效,B[8..0]是控制頻率的,SWITCH[1..0]是選擇輸出波形的,這三個都是輸入端,輸出端是兩個,ADGDATA[3..0]和DATA[7..0],前面是多路模擬開關的輸出信號,后面是DA的輸出信號,從圖中可以看出DA輸出一個信號的時候多路模擬開關不斷的在四個開關口選通。

4 實驗結果

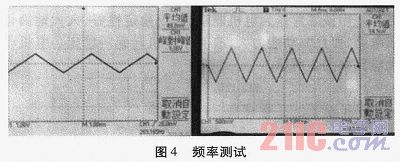

圖4是用撥碼開關輸出250 Hz和100 Hz的測試結果。從實驗結果中可以看出當撥碼開關的前9位為011111010,第10個和第11個撥碼開關為10,然后把示波器的紅色探針放到排母的第9根到第12根上的任意一根可以在示波器上看到三角波,并且在圖的右下角可以看到當前波形的頻率,該頻率為261Hz與理論上相差不大。當把撥碼開關的前9位改為001100100時,示波器的頻率顯示為100.94Hz,達到了預期的效果。

圖5為同一個方波信號同時輸出四路,當第10個和第11個撥碼開關為11時,會在排母的第13根到第16根上同時輸出方波信號,從圖片的左邊到右邊分別為探針從第16路到第13路探測出的波形,可以看到四路都有方波信號,實現了四路同時輸出信號的功能。

通過實驗結果可以看出該Flash型FPGA的信號源卡的設計實現了方波,三角波,正弦波和直流信號的多路輸出以及頻率在1~500 Hz可調的功能。