白玉1,楊斌斌1,楊承志2,王龍2

(1. 沈陽航空航天大學 電子信息學院,遼寧 沈陽 110136;2.空軍航空大學 信息對抗系,吉林 長春 130022)

摘要:針對電子戰中雷達對高抗干擾性和高分辨率的需求,設計了具有大帶寬、高頻率的寬帶雷達信號源。以FPGA為核心,采用面積換速度的思想,在FPGA中設計了多個信號生成單元,以這些單元產生多路參數相關的信號,通過多路并串轉換合成一路高頻信號,結合一片采樣率高達2.85 GS/s的高速D/A芯片進行數模轉換,完成了寬帶信號源的設計。通過MATLAB仿真,驗證了該方法的有效性,最后利用頻譜儀測試了信號源的性能指標,實測表明該信號源輸出頻率范圍介于DC~1 000 MHz,整體設計符合雷達應用需求。

關鍵詞: FPGA;面積換速度;AD9129;寬帶信號源

0引言

伴隨著電子戰的發展,不僅要求現代雷達要具有良好的目標識別與超近程的探測能力,還要求其具備極高的距離分辨力和很強的抗干擾性能,這就要求雷達的發射信號具備大帶寬。近年來由于匹配濾波技術和脈沖壓縮技術的發展,如脈內寬帶線性調頻信號(Wideband Linear Frequency Modulation Signal, WLFM)在雷達系統中得到了廣泛使用,它正好符合雷達距離分辨力和大探測范圍的需求。

用數字方法產生寬帶線性調頻信號,無論在頻率、幅度以及信號的信噪比等方面均優于模擬方法,且具有精度高、外圍電路簡單等優點。目前使用數字方式產生信號主要通過直接數字頻率合成(Direct Digital Frequency Synthesis, DDS)[1] 法來實現。DDS雖然受限于FPGA的時鐘頻率,但其具有很強的靈活性。近年來,由于FPGA的工作頻率隨著集成電路的發展不斷提高,越來越多的設計開始采用這種方法。例如參考文獻[2]、[3]采用DDS的思想分別介紹了使用可編程邏輯器件CPLD和FPGA控制DDS芯片來產生線性調頻信號。參考文獻[4]利用FPGA提供的知識產權核資源,在FPGA中直接調用多個DDS核來產生波形。

上述這些設計,普遍具有花費大、設計周期長、可移植性差等問題。本文在上述文獻的基礎上,提出基于FPGA的DDS優化設計,通過FPGA設計了多個信號生成單元。使用多個信號單元來產生多路特定參數相關的信號,再通過并串轉換技術合成為一路信號,最后借助于高速D/A芯片AD9129完成數模轉換,完成寬帶信號源的設計。

1系統原理介紹

1.1工作原理

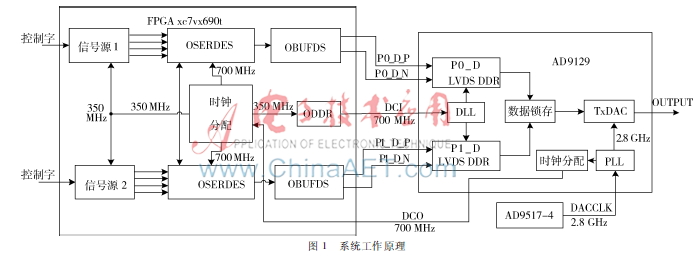

傳統DDS芯片受器件工作時鐘影響,導致DDS直接輸出的頻率上限較低,產生的信號帶寬很有限。本設計利用FPGA豐富的片上資源,在FPGA中設計了多個信號生成單元,在用其輸出多路調制樣式各異信號的同時,用它配置AD9129來產生寬帶雷達信號。AD9129實時采樣率為2.85 GS/s,可配置為雙端口傳輸數據,且每個端口可使用雙倍時鐘速率(Double Data Rate, DDR)來采集數據,這樣每個通道的數據采樣時鐘便降為D/A芯片工作時鐘的1/4,即700 MHz左右,但在700 MHz時鐘下,FPGA并不能嚴格保證其內部路邏輯的穩定,所以采用面積換速度的方法和流水線設計的思想,在FPGA中生成8個信號生成單元,這樣每個單元的工作頻率便降低到350 MHz,8個單元的信號通過并串轉換技術合成為兩路信號,D/A芯片通過兩個通道采集數據后,再將其合成為一路高頻信號。具體過程如圖1所示。

由圖1可見,在FPGA中生成了兩個信號源產生模塊,每個模塊含4個信號生成單元,這些單元均工作在350 MHz的頻率下,利用FPGA提供的并串轉換(OSERDES)資源進行并串轉換,可將8路信號合成為2路并行的信號,2路信號經過單端轉差分(OBUFDS)后轉化為2對頻率均為700 MHz的差分信號。AD9129在700 MHz的數據輸入時鐘DCI的驅動下,分別從P0_D和P1_D兩個端口使用DDR模式來采集FPGA傳送過來的兩對差分信號,采樣后的信號在外部時鐘提供的2.8 GHz時鐘ADCCLK的驅動下,最終將鎖存器中的數據轉換為一路模擬信號進行輸出。

1.2基于優化設計的信號生成單元

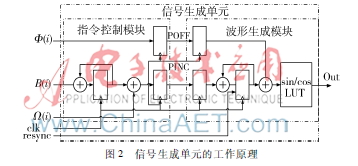

本文在FPGA中設計了多個信號生成單元,這些單元能夠在上位機的控制下,輸出特定參數的正弦波、鋸齒波等。與直接調用FPGA中的DDS核相比,本方案的信號生成單元占用更少的資源,擁有更高的執行效率。其工作原理如圖2所示。

圖2中,整個信號生成單元由指令控制模塊和波形生成模塊構成。假設需要輸出的WLFM信號脈寬為τ,帶寬為B,重復周期為T,起始頻率為f0,終止頻率為f1,調圖2信號生成單元的工作原理

頻斜率k為BT。本設計需要在FPGA中調用8個信號生成單元去拼一路信號,通過計算和MATLAB仿真及驗證,得到每路信號生成單元的調頻斜率ki都相等,均為8k,即為:

k1=k2=ki=8k i∈{0,1,2...7}(1)

設每路信號生成單元的初始頻率和初始相位分別為fi和φi,則fi和φi分別為:

fi=k×i+f0,i∈{0,1,2...7}(2)

![1`J(`)6XA4TQ[DV]WJJ8X5H.png 1`J(`)6XA4TQ[DV]WJJ8X5H.png](http://files.chinaaet.com/images/2016/08/31/6360827355264800005291610.png)

設計中,FPGA調用的8個信號生成單元的調頻斜率、初始頻率和初始相位分別根據式(1)~(3)進行配置。

2系統方案設計

2.1DAC芯片介紹

本文選用的D/A芯片AD9129是一塊高性能的具有14位DAC量化的數模轉換芯片,其具有雙端口接口和雙倍數據速率,以及低壓差分信號接口,可支持2.85 GS/s的最大轉換速率[5]。其結構如圖3所示。

AD9129芯片上的時鐘全部是差分時鐘信號,共有3對,分別為:D/A芯片的輸入時鐘DACCLK、數據輸入時鐘DCI、輸出時鐘DCO。根據配置信息的不同,AD9129可工作在不同的工作方式下,本文通過SPI串行接口向芯片內部寄存器寫入配置信息,將AD9129配置為雙端口傳輸數據,且每個端口均采用DDR模式。這樣AD9129的數據時鐘的頻率就降為芯片時鐘的1/4,降低時鐘的傳輸頻率就意味著可以提高時鐘的質量,也可以提高數據傳輸的正確率。

2.2軟件設計

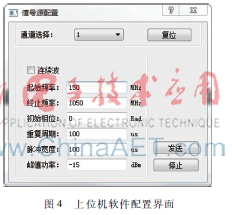

在本設計中,使用上位機軟件對FPGA進行參數配置,上位機軟件在Qt Creator 5.5環境中編程實現,其通過網口與FPGA進行通信,當啟動軟件后,軟件將自動接管系統控制權,在軟件上對相應的參數進行配置后,點擊發送按鍵圖4上位機軟件配置界面即可在DAC輸出端得到所需要的WLFM信號。其輸入界面如圖4所示。

3驗證與測試

3.1MATLAB仿真驗證

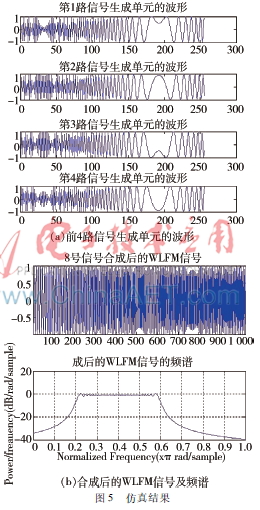

本設計提出了在FPGA中生成多個信號生成單元來產生WLFM信號。為了驗證方案的可行性,使用MATLAB對該方案進行了仿真驗證。通過計算及仿真,得到每個信號生成單元的配置參數,具體的仿真結果如圖5所示。

圖5(a)是仿真得到的前4路信號生成單元的輸出波形,圖5(b)是將8路信號合成后的WLFM信號的輸出波形及頻譜。經對比,合成后的信號與直接使用WLFM信號公式得到的數據完全相同。

3.2系統測試與分析

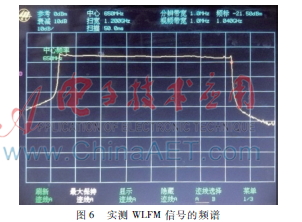

本文對設計后的系統進行了成果驗證,當設置起始頻率為150 MHz,終止頻率為1 050 MHz,初始相位為0 Rad,重復周期為100 μs,脈沖寬度為100 μs時,實測得到WLFM信號的頻譜如圖6所示。

在未濾波的情況下,從實驗截圖可看出,輸出信號的頻譜在1 GHz左右,帶內平坦度約為3 dB。實測觀察到信號源輸出頻率范圍介于DC~1 400 MHz。可見,本設計實現的寬帶信號源達到了設計指標要求,滿足實際工程需求。

4結束語

本文針對目前雷達發射信號帶寬較窄與頻率較低的問題,利用目前最具性價比的FPGA和高速D/A芯片,設計了帶寬與頻率分別可達1 GHz和1 400 MHz的寬帶信號源。使用上位機軟件配置FPGA的參數,利用FPGA產生信號,通過高速D/A進行數模轉換,完成了上述信號源的設計。仿真驗證表明,該設計對輸出信號的帶寬與頻率均有較大的提升,為提高雷達發射信號的性能提供了新的思路,該方案已成功應用于某戰場電磁環境產生器設計的實踐中。

參考文獻

[1] LEE P S, LEE C S, JU H L. Development of FPGAbased digital signal processing system for radiation spectroscopy[J].Radiation Measurements, 2013,48(1):1217.

[2] 彭昭,胡進峰. 基于FPGA的直接數字頻率合成器的優化設計[J].電子世界, 2012,16(18):108120.

[3] 柳春,甘泉. 基于FPGA的雷達信號源設計[J].電子技術應用,2013,39(11):4749.

[4] 唐大偉,吳瓊之. 基于高速D/A AD9739 2.5 GSPS的寬帶信號源[J].電子設計工程,2013,21(20):4547.

[5] ADI Corporation. AD9129 datasheet[EB/OL].(2013 03 21)[2016 02 25].http://www.analog.com.