2月,三星爆出將在美國德克薩斯州奧斯汀建設價值100億美元晶圓廠,發力追趕臺積電。雖然三星在5nm制程上已趕上了臺積電的腳步,于2020年實現了量產,但3nm似乎仍落后于臺積電。此前,臺積電已為其3nm制程晶圓廠投資200億美元,將于今年試產,預計2022年量產。為此,三星不惜跳過4nm制程節點,直接上3nm,不過2023年或難以量產。

在技術方面,三星稱在3nm時代就會采用GAA全環繞柵極FET,臺積電則要在2nm階段才開始使用。這似乎也預示著,三星將在3nm時代進一步拉近自己與臺積電的芯片代工技術差距。

隨著器件規模的不斷擴大,需要采用更精細的節點,但由于3nm制程的難度極大,出現了許多新技術、新問題和不確定性,需要在遷移中去適應和解決。

亞3nm挑戰頗多

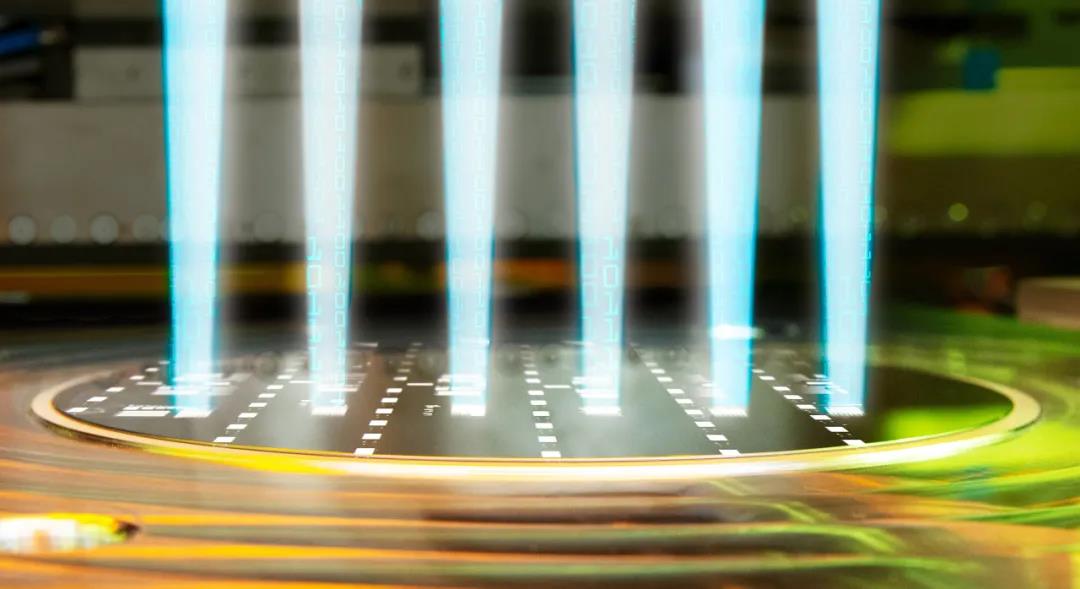

一些晶圓廠開始加大新的3nm的研發力度,2nm節點及其后的工作也在進行。從3nm開始,業界希望從今天的FinFET晶體管過渡到全環繞柵極(GAA)FET。在亞3nm節點,芯片制造商可能需要新的設備,比如下一代極紫外(EUV)光刻機,還有新的沉積、蝕刻和檢驗/計量技術。

根據IBS數據,7nm器件的設計成本為2.223億美元,5nm為4.363億美元,3nm為6.5億美元。在從FinFET轉向GAA-FET的同時,晶體管、晶圓廠設備、材料、光子學等方面都將迎來巨大的變化。事實上,并非所有設計都需要先進節點。不斷上升的成本也在促使許多人探索其他選擇,如先進封裝,力圖通過將先進芯片放入封裝中來擴展優勢。

FinFET向GAA-FET轉型的選擇

晶體管是器件中提供開關功能的關鍵組件。幾十年來,基于平面晶體管的芯片一直暢銷不衰。走到20nm時,平面晶體管開始出現疲態。為此,英特爾在2011年推出了22nm的FinFET,之后晶圓廠在16nm/14nm予以跟進。

FinFET中的電流控制是通過翅片三個邊上每個邊一個柵極實現的。當翅片寬度達到5nm時,FinFET幾乎走到了盡頭,3nm節點附近將停滯不前。因此,2022年前后,晶圓廠希望遷移到下一代納米片(nanosheet)FET,它屬于GAA-FET的范疇,是FinFET的延伸,其側面有柵極包圍。

三星的平面晶體管、FinFET與納米片FET

在GAA-FET中還有其他類型,例如,Imec開發的2nm叉片(forksheet)FET。這種晶體管的nFET和pFET集成在同一結構中,由電介質壁將nFET和pFET隔開。這與現有的GAA-FET不同,后者nFET和pFET是在不同結構中。叉片FET允許更緊密的n-to-p間距,減少了面增比(area scaling)。

互補場效應晶體管(CFET)是另一種類型的GAA-FET器件,也是2nm甚至以后的一種選擇。CFET由兩個獨立的納米線FET(p型和n型)組成。基本上,p型納米線堆疊在n型納米線的頂部。CFET是將nFET“折疊”在pFET器件上,以消除n-to-p分離的瓶頸,并因此將單元有源區域的面積減少了2倍。

CFET結構

專業人士認為,GAA技術,特別是堆疊CFET技術創造了一個向3nm、2nm和1nm邏輯擴展的拐點,很有前景。

不過,CFET前景看好,但發展需要時間。其挑戰包括:

在高溫工藝之前,需要使用很多金屬。因此,需要確定CFET觸點和互連之間所需阻擋金屬的最大熱極限。

厚度小于5nm的旋壓覆蓋(spin-coat)沉積層很容易受到表面能(surface energy)微小變化的影響,可能是襯底,也可能是材料。

光刻技術水漲船高

光刻是在芯片上繪制微小特征的藝術,有助于實現芯片功能的擴展。在亞3nm,芯片制造商可能需要一種新版本的EUV光刻技術,即高數值孔徑EUV(high-NA EUV)。它是當今EUV的延伸,仍在研發當中,預計2023年可在3nm制程中應用,這種體積龐大的設備既復雜又昂貴。

EUV的重要性顯而易見。多年來,芯片制造商在晶圓廠使用的都是基于光學193nm的光刻掃描儀。在多重圖案化(patterning)的幫助下,芯片制造商將光刻技術擴展到了10nm/7nm。但在5nm處,現有光刻技術已經失去了動力。這就是EUV的用武之地。它有助于芯片制造商在7nm及以后光刻出最難以實現的特性。

光刻設備能力

開發EUV的難度一直都非常大。隨著ASML使用13.5nm波長和0.33 NA透鏡的最新EUV掃描儀的推出,實現13nm分辨率已不成問題,每小時可生產170片晶圓。此前,在7nm處,芯片制造商使用基于EUV的單圖案化方法對微小特征進行圖案化。單圖案化EUV正在擴展到30nm到28nm間距。同時,芯片制造商還需要EUV雙圖案化,這是一個困難的過程。因為即使將多圖案化技術應用于EUV,對位控制(overlay)也是一個難題。

在5nm/亞3nm,雙圖案化EUV仍然是一種選擇,因為它具有一定的成本效益。但為了對沖風險,芯片制造商希望獲得高NA EUV,以便能夠繼續采用更簡單的單圖案化方法。不過,高NA-EUV掃描儀很復雜,系統采用具有8nm分辨率的0.55 NA變形鏡頭,而不是傳統的鏡頭設計。該鏡頭在掃描模式下支持8倍放大,在另一個方向支持4倍放大。這樣,照野大小減少了一半。所以在某些情況下,芯片制造商會在兩個不同的掩模上加工一個芯片。然后,將掩模合并在一起并印刷在晶圓上,這是一個復雜的過程。

Hi-NA EUV可以選擇半野或雙掩模

其他問題包括高NA EUV不能使用光刻膠。幸運的是,現有的EUV掩模工具可以用于亞3nm。晶圓廠可能需要新材料的EUV掩模底版,反過來又需要更快的掩模底版離子束沉積(IBD)工具。Veeco正積極與主要客戶合作,開發IBD系統的一些先進功能,以解決亞3nm的問題。

分析師認為,高NA EUV距離實現大批量生產能力還有幾年的時間。ASML可能會在2021年開始提供測試系統,但這并不意味著大批量生產的到來。

從原子層沉積到分子層蝕刻

現在,芯片是使用各種原子級處理設備生產的,例如原子層沉積(ALD)技術,一次沉積一層材料。原子層蝕刻(ALE)是一項相關技術,它是在原子級去除目標材料。ALD和ALE都用于邏輯和內存。

業界也在為亞3nm節點開發高級版本的ALD和ALE。區域選擇性沉積是一種先進的自對準圖案化技術。將新的化學方法與ALD或分子層沉積(MLD)工具相結合,選擇性沉積是在精確位置沉積材料和薄膜的過程。理論上,選擇性沉積可以用來在金屬上沉積金屬,在器件的電介質上沉積電介質。仍處于研發階段的技術可能會減少流程中光刻和蝕刻的步驟。

圖源 | digikey.com

另一項即將出現的技術是分子層蝕刻(MLE)。它從上世紀90年代開始研究,是基于等離子體的方法。MLE是有機/無機材料雜化蝕刻技術的延伸。對于半導體工業來說,它提供了一種對材料進行各向同性還原的方法,可以用作光刻掩模。

對于5nm以下節點的芯片來說,最大的問題之一是器件的選擇性增加,以及去除特定的材料。因此,芯片中出現的異常現象可以通過某種蝕刻來消除。在這些節點,晶圓上殘留的任何材料都可能導致額外的問題,比如掩模阻塞。

由于比有機材料更致密、更薄,過去幾乎所有的商業努力都集中在無機材料上。但隨著越來越多的有機材料進入制造過程,事情變得越來越復雜。在各向同性性質和掩模釋放的飽和值之間需要一個折衷,在這個過程中,即使材料密度較低,掩模釋放的厚度也可以較高。這方面,業界還在探索。

光學和電子束

計量學是測量結構的藝術,為的是使用各種系統發現芯片中的缺陷。檢查分為光學和電子束兩類。光學檢測設備速度很快,但有一定的分辨率限制。電子束檢測系統具有更好的分辨率,但速度較慢。因此,業界一直在開發多波束電子束檢測系統,以便以更高的速度發現最困難的缺陷。ASML開發的一種電子束檢查設備有九個電子束,有助于芯片制造商加速檢測過程。

目前,芯片制造商使用各種系統來測量結構,如CD-SEM、光學CD(OCD)等。前者采用自上而下的測量方法;后者使用偏振光來表征結構。十年前,許多人認為CD-SEM和OCD會失去動力。因此,行業加快了幾種新計量類型的研發,包括稱為臨界尺寸小角度X射線散射(CD-SAXS)的X射線計量技術。CD-SAXS使用來自小光束尺寸的可變角度透射散射進行測量,X射線的波長小于0.1nm。

CD-SAXS是一種非破壞性技術,也是一種非常簡單的度量方法。X射線源通過具有周期性納米結構的樣本發射聚焦的X射線束,X射線相機拍攝散射的X射線圖像。然后對一系列入射角重復測量。之后反解散射圖樣,得到周期結構的電子密度分布的平均形狀。散射計算是傅里葉變換,所以對大多數結構來說計算起來很容易。

CD-SAXS可以解決CD、無序CD以及層間電子密度的差異(這可能與成分有關)。與傳統OCD相比,CD-SAXS的主要優點是光學常數與尺寸無關,波長小,分辨率高,避免了OCD的許多參數相關性問題,計算簡單。CD-SAXS還可以測量埋入式結構物和光學不透明層。

不過,CD-SAXS都是由研發機構的大型同步加速器儲存環實現的。晶圓廠用的CD-SAXS的問題是X射線源有限且速度慢,這會影響吞吐量。雖然CD-SAXS可以穿透襯底,看到不同材料的層,但它是一種光學散射測量技術,速度很慢。另外,數倍的成本也是一個問題。不過,存儲器制造商已在使用這項技術來表征硬掩模和高深寬比結構。

轉向先進封裝

除了依靠成本不菲的先進制程節點,IC功能的擴展還可以通過改變芯片架構,在其中集成更多的片芯來實現。

畢竟能用得起尖端芯片的公司和應用還是少數。在供應鏈上,從規模的角度看,先進制程與現有制程的鴻溝不斷加大。最前沿的應用需要7nm、5nm,也許是3nm,但其他應用還在原地踏步。

為了提升性能,不妨“王顧左右而言他”,借助先進封裝,如小芯片(Chiplet)、3D封裝等異構集成形式來追趕摩爾定律。

小芯片3D堆疊

IC功能的一個重要方面是內部傳輸速度,因此,雖然面積至關重要,特別是人工智能(AI)應用,但芯片的速度取決于處理元件和加速器的高度冗余陣列,每個新節點的最大好處是利用架構變化和軟硬件協同設計。但是,信號通過細線從大芯片的一端傳輸到另一端所需的時間比使用高速接口垂直傳輸到另一個芯片所需的時間要長。

為此,臺積電將小芯片嵌入生產線前端(FEOL)封裝,使用先進混合鍵合技術改善了器件之間的連接,實現了所謂的系統集成芯片(SoIC),進一步提高了封裝器件的速度。這將比使用硅中介層(interposer)將芯片連接在一起更快,而硅中介層是目前這種方法的最先進技術。

硅中介層也可以用作光子學的波導,無論是封裝內還是封裝間,這又增加了另一種選擇。一個例子是,現在服務器場中的光纖是東西向的流量。通過新的背板,光纖不是通過模塊而是直接到服務器,最后到交換機所在的封裝。光子學的應用將帶來更多帶寬、更多大容量的解決方案。

光的優點是比通過銅線發送電信號所需的功率更小。因此,一些公司正在研發能夠傳輸光的中介層,如果成功,就可以用它連接芯片,讓光信號直接來到封裝的旁邊。當然,這樣做也不是沒有挑戰。光信號會隨著溫度的升高而漂移,因此需要對濾波器進行校準以解決漂移的問題。

寫在最后

該來的總會來

3nm即將發生,2nm也是如此。由于沒有一種技術可以滿足所有的應用,在芯片縮小和功能擴展的過程中,制程的進步、晶體管結構的變化和其他方法會交替進行,不斷推動芯片性能向上攀升,也不致被摩爾定律甩的太遠。