比利時imec在2021年11月舉辦了針對日本的技術介紹會議一一ITF(imec Technology Forum) Japan 2021,在會議上imec披露了當下的研發成果和未來的計劃。之前都是在東京的某家酒店舉行會議,今年受到疫情影響,在線舉行。

圖1:ITF Japan 2021的演講。出自筆者截圖。

(圖片出自:mynavi)

新結構、新材料、3D化為“摩爾定律”續命

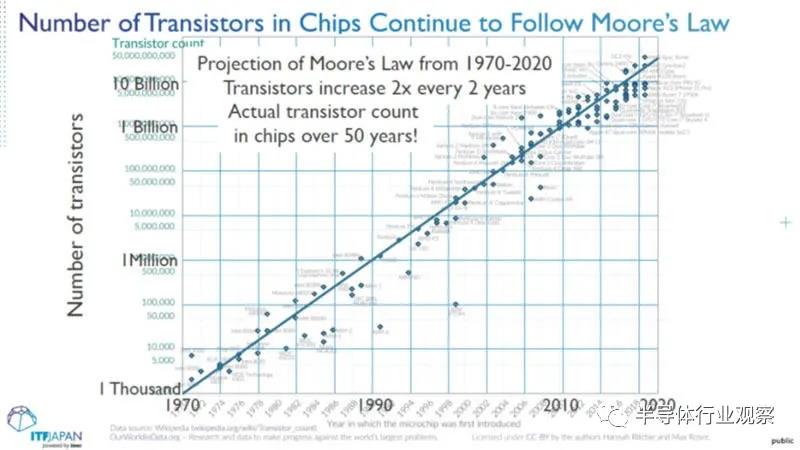

在上世紀末,就已經出現“摩爾定律”已經終結的悲觀論調。但是,imec為了不讓摩爾定律(是半導體產業增長的原動力)終結,一直在致力于提高工藝微縮化的集成度。而且,imec認為,在2020年之前的五十多年時間里,摩爾定律一直都在發揮作用。未來,通過導入微縮化、新型元件結構、新材料,以及堆疊芯片內晶體管和3D封裝(堆疊芯片),摩爾定律還會繼續發揮作用。

圖2:在過去五十年里,半導體芯片上晶體管數量的變遷。摩爾定律一直存在。(圖片出自:mynavi)

對1納米以下工藝的超微縮化技術的研究

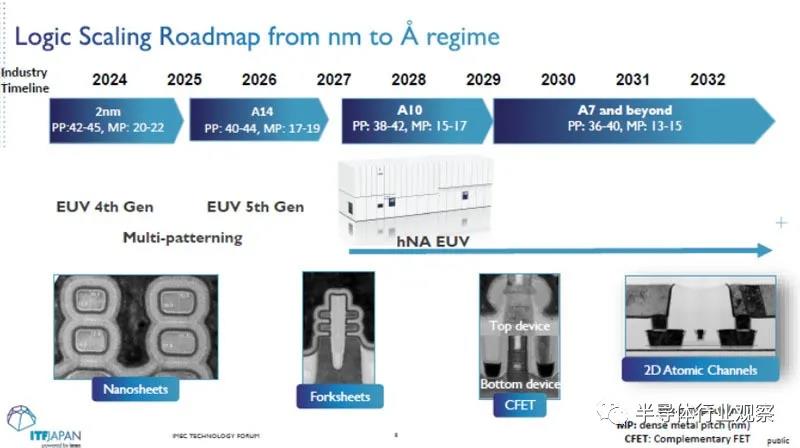

首先,作為2D的微縮化方向的努力,imec此次展示了未來十年的邏輯半導體工藝、電子元件的長期技術藍圖。

一直以來,微縮化的標準都是以納米為單位表示的,在2025年以后,即進入以“埃(?,angstrom,1埃 = 0.1納米 = 1^(-10)米)”來表示的時代。屆時邏輯半導體工藝、元件實用化的藍圖如下:2025年為“A14(14?=1.4納米)”、2027年為“A10(10?=1nm)”、2029年為“A7(7?=0.7納米)”。

這與英特爾在2021年7月披露的邏輯半導體工藝技術藍圖如出一轍,即2024年為“Intel2(2納米)”、2025年為“Intel 18A(18 ?)”(注:此處為英特爾公司內部叫法,可以看出英特爾試圖追趕在微縮化方面領先的TSMC)。Imec展示的邏輯半導體元件的技術藍圖上記載了“Industry Timeline”,還展示了先進半導體企業開始生產的年份。

另外,imec的長期方向在于研發先進工藝,而不是先進半導體企業從事的生產工藝。即,為了實現1納米以下的微縮化元件,imec已經在研發工藝、材料。將研發業務委托給imec的全球先進半導體企業與諸多設備材料廠家一起,外派了諸多技術人員、研發人員到比利時的imec園區,從事合作研發。

之前,人們使用最小加工尺寸、最小線寬、MOS晶體管的柵極(Gate)長等來表示邏輯工藝的微縮化,如今,各家公司不再將微縮化的程度拘泥于指標性數字,實際上集成電路上并沒有表示其長度的地方。因此,TSMC一直以來的“Nx(比方說,不說4納米,而是說N4)”、Intel最近提出的“Intel x(比方說,不說4納米,而是說Intel 4)”,這些名稱上都沒有提到長度單位。

從數字來看,每個代際(技術節點)都是上一代際的0.7倍左右(如,3納米、5納米、7納米、10納米……),這是英特爾自1970年制造出全球首個1K DRAM以來的傳統,長度為上一代際的0.7倍,面積就會成為上一代際的二分之一。如今,代際已經不再用長度來表示,因此面積也不一定就是上一代際的二分之一。

比方說,從下圖3中可以看出,PP為多晶硅(Polysilicon)排線線距(Pitch)的實際長度,MP為第一段金屬排線層的線距的實際長度。這樣,各家公司對于邏輯元件微縮化的指標就大相徑庭,且他們的指標遠遠小于線距。

圖3:imec的邏輯工藝·元件的微縮化技術藍圖。時間軸與先進半導體企業的生產元年一致,imec已經開始研發1納米(10?)以下的工藝。imec的目標是在三年內,將High NA EUV設備從試做到導入量產。(圖片出自:mynavi)

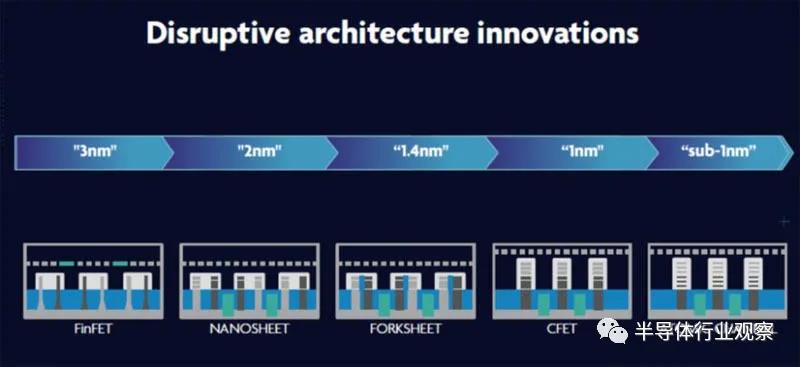

晶體管結構每個代際都在變化

就邏輯元件而言,隨著微縮化發展,其晶體管的結構從長年以來的平板型(Planner)結構到FinFET結構,在2納米以后,TSMC、英特爾正試圖采用GAA(Gate-All-Around,全環繞柵極)納米片(Namo-sheet)壓層結構。英特爾稱之為“RibbonFET”。此外,三星率先宣布已經從3納米過度到GAA納米層(三星稱之為“MBCFET(Multi Bridge Channel FET)”)。

就14?節點而言,imec提案了原用于CMOS的Forksheet結構(將p型和n型納米片晶體管成對排列,由于類似于用餐的叉子,所以命名為Forksheet),并一直在研發。就10?節點而言,imec試圖采用CEFT結構(Complementary FET,在硅表面垂直堆疊P-channel FET和N-channel FET),制作CMOS。在1納米(10?)以及以下節點,計劃采用原子形狀的溝道(Atomic Channel),其溝道采用厚度為1~多個原子層的2D材料。此外,imce所指的2D材料為半導體單層過渡金屬二硫屬化物(Dichalcogenide),化學式為MX2。此處的M為Mo(鉬)、W(鎢)等過渡金屬元素。X為硫、Se硒、Te(碲)等硫硒碲化合物(16類元素),imec通過采用2D材料和High NA EUV,開拓了1納米以下的工藝。

圖4:對晶體管結構變化的預測,imec正在研發以上所有的晶體管結構。(圖片出自:mynavi)

目標是在High NA EUV試做機出貨三年后實現量產

下面我們來看看EUV 光刻的未來技術藍圖。就2納米工藝而言,其使用的是繼7納米、5納米、3納米之后的第四代EUV光刻技術,且14?就在其延長線上。

但是,據預測,在14?以后,將不再使用NA=0.33的EUV,而是采用NA=0.55的High NA EUV光刻。Imec和ASML已經合作在荷蘭設立“imec-ASML Joint High NA EUV Research Laboratory”,由ASML在2023年導入High NA試做一號機。就EUV專用涂覆顯影設備(coater developer,即clean truck)而言,已經決定由獨霸市場的東京電子來提供。

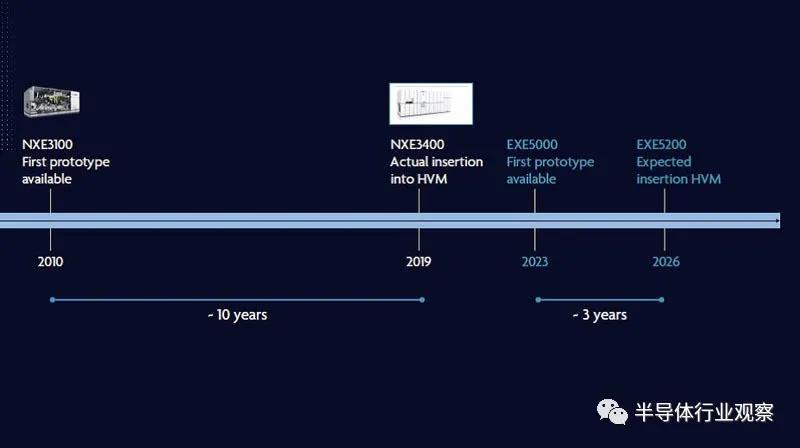

ASML在2010年出貨了用于首代量產技術研發的EUV曝光設備一一“XE:3100”,十年后,量產設備“NXE:3400”被用于邏輯半導體的量產產線。就High NA EUV曝光設備而言,目標是在2023年出貨試做設備(EXE:5000),在三年后的2026年導入量產產線,技術人員正在imec-ASML的合作研究所里集中推進研發。

圖5:ASML 的EUV曝光設備技術藍圖。

(圖片出自:mynavi)

通過微縮化和3D封裝,進一步實現集成化

通過將原本平鋪的晶體管垂直堆疊,就可以使集成電路的晶體管數量增多,這是一個方向;此外,通過采用3D封裝技術(堆疊半導體芯片或者晶圓),來進一步增加晶體管數量的研發也在如火如荼地進行。TSMC在日本成立3DIC研究中心的目的似乎也在于此。

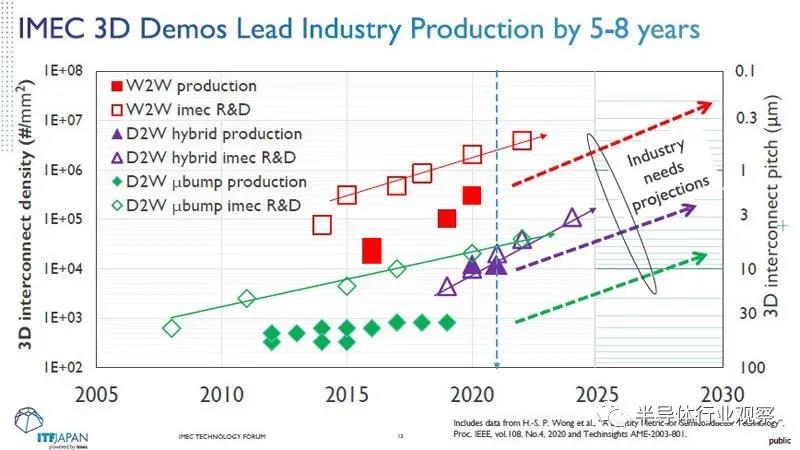

就imec而言,其研發水平遠遠領先于業界5一一8年的時間,其目標是先于業界實現某些技術,而且這些研究大部分是與合作伙伴共同合作的。

圖6:半導體企業的3D Interconnect密度、imec的推移表、未來的預測。(圖片出自:mynavi)

開始涉足降低生產半導體時的環境負荷項目

此外,imec在ITF Japan 2021上 做了新的研究主題一一《可持續發展的半導體技術、系統(Sustainable Semiconductor Technology and Science: SSTS項目)》。

在這個項目中,預測了生產半導體芯片時對環境造成的影響(電能消耗、化學藥品、材料、超純水、氣體等其他消耗),通過詳細分析碳足跡(Carbon Footprint,指的是一個人或者團體的“碳耗用量”),力求實現降低生產IC時的環境負荷。很期待半導體廠家(如生產設備廠家、材料廠家、晶圓代工廠)等企業共同加入研發,最近Apple(既是半導體Fabless、也是半導體客戶)也加入了研發,作為一項可以響應全球“碳中和(Carbon Neutral)”目標的活動,而被業界所熟知。

即,imec希望通過以上措施,以支持全球半導體供應鏈削減 “碳足跡”。