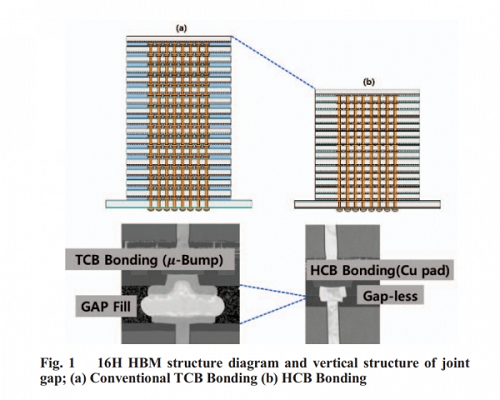

6月11日消息,據韓國媒體Thelec報道,三星上個月在2024年IEEE上發(fā)表的一篇題為《用于HBM堆疊的D2W(芯粒到芯片)銅鍵合技術研究》的論文,提到16層及以上的高帶寬內存(HBM)必須采用混合鍵合技術(Hybrid bonding)。

據了解,混合鍵合是下一代封裝技術,目的是芯片透過硅穿孔(TSV)或微型銅線進行垂直堆疊時,中間沒有凸點。韓媒The Elec指出,由于是直接堆疊,所以混合鍵合也稱為“直接鍵合”。

與目前三星所使用的熱壓焊接(TC)相比,Hybrid bonding可焊接更多芯片堆疊,維持更低的堆疊高度并提高熱排放效率。三星指出,降低高度是采用混合鍵合的主因,內存高度限制在775微米內,在這高度中須封裝17個芯片(即一個基底芯片和16個核心芯片),因此縮小芯片間的間隙,是內存大廠必須克服的問題。

最開始DRAM大廠計劃盡可能減少核心芯片的厚度,或者減少凸點間距,但除混合鍵合外,這兩種方法都已達極限。知情人士透露,很難將核心芯片做得比30微米更薄。由于凸點具有體積,通過凸塊連接芯片會有一定局限性。

三星4月使用子公司Semes的混合鍵合設備制作了16層的HBM樣品,并表示芯片運作正常。目前貝思半導體(BESI)和韓華精密機械(Hanwha Precision Machinery)也在開發(fā)混合鍵合設備。傳聞三星計劃在2025年制造出16層堆疊的HBM4樣品,并于2026年量產。

本站內容除特別聲明的原創(chuàng)文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創(chuàng)文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。