引 言

自適應濾波器一直是信號處理領域的研究熱點之一,經過多年的發展,已經被廣泛應用于數字通信、回聲消除、圖像處理等領域。自適應濾波算法的研究始于20世紀50年代末,Widrow和Hoff等人最早提出最小均方算法(LMS)。算法由于結構簡單,計算量小,易于實時處理,因此在噪聲抵消,譜線增強,系統識別等方面得到了廣泛的應用。為了克服定步長LMS算法中收斂速度、收斂精度及跟蹤速度等對步長大小選取相互矛盾的缺點,人們提出了許多變步長LMS算法,但是,當輸入信號具有強相關性時,例如語音信號,LMS算法及NLMS算法的收斂速度將急劇下降。因此,本文對進入自適應濾波器的輸入信號首先進行解相關預處理,再對自適應濾波器進行歸一化LMS。

很多自適應濾波器是在通用DSP處理器上通過編寫軟件代碼實現。這種濾波器在系統實時性要求不高的情況下,能很好地滿足濾波要求,但在實時性要求較高的場合(如3G移動通信,網絡會議等),這種濾波器在處理速度和抗干擾性能等方面已不能滿足要求。而用FPGA硬件實現的數字濾波器就能很好的解決并行性和速度問題,而且其具有靈活的可配置特性和優良的抗干擾能力,因而自適應濾波器的FPGA實現成為近年來數字濾波器中研究的熱點。Altera公司開發的DSP Builder可以完成FPGA的DSP系統設計,它結合Matlab/Simulink提供的庫元件和強大的計算仿真能力,進行圖形建模和仿真,還可以完成從Simulink模塊文件向VHDL語言的自動轉換。

1 算法概述

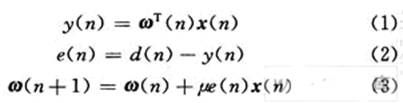

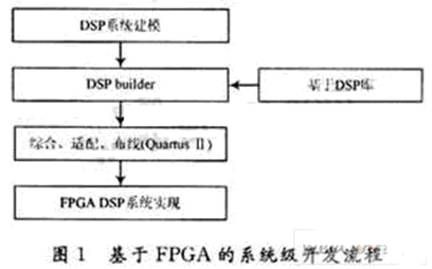

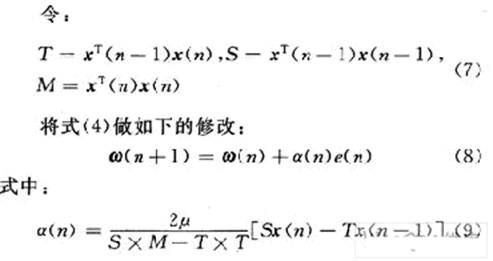

在標準LMS算法中,其迭代公式如下:

式中:ω(n)為自適應濾波器在時刻n的權矢量;x(n)為時刻n的輸入信號矢量;d(n)為參考信號;e(n)是誤差信號;μ是步長迭代因子,為了增加LMS算法的收斂速度,文獻[1-4]提出了不同的變步長算法代替定步長因子μ,但是很多變步長因子的計算量大,存在開方和指數運算,故在能滿足要求的情況下,歸一化LMS (NLMS)依然是一個很好的選擇,即用μn/[xT(n)x(n)]代替定步長因子μ為了控制失調,在更新公式中引入一個固定的收斂因子μn,這是因為所有的倒數都是基于平方誤差的瞬時值而不是均方誤差(MSE)。對于NLMS算法,當輸入信號具有強相關性時,LMS算法及NLMS算法的收斂速度將急劇下降。因此對進入自適應濾波器的輸入信號首先進行解相關預處理,再對自適應濾波器進行歸一化LMS,便得解相關歸一化LMS(DNLMS)即用式(4)代替式(3):

2 基于FPGA的系統開發流程

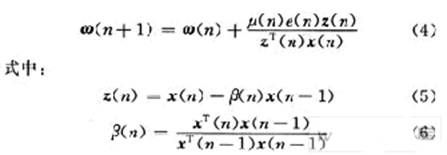

在早期PFGA的DSP系統設計過程中,DSP開發者直接使用VHDL或Verilog HDL語音進行開發。這種開發難度較大,開發效率較低,為了克服這些問題,出現了許多新的基于FPGA的DSP開發工具,如Altera公司的DSP Builder、Xilinx公司的System Generator等。圖1是Altera公司的FPGA系統級開發流程。

DSP Builder是Altera公司推出的一個面向DSP開發的系統級工具。它是作為Matlab/Simuli-nk的一個工具箱出現的。它從利用Matlab建立DSP電路模型開始。電路模型可方便地利用Simulink與DSPBuilder中提供的功能模塊和IP核進行設計。電路中的功能模塊和IP的技術參數、數據格式、數據類型和總線寬度等都能直接設置。電路模型建立后就能進行系統級的仿真。仿真通過后可以運行Signal Compiler,將模型轉化成RTL級的VHDL代碼和Tcl(工具命令語言)腳本語言。調用QuartusⅡ進行編譯,QuartusⅡ根據網表文件及設置的優化約束條件進行布線布局和優化設計的適配,最后生成編程文件和仿真文件。

3 系統建模與仿真

根據DNLMS算法的思想,結合FPGA硬件設計的特點。

NLMS算法主要包括延時模塊,乘法模塊,加法模塊,除法模塊等。為了讓整個系統看起來清晰,降低原理圖的復雜性,也便于多次應用,本文將幾個多次使用的模塊封裝成子模塊。下面將對各個子模塊作簡單的介紹。

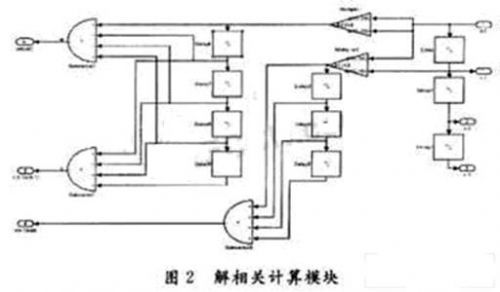

根據算法的要求,每次新的數據x(n)輸入,數據T,S,M都需要重新更新一次,計算量大,消耗的乘法塊多。為了解決這個問題。根據T,S,M的運算特點,每次更新只需要一個乘法塊和一次加法,就能完成8次乘法和一次加法的運算。具體子模塊如圖2所示。

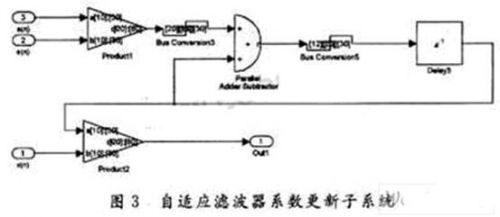

通過圖2的優化,對于8階濾波器,乘法塊的使用從24個減少到2個,計算速度將得到很大的提高。ω的迭代運算通過圖3實現。

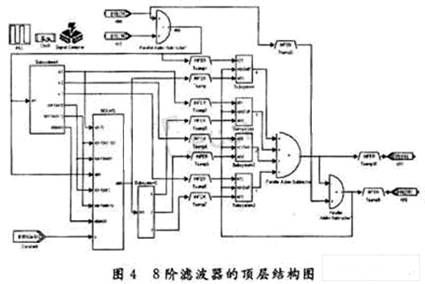

在頂層模塊的設計中,加入了PLL模塊和SignalComplier,根據各模塊仿真周期,在PLL模塊中設置好不同的周期,利用Simulink中的顏色標識采樣頻率的高低。頂層文件的設計如圖4所示。

在頂層結構圖中,子模塊8為方程(9)的實現過程。

4 計算機仿真

為了充分模擬相關性較強的信號,在輸入端加如下的信號源:

x(n)=0.99x(n-1)+v(n)

式中:v(n)為高斯白噪聲;x(n)的初始值為500,具體的產生電路如圖5所示。

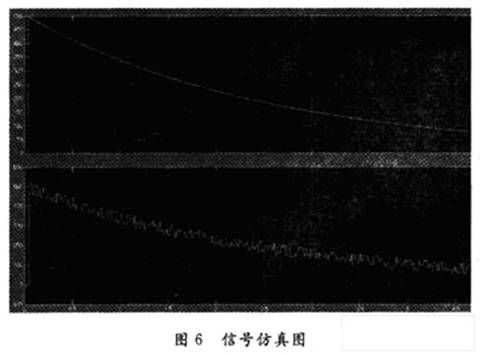

信號產生波形以及加噪后的仿真波形如圖6所示。

通過濾波器濾波的結果如圖7所示。

在圖7的信號依次為參考信號、加噪聲信號、誤差信號和濾波信號。濾波效果良好,對于強相關的信號,也有很好的濾波效果。通過QuartusⅡ編譯,濾器器的速度為35.24 MHz,編譯后生產如圖8所示的塊,它作為一個符號模塊可供更高級系統設計時調用,通過對該塊的修改和增加濾波器的階數,可以實現對語音的回聲消除。

5 結 語

自適應濾波器的研究是近年來研究的熱門方向,在PFGA中實現高速的自適應濾波器的設計更是一個熱點,在此采用DSP Builder系統建模的方法,在FPGA中實現了歸一化LMS算法,實驗結果表明:用DSPBuilder設計的8階DNLMS算法比用底層的VHDL代碼設計效率更高,靈活性更大,速度更快。同樣比通用的DSP芯片設計的8階NLMS濾波器處理速度快了20多倍。如果將8階NLMS濾波器擴展到512階或者1 024階,可以很好地應用于自適應回聲消除等很多自適應濾波的領域。故有一定的參考價值。