摘要:現代測試領城中,經常需要信號發生器提供多種多樣的的測試信號去檢驗實際電路中存在的設計問題。傳統的信號發生器多采用模擬電路搭建。以正弦波信號發生器為例,結合DDS直接數字合成技術,基于FPGA設計其他外圍電路構成正弦波信號發生器。相比傳統的模擬信號發生器,該電路具有設計簡單,升級容易,波形穩定等特點。

關鍵詞:FPGA;DDS;正弦波信號發生器

O 引言

信號發生器是用來為各種電路提供測試信號的儀器,在工程應用和測試領域有著非常廣泛的應用。目前傳統的信號發生器是使用模擬電路或者專用芯片搭建而成,但是存在頻率不商,穩定性較差,且不易擴展和調試的缺陷;而采用DDS直接數字頻率合成技術設計的信號發生器,改變了以往的設計思路,在精度、靈活性上大大超越了模擬信號發生器。隨著可編程邏輯器件FPGA的迅速發展,基于FPGA控制的DDS信號發生器使得電路設計更加簡單,而且通過預留的端口可輕松進行二次開發。本文通過Altera公司的EPFl0K10LC84-4芯片,成功實現了正弦波信號發生器。

1 系統硬件結構

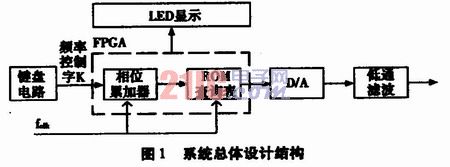

本系統由健盤電路、LED顯示、FPGA單元、D/A轉化和低通濾波器構成。以FPGA為主控制芯片,結合DDS直接數字頻率合成技術產生正弦波信號。系統總體設計結構見圖1。

1.1 鍵盤電路

在本系統中,通過鍵盤電路改變頻率控制字K,從而實現對正弦信號的頻率、相位的初始化設置。為了節省FPGA的I/O端口,簡化硬件線路,鍵盤電路采用4×4矩陣式健盤。鍵盤共設有14個鍵,其中包括4個功能健。具體鍵盤按鍵設置如表1。

使用時先通過“0~9”、“↑”、“↑”12個設置按鍵輸入所需信號頻率,再按下ENTER執行健,頻率控制字K將刷新,使得輸出信號頻率發生變化。CLR鍵用于將原有的設定值清零。

1.2 LED顯示

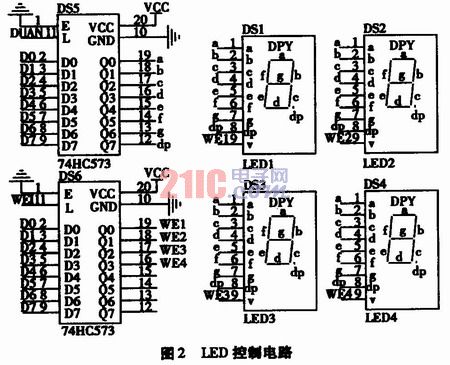

在本系統中,通過4個LED數碼管進行動態顯示。電路設計如圖2所示。LED數碼管動態顯示的實現方法為依次點亮各個數碼管,循環進行顯示,利用人眼的視覺暫留特性,數碼管每秒導通16次以上,可以達到4個數碼管同時顯示的效果。但是,延時也不是越小越好,因為數碼管達到一定亮度需要一定時間。如果延時控制不好則會出現閃動,或者亮度不夠。根據經驗,延時0.005秒可以達到滿意效果。

1.3 FPGA單元

FPGA單元包括鍵盤轉換頻率控制字、LED顯示控制、相位累加器、ROM查詢表的實現。鍵盤電路是一組按鍵開關的集合,FPGA掃描鍵盤電路的電平信號,通過FPGA中指定程序轉化為頻率控制字K輸入到相位累加器,同時,將設置輸出的頻率通過4個LED數碼管實時顯示。

相位累加器是DDS技術的核心,它類似一個計數器,由時鐘信號fclk上升沿觸發。頻率控制字K控制相位累加器的步長,每來一個上升沿,相位累加器上次的基數與頻率控制字K相加,得到新相位。新相位作為ROM查詢表的地址,相應的波形數據被讀取,經過D/A轉換輸出階梯波形。本文只將相位累加和ROM查詢表作為主要內容在軟件設計部分說明,具體內容見第3部分軟件設計。

1.4 D/A轉化

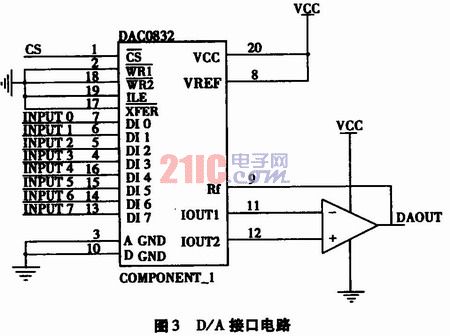

從FPGA輸出的正弦波信號還只是階梯信號,需要經過D/A轉化器進行數字/模擬信號的轉化。本設計使用的是8位D/A轉化芯片DAC083 2,該芯片采用CMOS/Si-Cr工藝實現。用倒T形電阻網絡轉換,為電流輸出型。DAC0832中有兩級鎖存器,第一級即輸入寄存器,第二級即DAC寄存器,數據輸入有直通數字輸入、雙緩沖輸入或單緩沖輸入三種工作方式。

D/A接口電路如圖3所示。

1.5 低通濾波電路

低通濾波器用于濾除階梯信號中的諧波分量。本文采用2階低通濾波電路,階梯信號通過低通濾波,使得輸出信號頻譜純度較好,失真較小。

2 系統關鍵技術

DDS(Direct Digital Synthesis)是一種應用直接數字合成技術來產生信號波形的方法。DDS技術建立在采樣定理的基礎上,它首先對需要的信號波形進行采樣、量化,然后存入存儲器作為待產生信號的數據查詢表。在輸出信號波形時,從數據表依次讀出數據,產生數字信號。

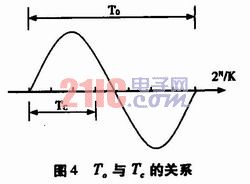

輸入時鐘頻率和輸出波形信號的頻率關系如圖4所示。在圖4中To表示輸出波形的周期,Tc為采樣周期,2N為ROM查詢表尋址范圍,K為頻率控制字。由圖可知To=Tc*2N/K,轉換為頻率可表示為fo=fc*K/2N,fc為時鐘信號clk的頻率。

在本設計中N=8,因此信號的輸出頻率fo=fc*K/256。

3 軟件設計

軟件設計主要是在FPGA中通過Verilog硬件語言進行相位累加器和ROM查詢表的編程實現,這兩部分采用Quartus軟件和Matlab軟件并行開發。

3.1 相位累加器的實現

相位累加器主要用于產生ROM查詢表所需的地址信息。圖5為在Quartus軟件中編程生成的相位累加器符號,相位累加器的輸入信號包括時鐘信號clk、復位信號clr和頻率控制字K。輸出信號addr[7…0]為ROM查詢表的輸入地址信號。

相位累加器類似一個計數器。首先,軟件設置相位累加器的基數為0,并通過時鐘信號clk上升沿觸發,基數與頻率控制字K相加,相加后的值反饋到相位累加器的輸入端作為下一次的基數。當相位累加器的溢出時,—個完整的階梯正弦信號就從ROM查詢表的輸出端輸出。因此,相位累加器的溢出率就是正弦波信號的輸出頻率。相位累加器的仿真波形如圖6所示。

3.2 ROM查詢表的實現

本文設計的ROM查詢表尋址范圍為256,數據為8bit。ROM查詢表如圖7所示,輸出q[7…O]需與D/A轉換器的輸入相連。ROM查詢表的輸出為8位,因此與D/A轉換芯片的分辨率相匹配。

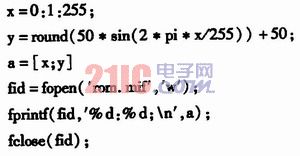

ROM查詢表的設計有很多種方法。定制ROM查詢表需要在軟件Quartus中載入.mif或.hex文件,這兩種文件可由多種工具獲得,如Quart-us的Text File編輯器、Matlab、DSP Builder、vc++編譯器、Keil編譯器等工具。本文選用Matab得到正弦波數字幅度值的.mif文件。Matl-ab程序如下:

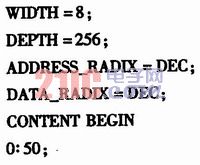

由于此時生成的.mif文件不符合Quartus中所需載入的.mif格式,還需要對其進行修改。修改格式如下:

最后通過載入此.mif文件,就可獲得如圖7所示的ROM查詢表。

4 系統測試

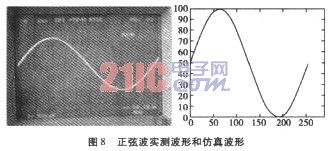

硬件調試完成后,我們對系統的整體功能進行了測試,并且與Matlab的仿真結果進行了比較。用示波器觀測試驗波形如圖8所示。系統的測試結果表明,輸出波形狀態良好,未出現明顯失真。

5 結束語

本文介紹的這種基于FPGA的DDS正弦波信號發生器,具有電路結構簡單、工作頻率穩定度高、頻率調整精度高等特點。并且,此方法同樣適用于三角波、方波等其他任意波形的實現。若要產生某特定波形,只需先用地Matlab對波形曲線采樣生成相應的.mif文件,然后載入ROM查詢表中,其他硬件不變即可產生所需信號。因此,該設計也可以直接拓展到其他測試領域的電路中。