0 引言

隨著科學技術的飛速發展,在軍事、航空航天和測試及測量等領域,人們對數據采集系統的采樣精度、采樣率和存儲量等指標提出了更高的要求。傳統的采集器件使用起來很不方便,其局限性非常明顯,顯然已經不能適應現代技術發展的需要。目前,隨著集成電路技術的進步,大規模和超大規模的可編程邏輯器件在實際系統設計中得到廣泛的應用。由于其集成度高、功耗低、設計靈活、效率高等優勢,同時器件具有用戶可編程特性,可大大縮短系統設計周期,減少設計費用,降低風險投入,而且部分器件還具有在線可編程的能力。

在此介紹一種雷達中/視頻數據采集記錄系統,它的核心技術是利用高速可編程邏輯門陣列FPGA對雷達目標回波進行高速實時采集,并將持續采集來的信號數據記錄在計算機硬盤上,以供后續數據處理需要。本系統的特點是:小型化,便于攜帶,連接方便,操作簡單,記錄時間長,采樣率高,數據傳輸率高,動態范圍大(12位A/D分辨率),并采用正交雙通道采集方式,完全符合高速大容量雷達信號采集記錄的需要。

1 系統組成與工作原理

系統主要由計算機和系統采集硬件組成,系統采集硬件由一塊帶有雙路高速A/D和USB接口電路的底板和一塊帶有FPGA的核心板組成。雷達數據采集記錄系統的工作流程如圖1所示。

系統以臺式PC作為采集主控設備,雷達中/視頻回波信號經A/D轉換器進行模數轉換,再由FPGA控制的核心采集模塊來完成數據的采集量化,采集模塊可以根據來自雷達系統的時鐘、同步觸發信號來控制對雷達回波信號的采集,然后將采集到的數據通過緩沖模塊送給USB,USB接口將數據打包傳送到臺式電腦的硬盤上以供顯示和處理使用。

FPGA與上位機間的數據交換是實現系統功能的重要一環。一方面,FPGA在完成對采集數據的抽取和緩沖后,采用高速的USB 2.0傳輸方式將數據實時地傳輸給上位機,使數據處理能夠順序進行;另一方面,數據采集模塊的某些參數由上位機控制面板設置后經總線傳送給FP-GA。

2 硬件電路板設計

在本系統中,FPGA核心板擔負著數據存儲,數據傳輸控制的任務,是本系統最為關鍵的部分,綜合考慮系統資源和FPGA價格,選擇Xi-linx公司的Spartan-Ⅱ系列XC2S200芯片較為適宜,由電源轉換芯片LT1764為FPGA提供穩定的電源電壓。其最小系統框圖如圖2所示。

XC2S200是推出的性價比更好的Spartan-Ⅱ系列FPGA產品中的一款,有著成熟的Virtex-E架構,內核電壓采用1.8 V,系統性能可達到200 MHz,系統門數為200 000系統門,內部包括適量的分塊RAM(Block-RAM)。該芯片支持豐富的接口標準。本系統采用ADI公司的AD9224為A/D轉換芯片,完成雙路A/D采樣功能。其采樣頻率為40 MHz,采用位數達12位,片內集成高性能的采樣保持放大器和參考電壓源,具有糾正錯誤輸出的邏輯功能,精確提供了在40 MSPS采樣率下12位的輸出數據,保證在完全可以運作的溫度范圍內無漏碼。

高速的數據采集速度是保證數據采集精度的標準,但往往在數據處理時并不需要以同樣的速度來進行,否則對硬件的需求太高,成本也較高。這里采用同步FIFO、SRAM、異步FIFO相結合的方法實現了對采集數據的緩沖處理。同時,由于數據的傳輸速度大于AD的采樣速度,保證了采集的數據在傳輸時無遺漏。

3 軟件設計

3.1 FPGA程序設計

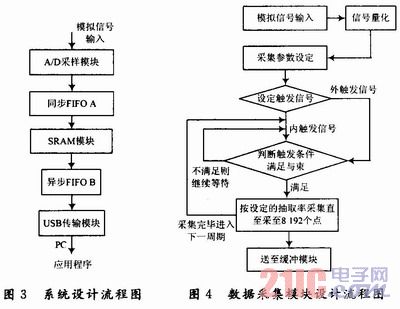

本系統采用了同步FIFO A、異步FIFO B和緩沖SRAM相結合的設計方法,共同構成本系統的數據緩沖模塊。整個系統的詳細設計流程如圖3所示。

3.1.1 數據采集模塊設計

雷達信號采集技術中,采集時序控制與實時數據傳輸是關鍵也是技術的難點所在。為保證采集的連續性,設計中采用了FPGA內部雙FIFO的緩沖技術、外置專用緩沖芯片技術與計算機公用緩沖區環行存儲技術。該模塊的詳細軟件設計流程如圖4所示。

3.1.2 數據緩沖模塊設計

數據緩沖模塊設計了同步FIFO A和異步FIFO B。其中FIFO A的一端接收A/D轉換數據,另一端將數據傳輸給外部SRAM;FIFO B的一端接收SRAM的數據,另一端將數據傳輸給USB單片機的FIFO。

3.1.3 測頻模塊設計

基于傳統測頻原理的頻率計的測量精度將隨被測信號頻率的下降而降低,在實用中有較大的局限性,而等精度頻率計不但具有較高的測量精度,而且在整個頻率區域能保持恒定的測量精度。綜合考慮,本系統采用等精度頻率計的測量方法。其基本流程圖如圖5所示。

3.1.4 測電壓模塊設計

采集信號經A/D變換器量化編碼以后,可以根據量化得到的結果進行信號幅度值的計算。同時考慮到采集到的信號尤其是正弦波、三角波等信號在測量時會發生抖動,所以在進行電壓測量時,采用了取平均值和對信號進行平滑處理相結合的方法提高測電壓的精度,設計實現對信號峰峰值、平均值的測量。

3.2 應用程序設計

在設計上,當USB驅動程序安裝好以后,應用程序調用線程獲取該設備的有效句柄,進而就可以與WDM進行通信。接口數據格式的定義我們采用結構數據包的形式,首先設計一個C語言的結構,把要進行通信的參數按照與VHDL語言相同的順序排列,然后在USB通信協議上,對這些參數進行數據包格式的設定。設計采集數據的存放問題時,我們調用線程把傳送來的數據數組按照“*.dat”的數據格式進行存儲,在回放顯示時,把數據從“*.dat”中讀到預定義的數組中進行調用,整個應用程序的設計流程如圖6所示。

設計虛擬儀器的主要工作就是編寫應用軟件,在此采用Visual C++進行了控制面板的設計。考慮到信號參數的設置把面板分為2大部分:采集參數設定部分和顯示控制部分,其中,前者的主要功能是把參數傳到硬件核心處理部分。而后者的主要功能是負責面板上NTGraph控件顯示參數的設置,應用程序控制及顯示面板如圖7所示。

4 系統調試和測試

在完成了系統的硬件設計和軟件設計以后,需要進行綜合調試和測試。通過調試,不斷優化程序代碼,對程序中的問題及時更正修改,使系統的性能得以提高,工作狀態更加穩定。測試的過程中可以修正電路中元器件的參數等,以免理論分析與實際狀態的差距引起系統的參數不符合要求。目前,本系統可以實現對多種型號的雷達進行實際外場數據采集。圖8,圖9分別為本系統采集到的某部岸基對海警戒雷達(全相參脈沖壓縮體制)的單路中頻(未經脈沖壓縮處理)和雙路正交視頻(經過脈沖壓縮處理)回波信號。

實驗表明該系統完全滿足所提出的指標要求,能夠做到大容量高速連續采集,而且穩定可靠,采集所得到的數據可以滿足信號處理和目標識別的要求。

5 結語

研究了雷達中/視頻數據采集與回放系統的總體方案,即由信號調理模塊、核心采集模塊、緩沖模塊、傳輸模塊和應用程序顯示模塊組成。FPGA與上位機間的數據交換通過USB 2.0接口實現,并運用虛擬技術,采用了Visual C++語言設計系統的計算機實時顯示界面。設計中運用硬件描述語言對FPGA進行編程,在完成了對輸入信號的采集和記錄的同時,實現了對輸入信號的防抖動、過零檢測、等精度測頻及電壓最值、峰峰值和平均值的測量,使得該系統能對信號參數進行準確測量。該系統被封裝于一個小型的屏蔽盒內,非常便于攜帶,可方便應用于外場雷達的數據采集。